前一篇文案介紹了LVDS,本篇介紹LVPECL(Low Voltage Positive Emitter Coupled Logi) 低壓正射極耦合邏輯, 源自發(fā)射極耦合邏輯(ECL),采用正電源。

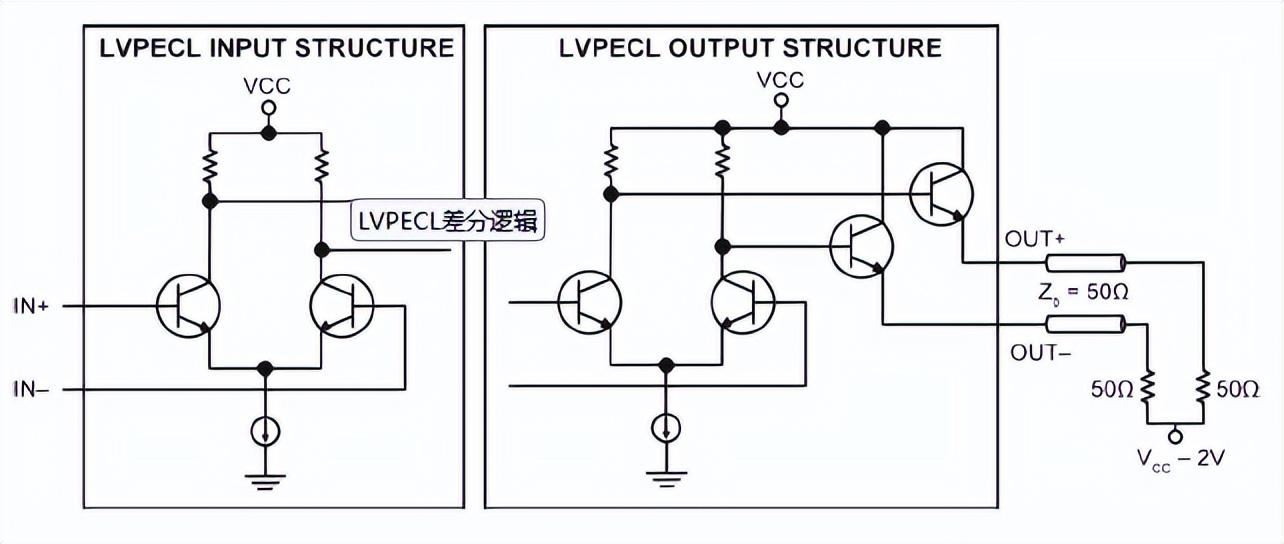

輸入是具有高輸入阻抗的電流開關(guān)差分對(duì)。

輸出由差分對(duì)放大器組成,驅(qū)動(dòng)一對(duì)射極跟隨器。如下:

缺點(diǎn)是功耗相對(duì)較高以及有時(shí)需要提供單獨(dú)的終接電壓軌

技術(shù)能實(shí)現(xiàn)超過10Gbps的高數(shù)據(jù)率。

LVPECL輸入與輸出端功能框圖

1.LVPECL內(nèi)部工作原理

LVPECL差分輸出端分別50Ω傳輸阻抗至Vcc-2V和輸出總線OUT + / OUT-輸出為中間電平為:Vcc-1.3V,導(dǎo)致近似的直流電流為14mA。

2.LVPECL端接匹配網(wǎng)絡(luò)

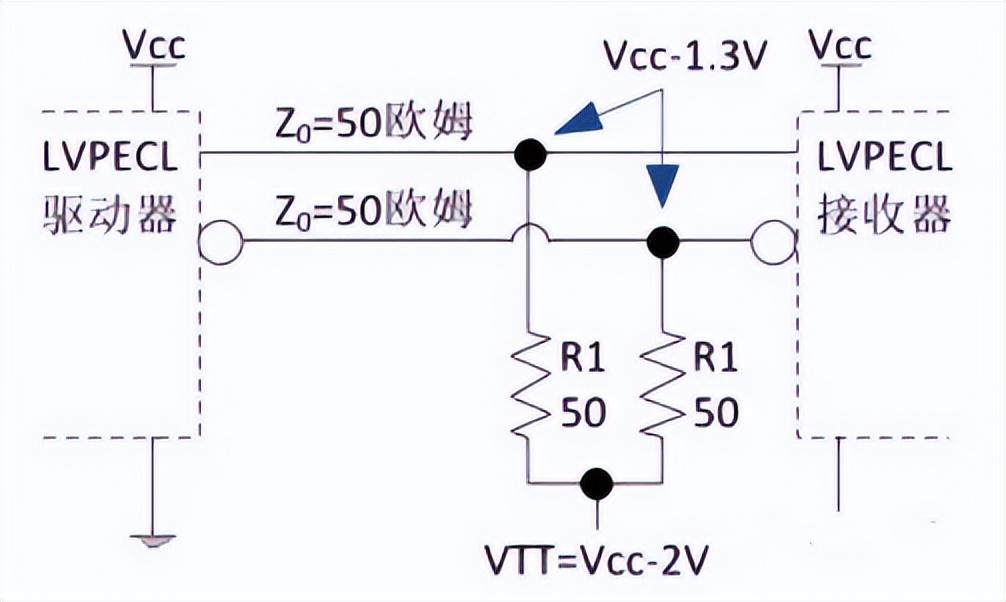

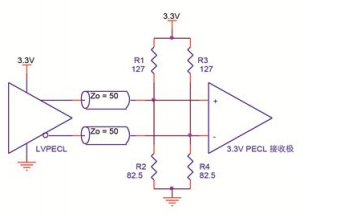

最簡單的LVPECL匹配方式就是在接收器的輸入側(cè)需要一個(gè)參考電壓:Vcc-2V,如下

典型配置方式

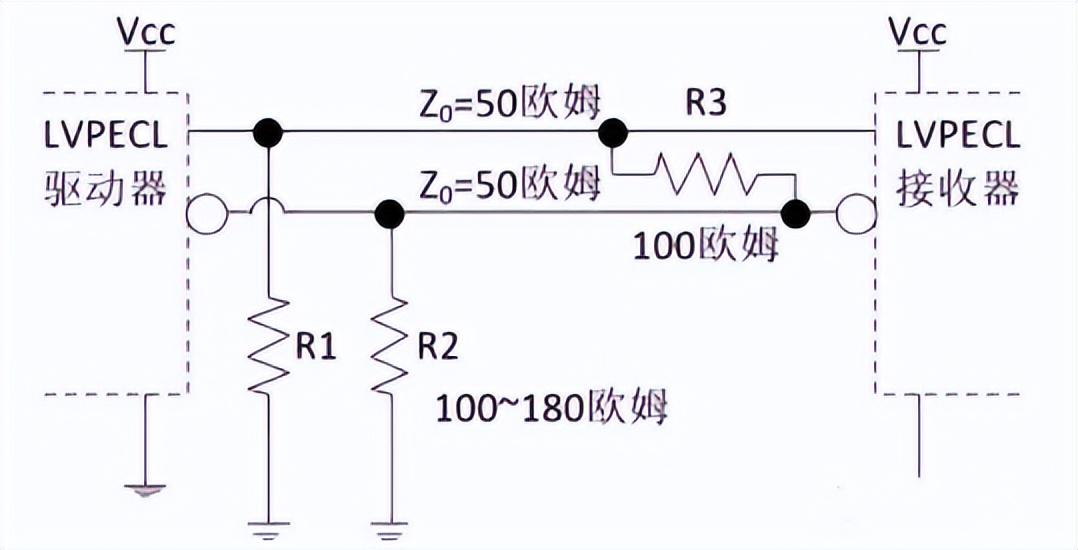

額外的電源需求會(huì)增加電路的復(fù)雜度和成本,本案介紹幾種常用端接方式(參見:淺談LVDS、CML、LVPECL三種差分邏輯電平之間的互連-電子發(fā)燒友),如下為推薦:

直流耦合三電阻方式

R1=140~200歐姆(Vcc:3.3V),R1=270~330歐姆(Vcc: 5V),R2=100歐姆。R1為輸出門提供偏置電流,R2為交流信號(hào)提供匹配。輸入門的直流電平偏置直接利用輸出門的直流電平(Vcc-1.3V),并不需要外來的上下拉電阻來提供。R2一個(gè)電阻必須放在離輸入門比較近的地方,R1放置的地方可以比較隨便。

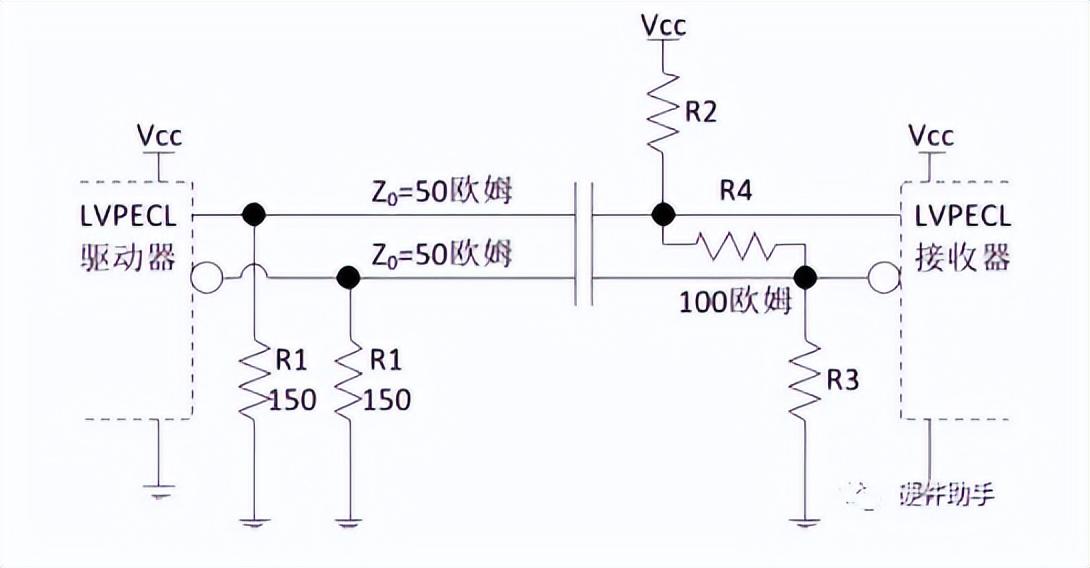

交流耦合

R1=140~200歐姆,屬于直流偏置電阻。C1為耦合電容,可以放在線上的任何一個(gè)地方。R4=100歐姆,屬于交流匹配電阻,一定要放在末端。R2、R3為K級(jí)別的電阻,必須滿足R3/(R2+R3)=(VCC-1.3V)/VCC的比值就可以了,這兩個(gè)電阻是為輸入端提供直流電平,所以對(duì)PCB上的位置沒有特殊要求。

-

放大器

+關(guān)注

關(guān)注

143文章

13548瀏覽量

213104 -

lvds

+關(guān)注

關(guān)注

2文章

1036瀏覽量

65703 -

射極跟隨器

+關(guān)注

關(guān)注

1文章

54瀏覽量

15152 -

LVPECL

+關(guān)注

關(guān)注

2文章

27瀏覽量

17917 -

耦合電容

+關(guān)注

關(guān)注

2文章

154瀏覽量

19789

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

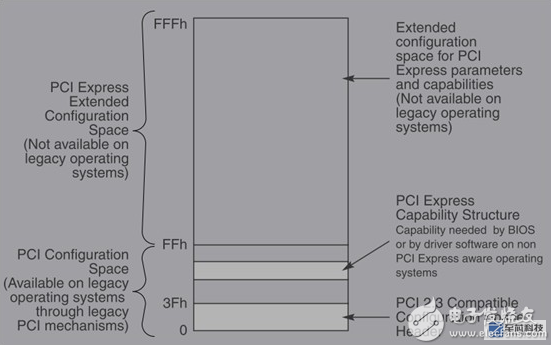

簡談PCIe的軟件配置方式

LVDS、CML、LVPECL不同邏輯電平之間的互連(二)

LMK00725是否支持LVDS或者LVPECL的差分交流耦合輸入呢?

LVPECL驅(qū)動(dòng)器終端設(shè)計(jì)介紹

如何將Virtex 5 LVPECL_25連接到另一個(gè)設(shè)備的3.3v lvpecl?

如何使用BLVDS或其他驅(qū)動(dòng)Kintex LVPECL輸入的方法的信息?

如果ad9680的clk和sysref信號(hào)采用lvpecl格式輸入,交流耦合的話前端網(wǎng)絡(luò)如何設(shè)計(jì)?

AD級(jí)聯(lián)的工作方式配置和AD雙排序的工作方式配置詳細(xì)說明

智能硬件產(chǎn)品有哪些_智能硬件網(wǎng)絡(luò)配置方式

設(shè)計(jì)LVPECL終端需要考慮那些原因

LVPECL配置方式介紹

LVPECL配置方式介紹

評(píng)論