介紹

計算高速鏈路? (CXL?) 可滿足處理器不斷增長的內存帶寬和容量需求,以加速高速計算應用,例如人工智能、云計算和機器學習。該行業正在迅速過渡,以利用這種新協議支持的功能,而采用的快速途徑在很大程度上基于利用現有的PCI Express?(PCIe?)5.0物理層,電氣和基礎設施。

設計利用這一新興標準在特定區域限制內優化容量、性能和功耗的大型系統需要仔細選擇內存模塊外形尺寸,同時考慮:

支持高帶寬的接口

支持最佳容量的尺寸

通過允許適當的氣流來支持功耗

針對多源進行標準化

模塊化,可根據應用需求進行擴展

本文探討了其中的一些設計方面。

內存技術

基于 CXL 的應用程序具有多個優點,包括更高的性能,因為它允許共享內存資源、CPU 內存空間與連接設備上的內存之間的內存一致性以及降低軟件堆棧復雜性。以前,業界將無緩沖 DIMM (UDIMM) 和寄存器 DIMM (RDIMM) 用于內存應用。

UDIMM 通常用于低端服務器,并且最具成本效益,但由于命令/地址信號的高負載,它們不適合更高的速度。此外,它們每個通道最多只能支持兩個 DIMM (DPC)。RDIMM 在 DIMM 上有一個寄存器,用于緩沖 DIMM 上的每個 DRAM 和內存控制器之間的地址和命令信號。這不僅可以在 DIMM 上安裝更多的 DRAM,還可以提高模塊的信號完整性,使其適合 CXL 運行的速度。所有這些因素使 RDIMM 外形尺寸的內存模塊非常適合 CXL 應用。例如,標準 RDIMM 可以連接到主板上基于 CXL 的內存控制器,也可以插入 CXL 轉接卡。

盡管RDIMM模塊具有優勢,但隨著DRAM速度的不斷提高(DDR5 *最大6400 MT/s),每個通道的引腳數量仍然相當大(DDR380為5引腳)。差分 DIMM (DDIMM) 是一種較新的內存模塊外形,引腳數明顯減少(84 個引腳),可實現 25.6GB/s 的數據吞吐率,延遲為 40ns,密度高達 256GB,允許 CPU 點對點連接到加速器和 I/O 設備。在減少引腳數的同時提高支持的數據速率,對于標準服務器環境中基于 CXL 的應用程序非常有益。

CXL 外形規格

隨著接口速度的提高,設計背板面臨一些挑戰,例如:為驅動器和連接器選擇合適的外形尺寸,以支持帶寬要求、滿足信號完整性需求、利用現有設計、滿足功率預算并有助于改善氣流。

企業和數據中心 SSD 外形 (EDSSF) 是 NVM Express? (NVMe?) SSD 的另一種現有外形,支持嵌入式機箱更換,需要更小的連接器,允許從 PCIe 將背板設計用于 1U 和 2U 服務器,并顯著減少 2U 氣流需求,從而降低冷卻成本。

EDSSF 針對特定類型的終端應用提供了幾個選項:

E1.S 外形小巧,支持 5.9 毫米至 25 毫米之間的厚度,是超大規模和企業級計算節點和存儲的理想選擇,與傳統 SSD 外形相比,可容納更多 NAND 封裝,以增加每個驅動器的容量。

E1.L 是一種外形規格,旨在最大限度地提高存儲陣列(JBOD、JBOF)中每個驅動器和每個機架單元的容量,與傳統外形規格(如專為旋轉介質設計的 U.2)相比,具有卓越的可管理性、可維護性和散熱特性。它支持 x4 或 x8 通道的 PCIe,最大厚度為 18 毫米。

E3 外形規格以 E3 的形式提供多種長度和高度選項。S 和 E3。L 表示 2U 垂直方向或 1U 水平方向。它們支持熱插拔,熱插拔的厚度從 7.5 毫米到 18 毫米不等,以最大限度地提高每個系統的驅動器,并支持 x4、x8 或 x16 PCIe 主機接口。

在背板上選擇合適的連接器以支持 CXL 的速度也非常重要。Mini Cool Edge IO 連接器 (MCIO) 是下一代連接器類型,支持 0.60mm 間距連接器,采用纖薄外形設計,能夠傳輸高達 56Gb/s 的高速信號。它被廣泛采用為服務器中 PCIe Gen 5 內部布線的首選連接器,因為與傳統的 PCB 布線方法相比,它允許更大的信號路徑長度,同時保持 SI 性能。它具有成本效益、高度模塊化、可擴展且極易維修,使其成為 CXL 應用的不錯選擇。

結論

為了設計需要內存池和擴展的 CXL 系統,可以使用幾種現有的內存模塊外形規格,其中包括滿足帶寬和容量需求的 RDIMM 和 DDIMM。使用的內存模塊外形類型應基于最終應用的性能需求、延遲、負載和空間限制。

最后,為驅動器選擇 EDSSF 外形尺寸以及用于背板的 MCIO 連接器將有助于利用現有的 PCIe 基礎設施,并利用 CXL 的性能增強

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19178瀏覽量

229201 -

人工智能

+關注

關注

1791文章

46896瀏覽量

237670 -

機器學習

+關注

關注

66文章

8382瀏覽量

132444

發布評論請先 登錄

相關推薦

FPGA的高速接口應用注意事項

高速電路中過孔設計注意事項

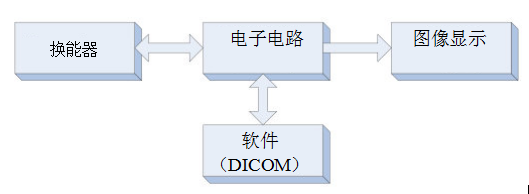

超聲系統信號鏈的設計注意事項

膽機使用的注意事項

超聲系統的信號鏈設計注意事項

計算高速鏈路的系統注意事項

計算高速鏈路的系統注意事項

評論