常用電路模塊的布局布線原則

常用存儲(chǔ)器設(shè)計(jì)

*FLASH

*DDR

*DDR2

*DDR3

*QDR

1、FLASH的設(shè)計(jì)

FLASH(閃速存儲(chǔ)器)-速率較低

布局:一般采用菊花鏈

BGA->SDRAM->FLASH

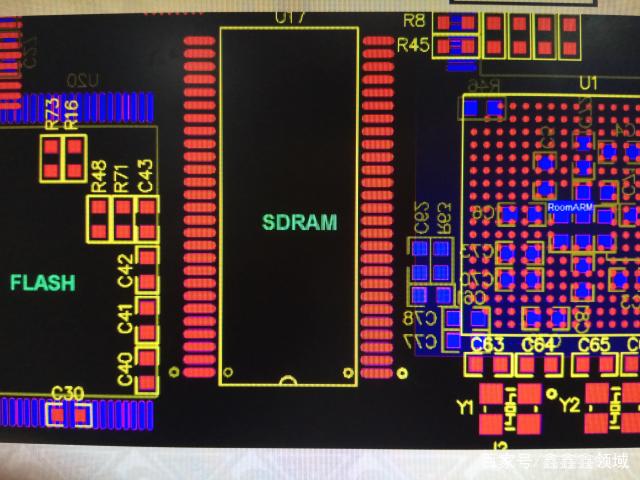

(FLASH和SDRAM推薦距離為500~1000MIL),如下圖:

2、FLASH的設(shè)計(jì)

布線(如圖)

3W原則

等長(zhǎng)范圍:+-100MIL

特性阻抗:50歐

3、DDR的設(shè)計(jì)

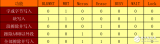

管腳定義解釋?zhuān)ㄈ缦聢D)

4、DDR的布局

布局原則:靠近CPU擺放

DDR X1片時(shí),采用點(diǎn)對(duì)點(diǎn)的布局方式,

DDR到CPU的推薦的中心距離:

當(dāng)中間無(wú)排阻時(shí):900~1000MIL;

當(dāng)中間有排阻時(shí):1000~1300MIL。

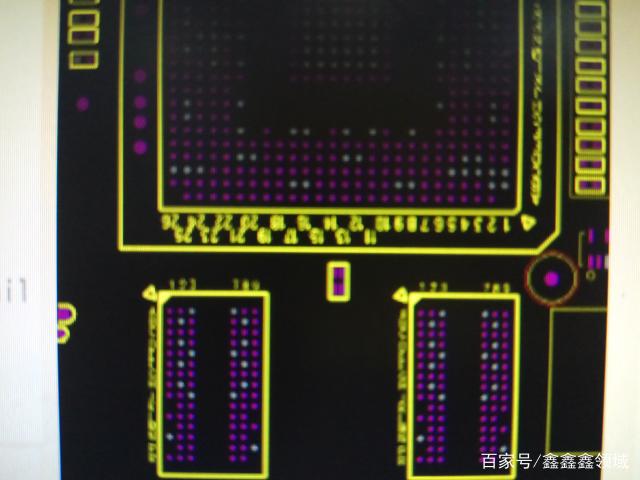

DDR X2片時(shí),相對(duì)于CPU嚴(yán)格對(duì)稱(chēng),如下圖:

5、DDR的保護(hù)區(qū)域

DDR2保護(hù)區(qū)域(KEEPOUT REGION):DDR2內(nèi)存組,所有同DDR相關(guān)的阻容電路,一直向CPU方向延伸至CPU的DDR控制器,稱(chēng)為DDR保護(hù)區(qū)域(DDR KEEPOUT REGION)。這個(gè)區(qū)域里需要滿(mǎn)足一下條件:

A)不得出現(xiàn)與DDR無(wú)關(guān)的信號(hào);

B)必須提供完整的地平面(信號(hào)線下方地平面不得中斷);

C)必須提供完整的VCC_1V8電源平面(信號(hào)線下方電源平面不得中斷)。

如下圖:

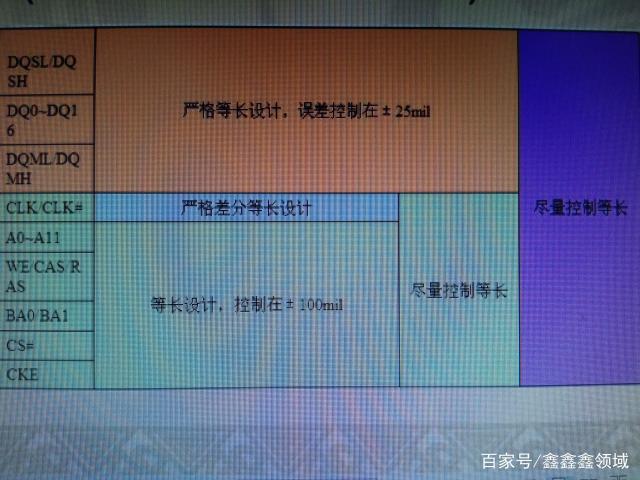

6、DDR的布線

特性阻抗:?jiǎn)味?0歐,差分100歐;

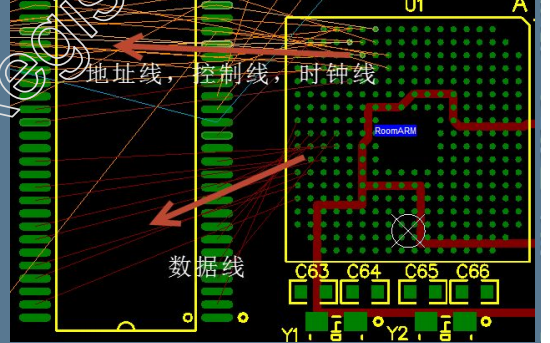

數(shù)據(jù)線每10根盡量走在同一層;

信號(hào)線的間距滿(mǎn)足3W原則

數(shù)據(jù)線、地址(控制)線、時(shí)鐘線之間的距離保持20MIL以上或者至少3W

完整的參考平面

VREF電源走線推薦>=20~30mil

誤差范圍:

差分對(duì)誤差嚴(yán)格控制在5MIL;

數(shù)據(jù)線誤差范圍控制在+/-25MIL;

地址線誤差范圍控制在+/-100MIL;

7、DDR的時(shí)序設(shè)計(jì)

DDR(采用樹(shù)形或者星形拓?fù)洌┤缦聢D:

-

SDRAM

+關(guān)注

關(guān)注

7文章

422瀏覽量

55159 -

FlaSh

+關(guān)注

關(guān)注

10文章

1621瀏覽量

147754 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7452瀏覽量

163606 -

DDR

+關(guān)注

關(guān)注

11文章

711瀏覽量

65230 -

Vcc

+關(guān)注

關(guān)注

2文章

305瀏覽量

35854

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

求助 數(shù)據(jù)存儲(chǔ)器 FLASH程序存儲(chǔ)器 FLASH數(shù)據(jù)存儲(chǔ)器的區(qū)別

未來(lái)DDR4、NAND Flash存儲(chǔ)器芯片該如何發(fā)展

單板硬件設(shè)計(jì):存儲(chǔ)器( NAND FLASH)

基于ColdFire MCF5249的Flash存儲(chǔ)器擴(kuò)展技

Flash存儲(chǔ)器的內(nèi)建自測(cè)試設(shè)計(jì)

Flash存儲(chǔ)器概述

flash存儲(chǔ)器的類(lèi)型

flash存儲(chǔ)器的讀寫(xiě)原理及次數(shù)

DRAM、NAND FLASH、NOR FLASH三大存儲(chǔ)器分析

介紹DRAM、FLASH和DDR技術(shù)分析和對(duì)比

PCB的常用存儲(chǔ)器設(shè)計(jì)的詳細(xì)資料說(shuō)明

硬件設(shè)計(jì)案例分析之常用存儲(chǔ)器FLASH與DDR的設(shè)計(jì)

硬件設(shè)計(jì)案例分析之常用存儲(chǔ)器FLASH與DDR的設(shè)計(jì)

評(píng)論