來源:半導體芯科技編譯

Imec的虛擬工廠支持減少光刻和蝕刻工藝步驟的碳足跡的戰略

在最近舉行的2023 Advanced Lithography + Patterning Conference會議上,Imec提出了對先進集成電路制造中圖案的環境影響的定量評估。在Imec.netzero建模平臺上開發了一個虛擬工廠。由此產生的分析使imec及其合作伙伴能夠評估當前的制造選擇,確定重點領域,并預測未來。在imec的物理工廠中,對影響較大的領域探索了環保的工藝解決方案,其中包括減少氟化蝕刻氣體,最大限度地提高EUV掃描儀的產量,以及減少氫氣和水的消耗。

由于先進技術的復雜性日益增加以及晶圓生產總量的預計增長,預計未來十年與IC制造相關的二氧化碳排放量將翻兩番。為了應對這種情況,先進的半導體企業已承諾到 2030-2050 年實現碳中和或凈零排放。在此背景下,Imec啟動了可持續半導體技術和系統(SSTS)計劃,匯集供應鏈,共同實現芯片制造的凈零排放。SSTS的目標之一是為行業提供一種獨特的自下而上的方法,提供具有高粒度的可操作數據,從而在工藝和流程開發期間進行影響評估。

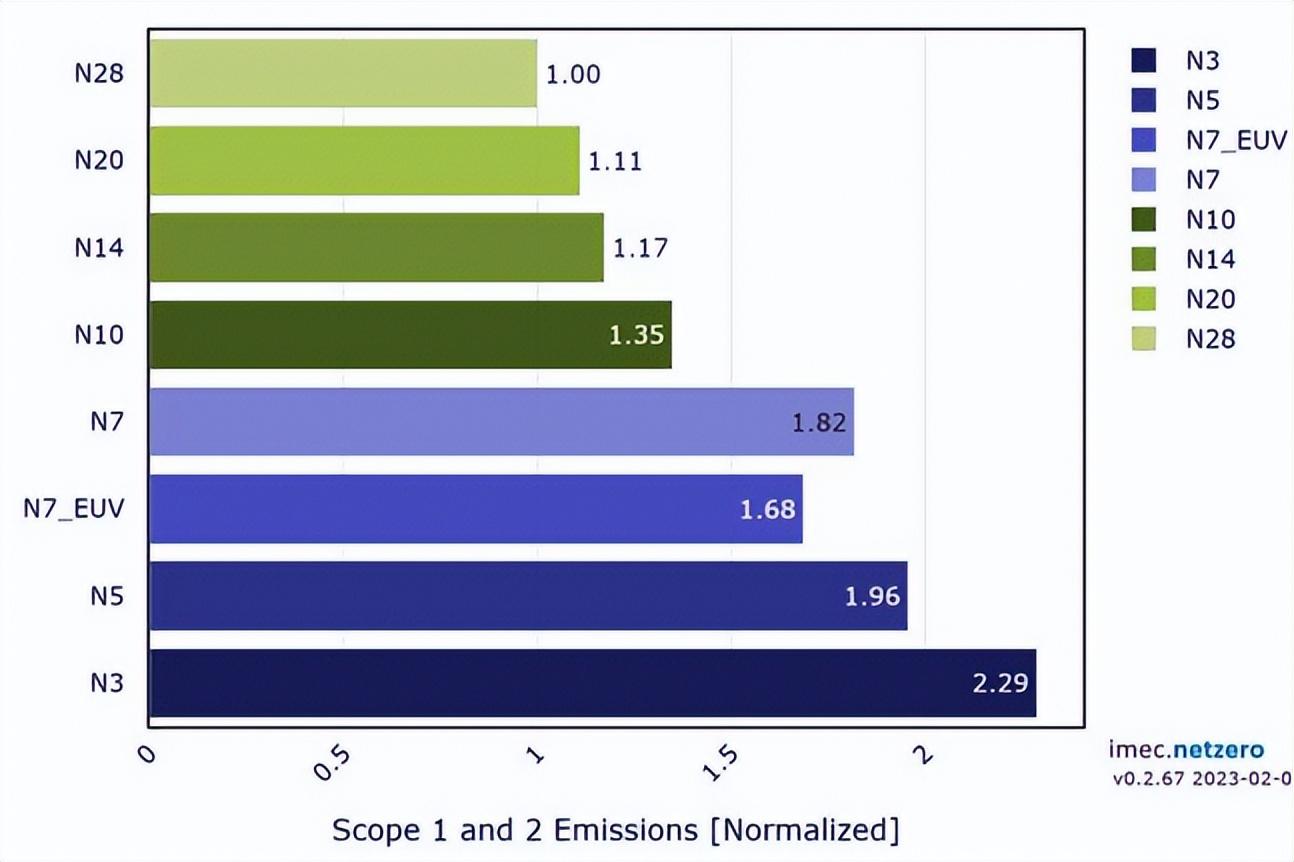

通過使用在SSTS計劃框架內開發的建模平臺Imec.netzero,Imec與其合作伙伴合作,首次量化了各種邏輯技術節點的圖案相關工藝步驟對環境的影響。“通過應用這種'虛擬晶圓廠'工具,我們證明了光刻和蝕刻共同承擔了與制造3納米邏輯晶圓相關的范圍1和范圍2排放(即分別來自自有或運營資產以及購買能源的排放)的45%。使用和不使用EUV圖案化的先進技術節點(我們的示例圖表中的N7)的比較也清楚地證明了EUV作為限制與復雜多圖案技術(10nm-7nm-5nm過渡)相關的CO2eq排放的解決方案的價值,“Imec技術團隊的主要成員Emily Gallagher解釋道。“此外,建模工具可以量化與實際晶圓廠實驗相關的收益。例如,將EUV劑量降低10%可為每個晶圓節省約0.4千克二氧化碳當量。這將導致大型晶圓廠每月節省約40噸二氧化碳當量,相當于從加利福尼亞州舊金山到俄勒岡州波特蘭的100個往返航班的排放量。

Imec利用其物理晶圓廠作為試點環境,探索高影響地區的工藝和設計方向。Emily Gallagher:“我們最近與我們的合作伙伴Edwards合作,在我們的300mm潔凈室中安裝了用于EUV光刻的氫氣回收系統,使我們能夠重復使用和回收~70%的氫氣。此外,我們越來越關注0.33NA和0.55NA(高NA)EUV光刻的低劑量解決方案,這一努力也有助于降低光刻成本。我們還確定了提高可持續性的蝕刻方向,目前側重于整體減少傳統氣體消耗。下一步,我們將與我們的合作伙伴一起量化這些擬議解決方案對整個半導體工藝流程的影響。”

Imec先進圖案、工藝和材料高級副總裁Steven Scheer表示:“過去開發的圖案化工藝步驟在很大程度上促進了半導體革命,要想跟上不斷提高的計算性能的需求,進一步的進步是必不可少的。在保持相同圖案化能力的同時制定減少二氧化碳排放的策略將是一項巨大的努力,為此我們現在已經達到了第一個里程碑。通過與設備和材料供應商的合作,Imec.netzero內開發的模型被不斷地進行基準測試和驗證。他們的作用對于推進我們的SSTS計劃以及促進實用的圖案化解決方案以減少全球半導體行業的碳足跡和環境影響至關重要。

“然而,我們注意到,并非所有環境影響都包含在碳當量排放指標中,”Steven Scheer補充道。“例如,氣體排放可能是有害空氣污染物(HAPS),光刻膠和增透膜(ARC)都可能含有PFAS(全氟和多氟烷基物質)。PFAS的碳-氟鍵強度有助于化學放大抗蝕劑(CAR)在成熟光學和不斷發展的EUV光刻膠中具有卓越的性能特征。然而,其生物蓄積潛力已導致社會對消除其使用的強烈興趣。除了直接降低碳排放的項目外,還必須考慮消除PFAS等項目。”

審核編輯:湯梓紅

-

集成電路

+關注

關注

5381文章

11389瀏覽量

360879 -

半導體

+關注

關注

334文章

27019瀏覽量

216349 -

晶圓

+關注

關注

52文章

4845瀏覽量

127804

發布評論請先 登錄

相關推薦

IBM發布《可持續發展準備工作狀態報告》

德力西電氣亮相大灣區EHS及可持續發展論壇

智慧城市在可持續發展中的應用

中興通訊發布2023年可持續發展報告

美光發布2024年可持續發展報告 促進平等與包容

隆基綠能發布2023年可持續發展報告 可持續發展融入戰略管理

4芯M5接頭環保與可持續發展

立訊精密首次被EcoVadis授予可持續發展銀牌

晶科能源受邀出席2024年亞洲可持續發展峰會

晶科能源獨家亮相Economists亞洲可持續發展峰會 促進可持續性增長

研華躋身可持續發展企業前列,首度入選標普全球可持續年鑒獲銀獎殊榮

英飛凌入選全球最具可持續發展能力的企業

虛擬晶圓工廠提供可持續發展的選擇

虛擬晶圓工廠提供可持續發展的選擇

評論