編者按:FPGA 架構(gòu)的新方法帶來(lái)了更細(xì)粒度的控制和更大的靈活性,以滿足機(jī)器學(xué)習(xí) (ML) 和人工智能 (AI) 的需求。這個(gè)由兩部分組成的系列的第 1 部分介紹了 Efinix 的一個(gè)這樣的架構(gòu),以及如何使用開(kāi)發(fā)板開(kāi)始使用它。第2部分討論開(kāi)發(fā)板與外部設(shè)備和外設(shè)(如相機(jī))的接口。

FPGA 在許多應(yīng)用中發(fā)揮著關(guān)鍵作用,從工業(yè)控制和安全到機(jī)器人、航空航天和汽車。由于可編程邏輯內(nèi)核的靈活性和廣泛的接口能力,F(xiàn)PGA 的一個(gè)不斷增長(zhǎng)的用例是在部署 ML 推理時(shí)的圖像處理。FPGA 非常適合實(shí)現(xiàn)具有多個(gè)高速攝像頭接口的解決方案。此外,F(xiàn)PGA 還支持在邏輯中實(shí)現(xiàn)專用處理流水線,從而消除與基于 CPU 或 GPU 的解決方案相關(guān)的瓶頸。

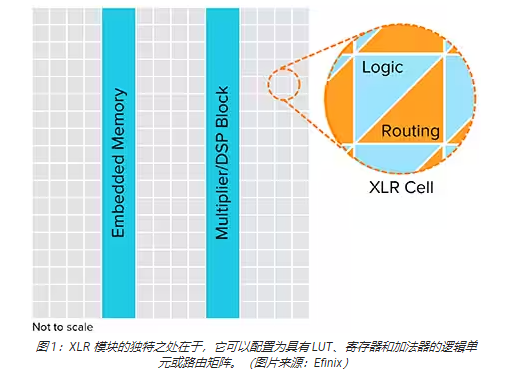

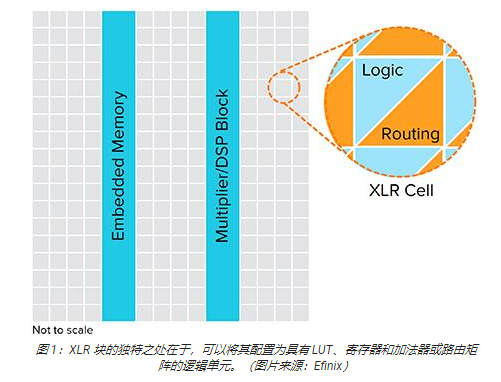

然而,對(duì)于許多開(kāi)發(fā)人員來(lái)說(shuō),他們的應(yīng)用需要更多的 ML/AI 功能以及更細(xì)粒度的控制或路由和邏輯,超出了具有組合邏輯塊 (CLB) 的經(jīng)典 FPGA 架構(gòu)所能提供的。FPGA架構(gòu)的新方法解決了這些問(wèn)題。例如,Efinix的Quantum架構(gòu)使用可互換邏輯和路由(XLR)模塊。

本文討論了Efinix FPGA架構(gòu)的主要特性和屬性,重點(diǎn)介紹了其AI/ML功能并介紹了實(shí)際實(shí)現(xiàn)。然后,本文討論了開(kāi)發(fā)人員可用于快速開(kāi)始下一個(gè) AI/ML 成像設(shè)計(jì)的開(kāi)發(fā)板和相關(guān)工具。

Efinix FPGA 器件

Efinix目前提供兩個(gè)設(shè)備系列。它最初推出了Trion系列,該系列提供從4000(4K)到120K邏輯元件(LE)的邏輯密度,并使用中芯國(guó)際40LL工藝制造。最新的器件系列鈦系列提供從35K到1萬(wàn)(1M)邏輯元件的邏輯密度,并在非常流行的臺(tái)積電16納米(nm)節(jié)點(diǎn)上制造。

這兩種產(chǎn)品都基于昆騰架構(gòu),這在FPGA世界中是獨(dú)一無(wú)二的。標(biāo)準(zhǔn)FPGA架構(gòu)基于CLB,在最簡(jiǎn)單的層面上,CLB包含一個(gè)查找表(LUT)和觸發(fā)器。CLB 實(shí)現(xiàn)邏輯方程,然后通過(guò)路由互連。Efinix的量子架構(gòu)通過(guò)XLR塊擺脫了不同的邏輯和路由塊。

XLR 模塊的獨(dú)特之處在于,它可以配置為具有 LUT、寄存器和加法器或路由矩陣的邏輯單元。此方法提供了一個(gè)更細(xì)粒度的體系結(jié)構(gòu),可提供路由靈活性,使邏輯繁重或路由繁重的實(shí)現(xiàn)能夠?qū)崿F(xiàn)所需的性能。

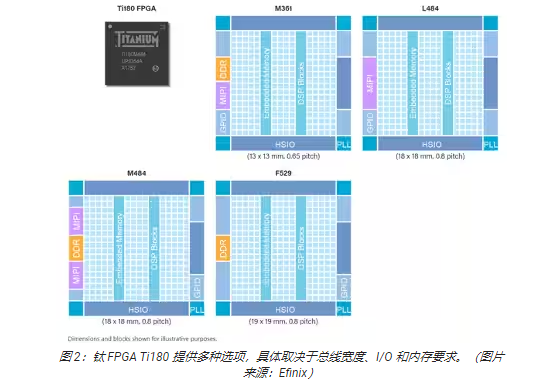

作為最新的產(chǎn)品系列,鈦金屬器件為開(kāi)發(fā)人員提供了最先進(jìn)的功能(圖 2)。與 XLR 內(nèi)核一起,它們提供多千兆位串行鏈路,其運(yùn)行速度為 16 Gbps 或 25.8 Gbps,具體取決于所選設(shè)備。這些千兆位鏈路對(duì)于實(shí)現(xiàn)片上和片外的高速數(shù)據(jù)傳輸至關(guān)重要。

鈦器件還提供廣泛的輸入/輸出 (I/O) 接口功能,可分為通用 I/O (GPIO),并且可以支持單端 I/O 標(biāo)準(zhǔn),例如 3.3 伏、2.5 伏和 1.8 伏的低壓 CMOS (LVCMOS)。

對(duì)于高速和差分接口,鈦金器件提供高速I/O (HSIO),支持單端I/O標(biāo)準(zhǔn),如1.2伏、1.5伏的LVCMOS,以及SSTL和HSTL。HSIO 支持的差分 I/O 標(biāo)準(zhǔn)包括低壓差分信號(hào) (LVDS)、差分 SSTL 和 HSTL。

現(xiàn)代FPGA還需要緊密耦合的高帶寬存儲(chǔ)器,用于存儲(chǔ)圖像處理應(yīng)用的圖像幀,信號(hào)處理的樣本數(shù)據(jù),當(dāng)然還有運(yùn)行FPGA中實(shí)現(xiàn)的處理器的操作系統(tǒng)和軟件。鈦合金系列器件能夠與動(dòng)態(tài)數(shù)據(jù)速率四(DDR4)和低功耗DDR4(x)(LPDDR4(x))接口。根據(jù)所選的確切鈦金設(shè)備,總線寬度支持為 x32 (J) 或 x16 (M),而某些設(shè)備不支持 LPDDR4 (L)。

鈦FPGA基于SRAM,需要配置存儲(chǔ)器,器件配置由主/從串行外設(shè)互連(SPI)或JTAG執(zhí)行。為了確保這種配置方法的安全,鈦FPGA使用比特流的AES GCM加密,以及AES GCM和RSA-4096來(lái)提供比特流身份驗(yàn)證。由于 FPGA 部署在惡意行為者可以訪問(wèn)和操縱其行為的邊緣,因此需要這樣的強(qiáng)大安全性。

開(kāi)發(fā)板介紹

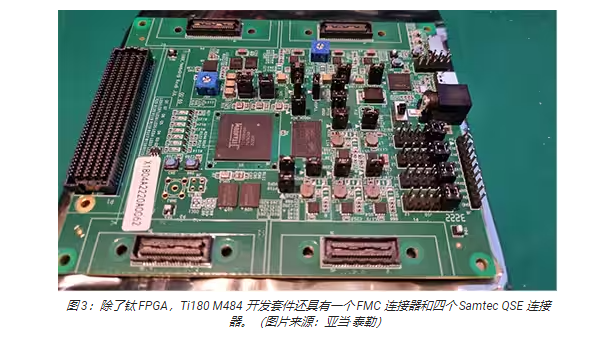

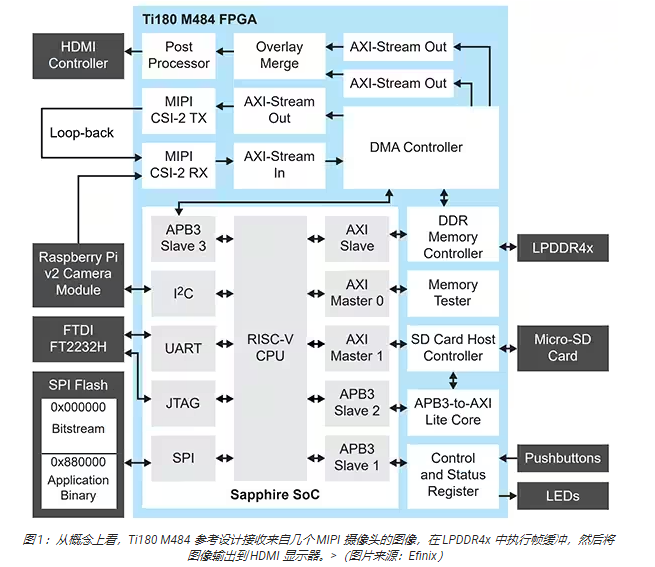

開(kāi)發(fā)板是FPGA評(píng)估過(guò)程的關(guān)鍵要素,因?yàn)樗鼈兛捎糜谔剿髌骷驮蛻?yīng)用的功能,從而有助于降低整體風(fēng)險(xiǎn)。第一個(gè)可用于評(píng)估鈦 FPGA 并開(kāi)始原型設(shè)計(jì)應(yīng)用的開(kāi)發(fā)板是 Ti180 M484(圖 3)。該板具有一個(gè)FPGA夾層卡(FMC)連接器和四個(gè)Samtec QSE連接器。

該開(kāi)發(fā)板安裝的 Ti180 FPGA 提供 172K XLR 單元、32 個(gè)全局時(shí)鐘、640 個(gè)數(shù)字信號(hào)處理 (DSP) 元件和 13 兆位 (Mbit) 嵌入式 RAM。DSP 元件能夠?qū)崿F(xiàn)定點(diǎn) 18 x 19 乘法和 48 位乘法。此 DSP 還可以針對(duì)在雙通道或四通道配置中運(yùn)行的單指令多數(shù)據(jù) (SIMD) 操作進(jìn)行優(yōu)化。DSP 元素也可以配置為執(zhí)行浮點(diǎn)運(yùn)算。

與大多數(shù)開(kāi)發(fā)板一樣,Ti180 開(kāi)發(fā)板提供簡(jiǎn)單的 LED 和按鈕。然而,它的真正力量在于它的接口能力。Ti180 開(kāi)發(fā)板提供低引腳數(shù) FMC 連接器,可連接各種外設(shè)。由于FMC卡是一種廣泛使用的標(biāo)準(zhǔn),因此有許多FMC卡可以連接高速模數(shù)轉(zhuǎn)換器(ADC)、數(shù)模轉(zhuǎn)換器(DAC)、網(wǎng)絡(luò)和存儲(chǔ)器/ 存儲(chǔ)解決方案。

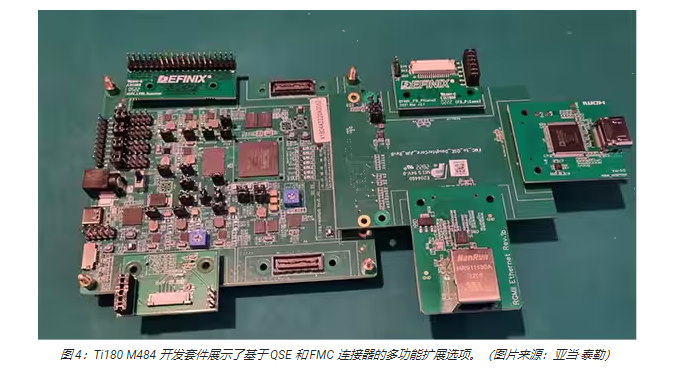

除了FMC連接外,該板還提供四個(gè)Samtec QSE連接器,使開(kāi)發(fā)人員能夠添加擴(kuò)展卡。這些 QSE 連接器用于提供 MIPI 輸入和輸出,每個(gè) QSE 連接器提供 MIPI 輸入或輸出。

Ti180 板還提供 256 Mbits 的 LPDDR4,以支持圖像或信號(hào)處理應(yīng)用所需的高性能存儲(chǔ)器。此外,該開(kāi)發(fā)板還提供一系列 25、33.33、50 和 74.25 MHz 時(shí)鐘選項(xiàng),可與器件鎖相環(huán) (PLL) 配合使用,以產(chǎn)生不同的內(nèi)部頻率。

在開(kāi)發(fā)過(guò)程中,在電路板上實(shí)時(shí)重新編程和調(diào)試的能力至關(guān)重要,需要JTAG連接,JTAG通過(guò)USB-C接口在板上提供。還提供兩個(gè) 256 Mbit NOR 閃存器件形式的非易失性存儲(chǔ)器,可用于演示配置解決方案。

該板由包裝盒隨附的 12 伏通用電源適配器供電。還包括FMC到QSE的分線,以及用于HDMI,以太網(wǎng),MIPI和LVDS的基于QSE的擴(kuò)展卡。為了演示 Ti180 圖像處理能力,還提供了一張雙 RPI 子卡和兩張 IMX477 相機(jī)卡。

軟件環(huán)境

針對(duì) Ti180 開(kāi)發(fā)板實(shí)現(xiàn)設(shè)計(jì)使用 Efinix 軟件 Efinity。該軟件能夠通過(guò)合成、放置和路由生成比特流。它還為開(kāi)發(fā)人員提供知識(shí)產(chǎn)權(quán) (IP) 模塊、時(shí)序分析和片上調(diào)試。

請(qǐng)注意,需要開(kāi)發(fā)板才能訪問(wèn)Efinity軟件。但是,與其他供應(yīng)商不同,該工具沒(méi)有需要額外許可的不同版本。

在Efinity中,將針對(duì)所選設(shè)備創(chuàng)建新項(xiàng)目。然后可以將 RTL 文件添加到項(xiàng)目中,并為時(shí)序和 I/O 設(shè)計(jì)創(chuàng)建約束。在Efinity中,開(kāi)發(fā)人員還可以利用HSIO,GPIO和專用I / O實(shí)現(xiàn)I / O設(shè)計(jì)。

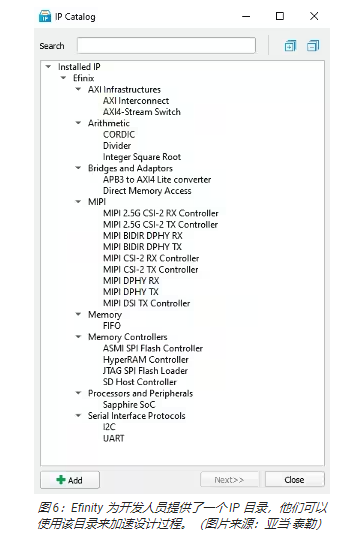

FPGA 設(shè)計(jì)的一個(gè)關(guān)鍵要素是利用 IP,尤其是對(duì)于復(fù)雜的 IP,如 AXI 互連、內(nèi)存控制器和軟核處理器。Efinity為開(kāi)發(fā)人員提供了一系列可用于加速設(shè)計(jì)過(guò)程的IP模塊。

雖然 FPGA 在實(shí)現(xiàn)并行處理結(jié)構(gòu)方面非常出色,但許多 FPGA 設(shè)計(jì)都包含軟核處理器。這些提供了實(shí)現(xiàn)順序處理(如網(wǎng)絡(luò)通信)的能力。為了在Efinix設(shè)備中部署軟核處理器,Efinity提供了Sapphire片上系統(tǒng)(SoC)配置工具。Sapphire 允許開(kāi)發(fā)人員定義一個(gè)多處理器系統(tǒng),該系統(tǒng)具有跨多個(gè)處理器的緩存和緩存一致性,以及運(yùn)行嵌入式 Linux 操作系統(tǒng)的能力。在 Sapphire 中,開(kāi)發(fā)人員可以在一到四個(gè)軟核處理器之間進(jìn)行選擇。

正在實(shí)現(xiàn)的軟核處理器是VexRiscV軟CPU,它基于RISC-V指令集架構(gòu)。VexRiscV 處理器是一種 32 位實(shí)現(xiàn),具有流水線擴(kuò)展并提供可配置的功能集,使其成為在 Efinix 設(shè)備中實(shí)現(xiàn)的理想選擇。可選配置包括乘法器、原子指令、浮點(diǎn)擴(kuò)展和壓縮指令。根據(jù) SoC 系統(tǒng)的配置,性能范圍在 0.86 到 1.05 DMIPS/MHz 之間。

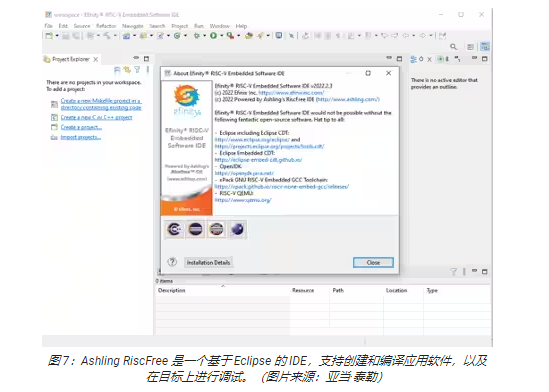

一旦在Efinix設(shè)備中設(shè)計(jì)和實(shí)現(xiàn)了硬件環(huán)境,就可以使用Ashling RiscFree IDE開(kāi)發(fā)應(yīng)用軟件。Ashling RiscFree是一個(gè)基于Eclipse的IDE,它支持創(chuàng)建和編譯應(yīng)用程序軟件,以及在部署之前對(duì)目標(biāo)進(jìn)行調(diào)試以微調(diào)應(yīng)用程序。

如果正在開(kāi)發(fā)嵌入式Linux解決方案,則提供所有必要的引導(dǎo)工件,包括第一階段引導(dǎo)加載程序,OpenSBI,U-Boot和使用Buildroot的Linux。或者,如果需要實(shí)時(shí)解決方案,開(kāi)發(fā)人員可以使用 FreeRTOS。

人工智能實(shí)施

基于RISC-V軟核操作的是Efinix的AI實(shí)現(xiàn)。這利用了RISC-V處理器的自定義指令功能來(lái)實(shí)現(xiàn)TensorFlow Lite解決方案的加速。RISC-V處理器的使用還使用戶能夠創(chuàng)建自定義指令,這些指令可用作AI推理之后的預(yù)處理或后處理的一部分,從而創(chuàng)建響應(yīng)速度更快、確定性更強(qiáng)的解決方案。

要開(kāi)始實(shí)施 AI,第一步是探索 Efinix 模型動(dòng)物園,這是一個(gè)針對(duì)其終端技術(shù)優(yōu)化的 AI/ML 模型庫(kù)。對(duì)于使用Efinix設(shè)備的開(kāi)發(fā)人員,可以訪問(wèn)模型動(dòng)物園,并使用Jupyter Notebooks或Google Colab訓(xùn)練網(wǎng)絡(luò)。一旦網(wǎng)絡(luò)經(jīng)過(guò)訓(xùn)練,就可以使用TensorFlow Lite轉(zhuǎn)換器將其從浮點(diǎn)模型轉(zhuǎn)換為量化模型。

一旦采用TensorFlow Lite格式,Efinix的tinyML加速器可用于在RISC-V解決方案上創(chuàng)建可部署的解決方案。tinyML 生成器使開(kāi)發(fā)人員能夠自定義加速器實(shí)現(xiàn)并生成項(xiàng)目文件。以這種方式部署時(shí),加速范圍可能在 4 倍到 200 倍之間,具體取決于所選的架構(gòu)和自定義。

結(jié)論

Efinix 器件憑借其獨(dú)特的 XLR 架構(gòu)為開(kāi)發(fā)人員提供了靈活性。該工具鏈不僅能夠?qū)崿F(xiàn) RTL 設(shè)計(jì),還可以實(shí)現(xiàn)部署軟核 RISC-V 處理器的復(fù)雜 SoC 解決方案。在軟核 SoC 之上構(gòu)建的是一種 AI/ML 解決方案,支持部署 ML 推理。

審核編輯黃宇

-

FPGA

+關(guān)注

關(guān)注

1626文章

21670瀏覽量

601873 -

AI

+關(guān)注

關(guān)注

87文章

30160瀏覽量

268427 -

開(kāi)發(fā)板

+關(guān)注

關(guān)注

25文章

4945瀏覽量

97201 -

ML

+關(guān)注

關(guān)注

0文章

146瀏覽量

34607

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

為什么以及如何將 Efinix FPGA 用于 AI/ML 成像 — 第 1 部分:入門指南

為什么以及如何將 Efinix FPGA 用于 AI/ML 成像第 2 部分:圖像采集和處理

阿毛FPGA入門公益學(xué)習(xí)班第3講回播

新冒出來(lái)的Efinix會(huì)革掉FPGA的命么?

【技術(shù)雜談】動(dòng)畫演示各大算法,助力 AI 小白順利入門

FPGA從入門到精通(1) - 前序

Efinix? 推出Trion? T20 FPGA樣品 支持主要客戶和市場(chǎng)的需求

Efinix將與三星合作開(kāi)發(fā)Quantum eFPGA

【原創(chuàng)】深度揭秘FPGA新玩家EFINIX

FPGA如何在PC中實(shí)現(xiàn)AI和ML

如何進(jìn)行電源設(shè)計(jì)-第1部分

為什么以及如何使用 Efinix FPGA 進(jìn)行 AI/ML 成像 — 第 1 部分:入門

為什么以及如何使用 Efinix FPGA 進(jìn)行 AI/ML 成像 — 第 1 部分:入門

評(píng)論