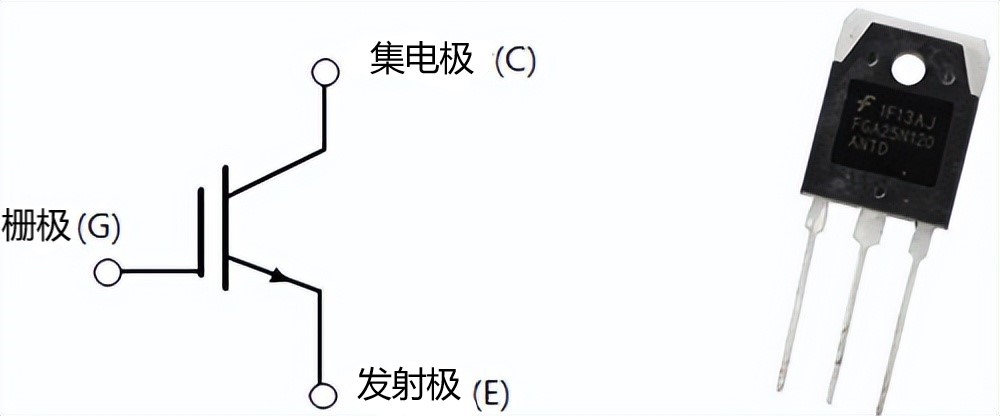

IGBT全稱絕緣柵雙極型晶體管(Insulated Gate Bipolar Transistor)。其歷史可以追溯到1979 年。當時,在美國通用電氣公司的 B.J.Baliga 首次在論文中描述了一個四層垂直器件結構,并通過相關實驗證明了可以通過調節柵極電壓來控制該結構的電流大小,這是工業史上首次有人展示IGBT的工作模式。之后不久,美國的H.W.Becke 和 C.F.Wheatle 在一份專利中首次指出 IGBT 工作時沒有出現晶閘管(Thyristor)效應。

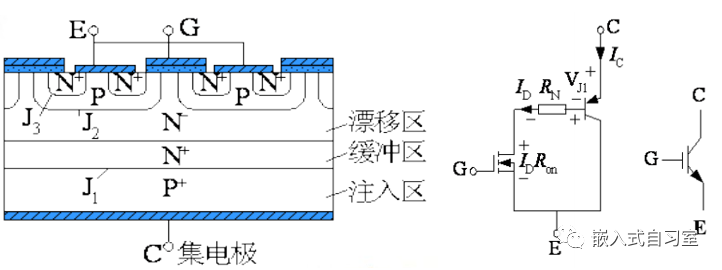

1982 年相關文獻報道了首個真正可以驅動電流進行工作的IGBT,其具有對稱的600V擊穿電壓性能,并且可以在直流、交流電路中應用。最初出現的對稱型 IGBT 采用了混合解決方案,集成在一起的功率 MOS 場效應晶體管部分導通時的溝道電流向 BJT 部分提供工作時的基極電流,同時 BJT 部分發射極向基區注入空穴,使得 MOS 場效應晶體管部分體區附近累積載流子,從而改善導通特性。

MOS 場效應晶體管部分載流子累積又使得此復合結構中 BJT 部分的基極驅動電流顯著增加,二者協同工作,從而改善了整個器件的特性。自 1979 年 IGBT 被提出以來,其性能和制造工藝都得到了顯著的優化、改進,應用范圍也越來越廣。工業界一般將其發展趨勢按襯底工程和柵工程技術歸納為六代,

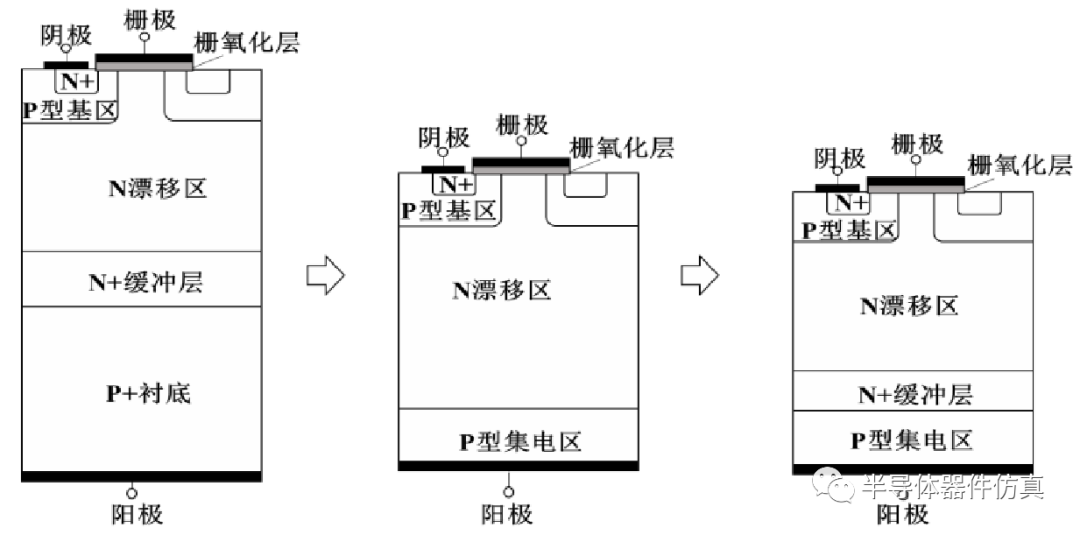

如圖1,其襯底工程技術經歷了從穿通(punch through, PT)型到非穿通型(not punch through, NPT),再到場截止型(field stop, FS)的演變。

圖1 IGBT襯底工程技術發展

穿通型 IGBT 采用厚的 P+襯底,在其上進行兩次外延,分別形成器件的緩沖層和漂移區,這種工藝不需要另外的背注工藝,工藝難度低,且可以與 MOS 工藝很好地兼容。但是若要求的器件耐壓較高,則需要較厚的外延層,工藝成本較高,且會使得器件導通狀態下外延層壓降變大,從而增大導通壓降。另外,因襯底摻雜較高,在導通期間正向電壓的作用下會向漂移區注入大量空穴,器件關斷時這些空穴的復合作用使得器件不能立即關斷,大大增加了關斷損耗。且采用 PT 型襯底工藝的器件,其導通壓降隨溫度升高而降低,在并聯應用時電流不能平均分配,限制了其應用。

G.Miller 等人在 20 世紀 80 年代末提出了非穿通型結構,該工藝通過采用高電阻率的區熔單晶片代替昂貴的直拉異質厚外延硅片,降低了工藝成本。該結構集電極通過背注和退火形成,這使得集電極摻雜相對較低,減小關斷損耗。與 PT 型襯底工藝相反,采用 NPT 型襯底工藝的器件,其導通壓降隨溫度升高而增加,這增加了 IGBT 的可利用范圍。但此結構仍未能改善穿通型 IGBT 在高耐壓應用時需要做較厚漂移區的狀況。鑒于此,場截止型 IGBT 應運而生。

場截止型結構具有與穿通結構相似的緩沖層,但其緩沖層的摻雜濃度比穿通結構的更低。在耐壓相同的條件下,場截止型 IGBT 元胞縱向深度要明顯小于穿通型和非穿通型 IGBT,這可以降低器件的導通飽和壓降和關斷時間。與 NPT 型 IGBT一樣,其導通壓降也隨溫度升高而增加,可應用于大電流并聯場景。隨著工藝的進步,場截止型 IGBT 厚度可持續減薄, 2011 年,英飛凌公司制造出了硅片厚度僅為 40μm 的場截止型 IGBT。

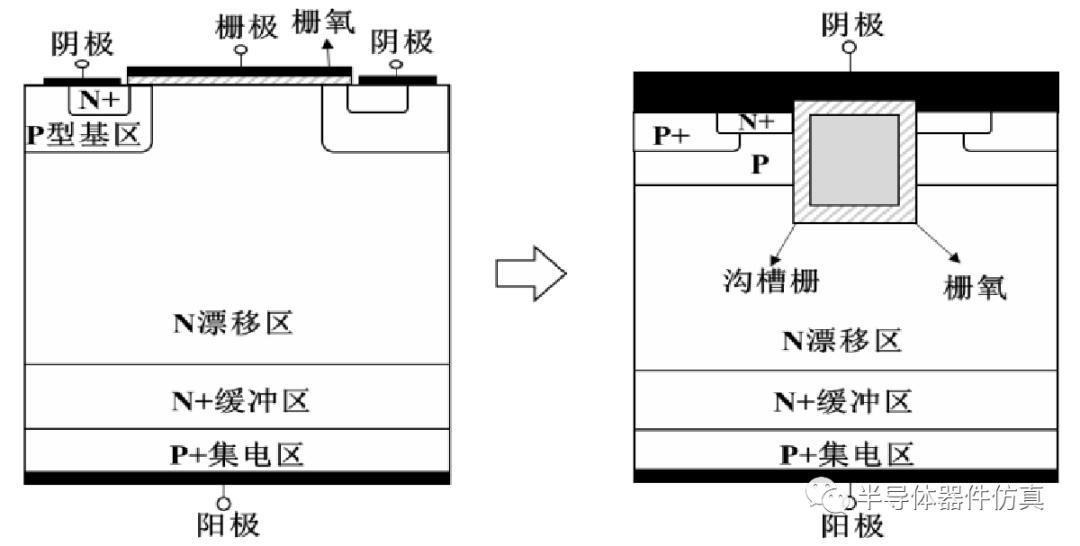

從柵工程技術上來看,IGBT 經歷了平面柵到溝槽柵的演變,圖2所示是不同柵結構 IGBT 演變示意圖。使用 DMOS 工藝制造的平面柵 IGBT 技術上受擴散限制,且因為它具有寄生 JFET 電阻以及水平電流路徑,導通壓降較高。與之相反,溝槽柵 IGBT(trench gate IGBT, TIGBT)制造時工藝上不受擴散限制,不具有寄生JFET 電阻,并且具有垂直電流路徑,因此其導通狀態壓降要低得多。溝槽柵 IGBT是由 H.R.Chang 和 B.J.Baliga 于 20 世紀 80 年代末提出的。非對稱溝槽柵 IGBT在 P 基極和 N+發射區進行擴散后,通過使用反應離子刻蝕蝕刻出柵極溝槽。該槽的深度必須大于 P 基極區的結深,以便在溝槽側壁上形成的溝道能連接 N+發射區和 N 漂移區,形成 MOS 結構。

接著,在溝槽的表面生長一層犧牲氧化層,隨后重新生長柵氧化層、淀積多晶硅填充溝槽、將多晶硅平坦化使柵電極凹進略微低于硅表面。淀積層間介質膜后,形成N+發射極和 P 基極區的接觸窗口。在溝槽柵 IGBT 工藝過程中,通常在 P 型基區表面靠近 N+發射區的地方擴散形成一個高摻雜的 P 型接觸區,以改善基區的接觸和抑制 N+發射區、P 型基區、N 型漂移區和 P+集電極所形成晶閘管結構的閂鎖效應。P 型接觸區的深度通常比基區小,并且小于溝槽柵的深度以避免產生寄生的結型場效應晶體管。

采用溝槽柵結構的優勢在于消除了平面柵結構中的 JFET 電阻,且因溝槽柵將柵極做在 IGBT 內部,在導通時可以形成載流子濃度更高的溝道,提高了器件性能。但溝槽柵 IGBT 結構缺點在于溝槽柵底部電場較高,易發生擊穿,因此在應用時需要對其進行結構和工藝上的優化。

圖2 IGBT柵極工程技術發展

圖2 IGBT柵極工程技術發展

本文以溝槽柵場截止型IGBT為例進行器件仿真建模介紹。該實例仿真研究了IGBT不同尺寸溝槽柵以及不同N+發射極延伸距離對器件性能的影響。也因為要仿真出N+發射極延伸距離的影響所以本實例構建了三維結構,因為器件實際的延伸距離不會僅僅在一個維度方向。結構建立后,Ic-Vg,Ic-Vc以及BV(Breakdown Voltage)特性被仿真出來。

隨后,在Sdevice中,構建IGBT的標準測試電路,在混合模式下跑出IGBT的開關特性,以及在器件開關操作過程中的能量損失(Eon和Eoff)。此外,為了獲取器件的失效時間,在短路條件下仿真了該器件結構的電力和熱力學特性。器件本身的Eon-Von,BV-Von以及tsc-Von(short-circuit failure time)特性都得到了全面分析。

PROCESS構建IGBT器件結構和摻雜分布

本實例根據圖3的版圖和圖4的器件參數分7個步驟進行了工藝仿真。

圖3 IGBT版圖示意圖

圖4 SPROCESS 仿真參數

圖4中的參數具體含義如下:

pmesh:過程仿真中的網格控制參數

dthick: IGBT厚度,默認60um

zfac:發射端N+區域與z方向器件整個寬度的比值。本實例中使用的值分別為10、20和30

Xmesa:兩個相鄰的柵極邊緣之間的橫向距離。本項目中使用的值分別為2、3和4um

ndriftD:漂移區的摻雜濃度,默認3e14

nbD: 場截止區摻雜濃度默認1e13

pwelD:pwell摻雜濃度,默認5e16

niD:n注入(pwell和n漂移層之間)的摻雜濃度 默認3e14

AnodeD:P+集電極的摻雜濃度 默認3e15

根據圖4的參數器件可以分成以下步驟進行工藝仿真:

1.自適應網格劃分和襯底的定義

2.氣相淀積外延層

3.刻蝕溝槽

4.淀積柵氧和多晶硅

5.發射極摻雜注入和擴散

6.場截止和P+集電極摻雜注入和擴散

7.電極定義

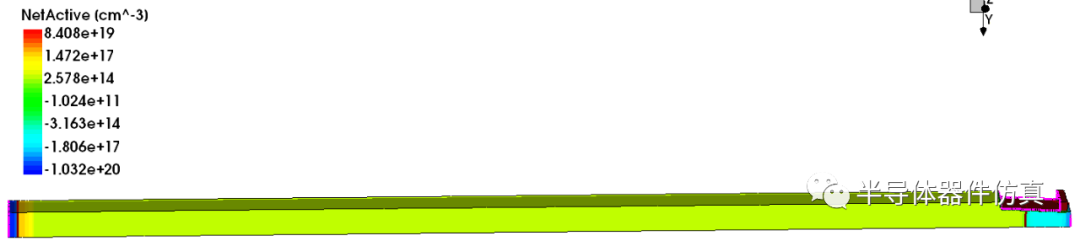

可以獲得圖5所示的3D模型,為了便于觀察圖中將器件放倒,其左側為實際器件的底部,也就是集電極,右側包括實際器件的溝槽柵以及發射極。圖6為圖5右側的二維截面圖。可以觀察到溝槽柵的深度以及發射極摻雜。

圖5 IGBT 3D結構圖

圖6 IGBT 剖面圖

電學仿真1

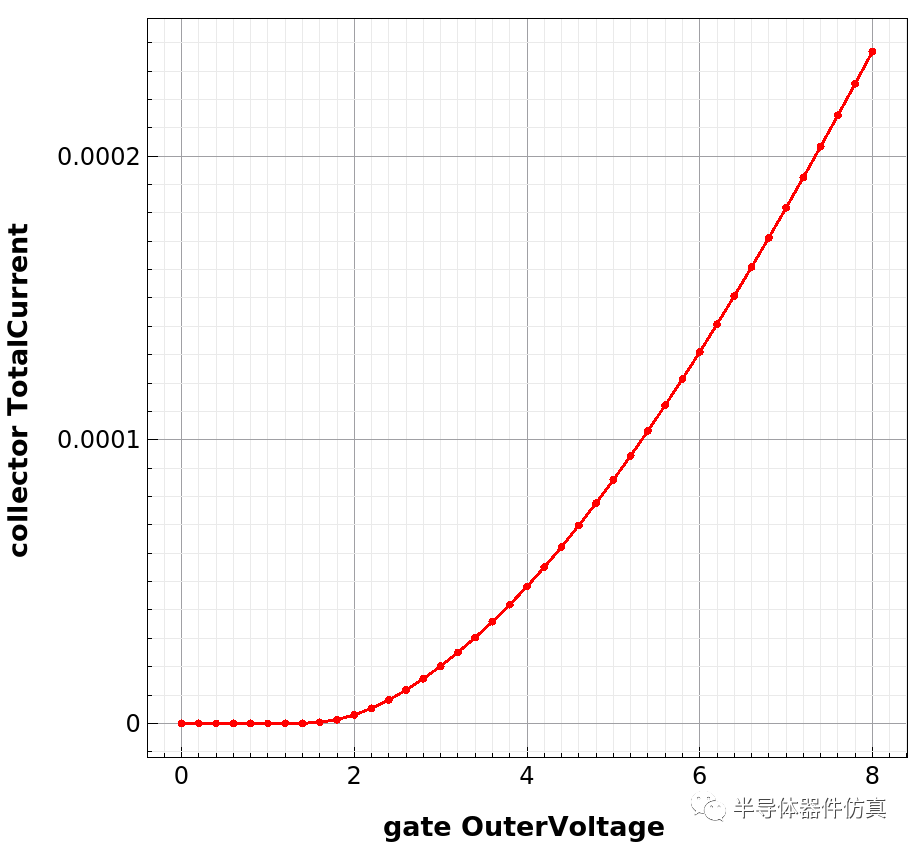

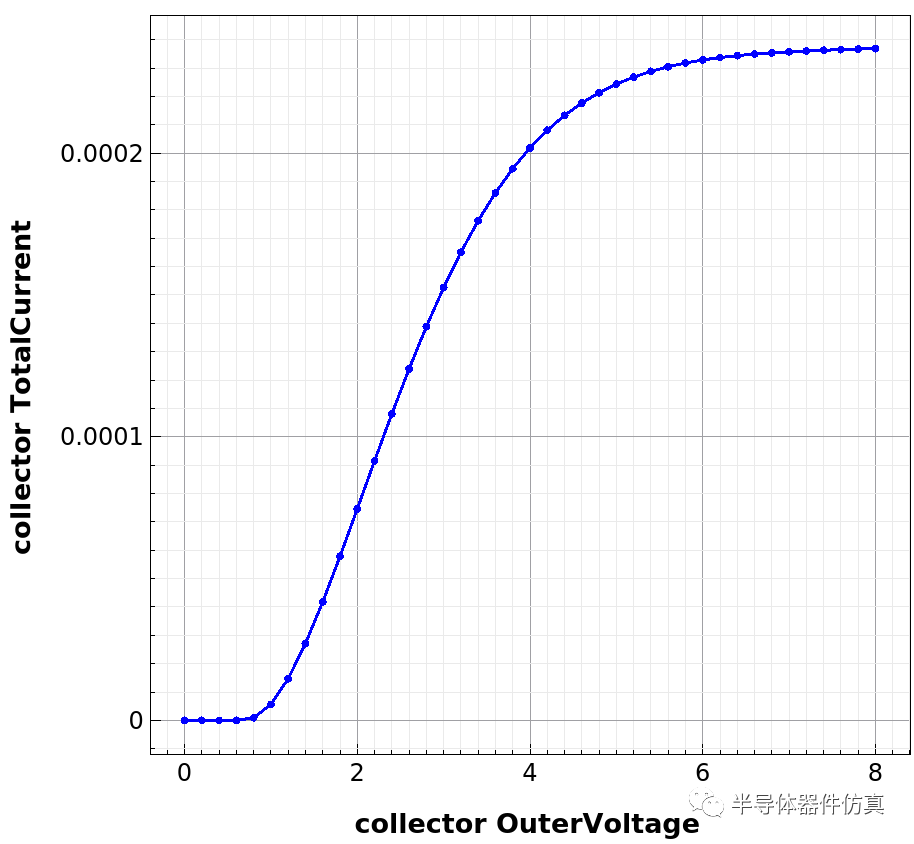

建立好3D結構后,則可以進行一系列器件特性仿真,得到包括圖7,8,9的Ic-Vg,Ic-Vc以及擊穿電壓特性,以及根據前述曲線算得圖10的Vth,Von,BV器件性能。

圖7 Ic-Vg曲線

圖8 Ic-Vc曲線

圖9 BV曲線

圖10 提取出的IGBT器件特性

電學仿真2

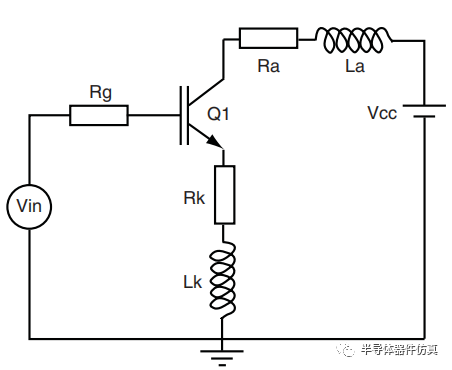

圖11 IGBT開關特性仿真電路

圖11中,Q1為IGBT器件,這里通過AreaFactor參數設置為1e5,將整個器件的終端電流倍增系數放大1×10^5^

圖12展示了當一個單脈沖VIn輸入圖11電路時的瞬態響應。其中Vcc為200V。通過將集電極電流和集電極電壓的乘積按相應的時間間隔積分,計算出器件開啟狀態和關閉狀態的能量消耗值。對于IGBT器件,器件關閉過程中的集電極尾電流是關閉狀態能量優化的一個重要特性。因此,在器件優化過程中,器件設計師需要考慮Eoff與Eon或Eoff和Von的趨勢變化進行器件設計。

圖12 IGBT開關瞬態曲線

圖13 IGBT短路失效特性仿真電路

圖13展示了用于仿真短路失效特性的測試電路。測試電路中的器件Q1是IGBT,和前面一樣終端電流和電荷乘以比例因子1e5。圖14顯示了設備在短路下的電氣和熱特性。在仿真過程中,柵極和集電極端子都保持在相應的最大工作值,并等待器件溫度達到其熔點(硅的熔點為1687 K)。最大電壓與器件溫度達到熔點之間的時間間隔定義為短路失效時間(tsc)。

圖14 IGBT短路失效電流、溫度曲線

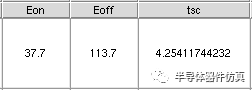

圖15 提取IGBT開關和失效特性參數

通過仿真可以得出TG-FS-IGBT器件性能Eoff-Von、BV-Von、tsc-Von強烈依賴于Xmesa和zfac參數的變化。對于擊穿電壓和短路失效時間,兩個參數值都隨著Von的減小而減小。zfac值的降低改善了器件的短路失效特性。通過增加Xmesa的值,短路失效特性還可以得到進一步的改進。

本文器件描述參考苗晶晶,姚兆銘,張森碩士學位畢業論文

-

IGBT

+關注

關注

1265文章

3761瀏覽量

248326 -

MOS

+關注

關注

32文章

1247瀏覽量

93488 -

場效應晶體管

+關注

關注

6文章

359瀏覽量

19473 -

BJT

+關注

關注

0文章

221瀏覽量

18118

發布評論請先 登錄

相關推薦

絕緣柵雙極型晶體管IGBT工藝仿真

絕緣柵雙極型晶體管IGBT工藝仿真

評論