徹底理解鎖存器,讓你不再為鎖存器頭疼!

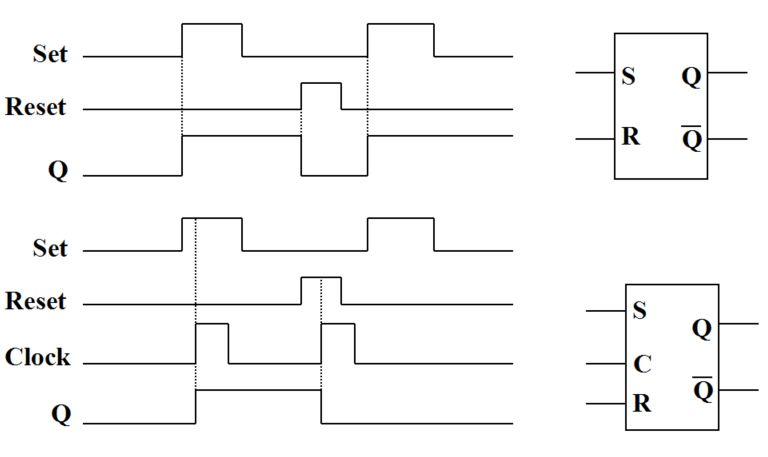

鎖存器(latch):是電平觸發的存儲單元,數據存儲的動作(狀態轉換)取決于輸入時鐘(或者使能)信號的電平值,盡當鎖存器處于使能狀態時,輸出才會隨著數據輸入發生變化。

分為普通鎖存器和門控鎖存器,普通鎖存器無控制信號,輸出狀態始終直接由輸入決定。在實際的數字系統中,為了協調各部分的工作,往往需要有一個特定的控制信號去控制鎖存器狀態轉換的時間,在控制信號無效時,輸出保持不變,不隨輸入變換;當控制信號有效時,輸出由輸入決定,跟隨輸入變化。

①正是因為門控鎖存器在控制信號有效的期間內,都可以接收輸入信號, 所以,激勵信

號的任何變化, 都將直接引起鎖存器輸出狀態的改變。這時輸入信號若發生多次變化,輸出

狀態也可能發生多次變化,這一現象稱為鎖存器的空翻。

②其次,當門控鎖存器的控制信號有效時,鎖存器就變成了一個組合電路,時序邏輯電

路的模型就等效為兩個各組合電路互為反饋的反饋系統,因此,系統有可能會因為瞬態特性

不穩定而產生振蕩現象。

觸發器(flip-flop)是邊沿敏感的存儲單元,數據存儲的動作(狀態轉換)由某一信號

的上升或者下降沿進行同步的(限制存儲單元狀態轉換在一個很短的時間內) 。(鐘控 D 觸

發器其實就是 D 鎖存器,邊沿 D 觸發器才是真正的 D 觸發器)

觸發器分為兩種,一種是主從觸發器和邊沿觸發器。主從觸發器在時鐘有效期內 (主觸

發器) 接收數據,在時鐘邊沿輸出狀態轉換。邊沿觸發器在時鐘邊沿期間, 觸發器才接收數

據并使輸出狀態轉換。

目前,主從觸發器基本上已經很少見了,實際使用的大都是邊沿觸發器。

寄存器(register):用來暫時存放參與運算的數據和運算結果。在實際的數字系統中,

通常把能夠用來存儲一組二進制代碼的同步時序邏輯電路稱為寄存器。

區別與聯系:由于觸發器內有記憶功能,因此利用觸發器可以方便地構成寄存器。由于

一個觸發器能夠存儲一位二進制碼,所以把 n 個觸發器的時鐘端口連接起來就能構成一個存

儲 n 位二進制碼的寄存器。

從寄存數據的角度來講,寄存器和鎖存器的功能是相同的;它們的區別在于寄存器是同

步時鐘控制,而鎖存器是電位信號控制。

一般的設計規則是:在絕大多數設計中避免產生鎖存器。它會讓您設計的時序完蛋,并

且它的隱蔽性很強,非老手不能查出。鎖存器最大的危害在于不能過濾毛刺 (使能信號有效

時,輸出狀態可能隨輸入多次變化,產生空翻) 。這對于下一級電路是極其危險的。所以,

只要能用 D 觸發器的地方,就不用鎖存器。

基本概念:

觸發器是指有時鐘邊沿觸發的存儲單元。鎖存器指一個由信號而不是時鐘控制的電平敏

感的設備。

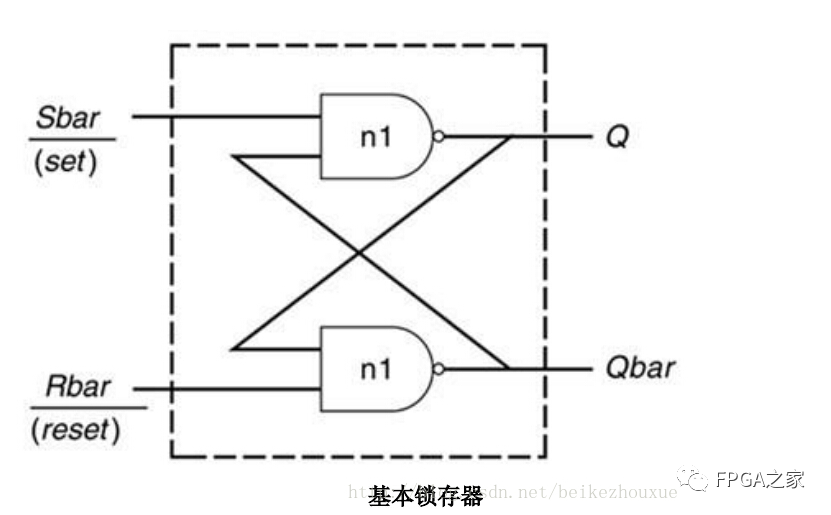

鎖存器的工作原理:

鎖存器不同于觸發器,鎖存器在不鎖存數據時,輸出端的信號隨輸入信號變化,就像信

號通過一個緩存器一樣;一旦鎖存信號起鎖存作用,則數據被鎖住,輸入信號不起作用。因

此鎖存器也稱為透明鎖存器,值得是不鎖存是輸出對輸入是透明的。

鎖存器具備下列三個缺點:

(1)對毛刺敏感,不能異步復位,因此在上電后處于不確定的狀態。

(2)鎖存器會使靜態時序分析變得非常復雜,不具備可重用性。(首先, 鎖存器沒有時

鐘參與信號傳遞,無法做 STA;其次,綜合工具會將 latch 優化掉,造成前后仿真結果不一

致)

(3)在 PLD 芯片中,基本的單元是由查找表和觸發器組成的,若生成鎖存器反而需要

更多的資源。根據鎖存器的特點可以看出,在電路設計中,要對鎖存器特別謹慎,如果設計

經過綜合后產生出和設計意圖不一致的鎖存器,則將導致設計錯誤,包括仿真和綜合。因此,

在設計中需要避免產生意想不到的鎖存器。

如果組合邏輯的語句完全不使用 always 語句塊,就可以保證綜合器不會綜合出鎖存器,

例如:

assign a = din ? x : y;

上述語句不需要保持信號 a 的前一個狀態,因此肯定不會產生鎖存器。

在基于 always 的組合邏輯描述語句中容易綜合出鎖存器的地方:1:if 語句的使用中缺

少 else 語句(前提是不是始終邊沿觸發);2:case 語句中沒有給出全部的情況。

從上圖可以看出綜合出來的是鎖存器。

針對這種情路可以采用一些措施來防止生成鎖存器:給輸出變量幅初值;增加 else 語

句;將鎖存器改為帶使能的觸發器。如下:

此時綜合出來的就是選擇器。

-

數據

+關注

關注

8文章

6909瀏覽量

88850 -

電平

+關注

關注

5文章

360瀏覽量

39858 -

鎖存器

+關注

關注

8文章

905瀏覽量

41448

發布評論請先 登錄

相關推薦

一文徹底理解鎖存器

一文徹底理解鎖存器

評論