一項(xiàng)新的研究發(fā)現(xiàn),通過將原子薄器件與傳統(tǒng)的微芯片相結(jié)合,科學(xué)家們創(chuàng)造了模仿大腦的混合電子設(shè)備,可以幫助實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)人工智能系統(tǒng),其能效遠(yuǎn)遠(yuǎn)高于標(biāo)準(zhǔn)電子設(shè)備。

隨著電子產(chǎn)品越來越小,科學(xué)家們正在為下一代電子產(chǎn)品研究原子薄的2D材料。例如,石墨烯由單層碳原子組成,二硫化鉬由夾在兩層硫原子之間的一片鉬原子制成。

研究高級(jí)作者M(jìn)ario Lanza是位于沙特阿拉伯圖瓦爾的阿卜杜拉國(guó)王科技大學(xué)材料科學(xué)與工程副教授,他說:“二維材料不僅具有最先進(jìn)的電氣性能,而且還具有優(yōu)異的熱、機(jī)械、光學(xué)和化學(xué)特性,這可能會(huì)產(chǎn)生目前尚不存在的新應(yīng)用。”

“Most people’s expertise is insemiconductors. We are experts in insulators.”

—Mario Lanza, King Abdullah University of Science and Technology

多個(gè)研究團(tuán)隊(duì)開發(fā)了基于2D材料的原型設(shè)備。然而,沒有一個(gè)顯示出計(jì)算或存儲(chǔ)數(shù)據(jù)的能力。此外,它們的制造主要依賴于與標(biāo)準(zhǔn)工業(yè)技術(shù)不兼容的合成和加工方法。此外,操縱單層2D材料是具有挑戰(zhàn)性的,因?yàn)楫?dāng)將它們從生長(zhǎng)它們的表面轉(zhuǎn)移到對(duì)應(yīng)用更有用的襯底上時(shí),可能會(huì)出現(xiàn)缺陷。這些缺陷降低了器件的一致性和成品率。

現(xiàn)在,科學(xué)家們已經(jīng)創(chuàng)造了他們所說的第一個(gè)用2D材料制造的密集集成微芯片,所有這些都使用了與半導(dǎo)體行業(yè)兼容的工藝。Lanza說:“我們不僅取得了優(yōu)異的特性,而且還實(shí)現(xiàn)了高產(chǎn)量和低變異性。”

在這項(xiàng)新的研究中,研究人員用六方氮化硼進(jìn)行了實(shí)驗(yàn)。這種原子級(jí)薄的陶瓷經(jīng)常被用作2D電子器件中的絕緣材料。“大多數(shù)人的專業(yè)知識(shí)都在半導(dǎo)體領(lǐng)域,”Lanza說,“我們是絕緣體方面的專家。”

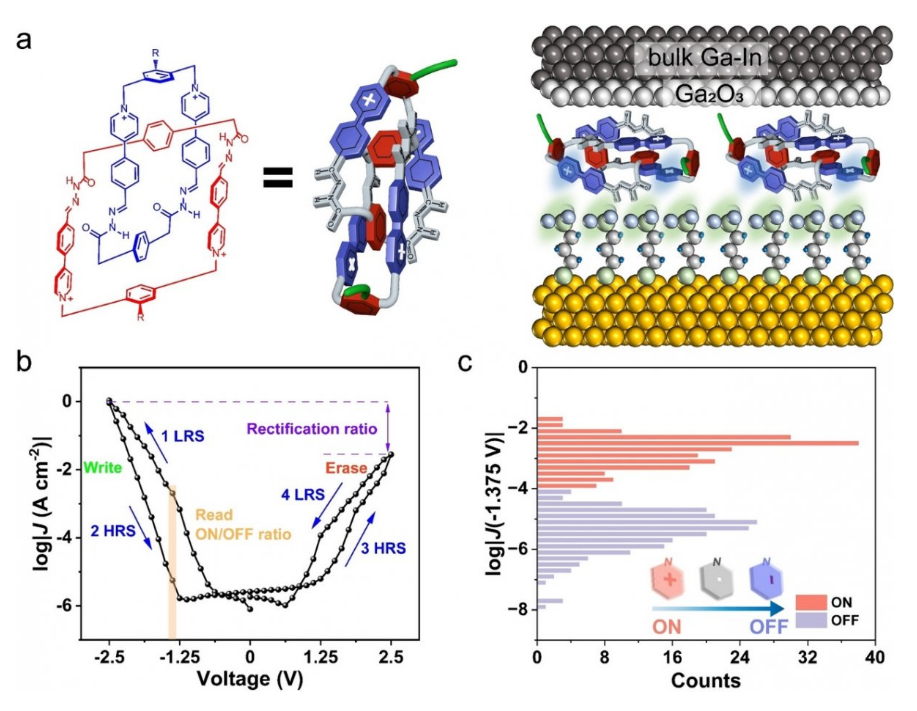

科學(xué)家們希望克服以前基于2D材料的設(shè)備所面臨的許多挑戰(zhàn)。例如,Lanza和他的同事們沒有試圖用2D材料制造晶體管,而是致力于制造憶阻器。憶阻器,或稱記憶電阻器,本質(zhì)上是一種開關(guān),可以在電源關(guān)閉后記住它們被切換到哪種電狀態(tài)。

Lanza說:“大多數(shù)團(tuán)隊(duì)都專注于晶體管,可能是因?yàn)樗鼈兪请娮赢a(chǎn)品的旗艦部件。相反,我們專注于憶阻器,它目前的市場(chǎng)規(guī)模要小得多,但在數(shù)據(jù)存儲(chǔ)、計(jì)算、加密和通信方面也有巨大的潛力。”

世界各地的科學(xué)家希望使用憶阻器和類似的組件來制造像神經(jīng)元一樣既能計(jì)算又能存儲(chǔ)數(shù)據(jù)的電子設(shè)備。當(dāng)傳統(tǒng)的微芯片在處理器和存儲(chǔ)器之間來回?cái)噥y數(shù)據(jù)時(shí),這些憶阻器件可以大大減少能量和時(shí)間損失。這種受大腦啟發(fā)的神經(jīng)形態(tài)硬件也可能被證明是實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)的理想選擇。這些人工智能系統(tǒng)越來越多地被用于支持自動(dòng)駕駛汽車和分析醫(yī)療掃描等應(yīng)用。

Lanza說,憶阻器是“能夠容忍缺陷的簡(jiǎn)單設(shè)備”。相比之下,晶體管“需要完美的晶體材料”,他如此解釋道。此外,之前的大多數(shù)工作都依賴于只有一兩層厚的2D材料,Lanza和他的同事使用了一張由大約18層組成的2D材料片,總厚度約為6納米。Lanza說:“這種較厚的材料不那么容易破裂。”

此外,研究人員沒有在空白基板(如傳統(tǒng)的硅晶片)上制造2D器件,而是在標(biāo)準(zhǔn)CMOS微芯片上制造2D設(shè)備。微芯片可以幫助控制憶阻器中的電流和開關(guān),這有助于成功地制造2D器件。

制造用于計(jì)算的晶體管的研究人員通常使用所謂的前端線步驟。相比之下,Lanza和他的同事在連接晶圓上器件的線路互連的后端建造了憶阻器。憶阻器通常以這種方式集成到微芯片上,“不同之處在于我們使用了2D材料而不是其他材料,”Lanza說。

研究人員將一層六方氮化硼多層片轉(zhuǎn)移到4平方厘米硅微芯片的后端線互連上,該芯片包含200毫米硅片上180納米節(jié)點(diǎn)的CMOS晶體管。接下來,他們通過蝕刻六方氮化硼并在頂部構(gòu)圖和沉積電極,用這種組合制造電路。這些電路每個(gè)都由5乘5的交叉單元陣列組成,每個(gè)交叉單元陣列由一個(gè)晶體管和一個(gè)憶阻器組成。

研究人員指出,盡管大多數(shù)使用2D材料制造的器件尺寸超過1平方微米,但新研究中的憶阻器只有0.053μm2。Lanza說,這些憶阻器“如果有更先進(jìn)的微芯片,可以很容易地制造得更小”。

CMOS晶體管有助于控制2D憶阻器上的電流。這有助于實(shí)現(xiàn)約500萬次開關(guān)循環(huán)的憶阻器壽命,與現(xiàn)有的電阻RAM和相變存儲(chǔ)器大致相當(dāng)。在沒有CMOS晶體管的情況下,憶阻器只經(jīng)歷了大約100次循環(huán)。

研究人員表明,他們可以用設(shè)備進(jìn)行內(nèi)存計(jì)算操作,構(gòu)建“或”和“暗示”邏輯門。通過修改設(shè)備之間的互連,他們可以運(yùn)行更復(fù)雜的操作。

此外,科學(xué)家們注意到,通過施加電脈沖,混合微芯片的電導(dǎo)率可以動(dòng)態(tài)調(diào)整到不同的水平,這種特性被稱為尖峰時(shí)間依賴性塑性。這一特征表明,該設(shè)備可以幫助實(shí)現(xiàn)比傳統(tǒng)神經(jīng)網(wǎng)絡(luò)更接近模仿人腦的尖峰神經(jīng)網(wǎng)絡(luò)。

尖峰神經(jīng)網(wǎng)絡(luò)中的關(guān)鍵組件是“尖峰”,也就是說,只有在給定時(shí)間內(nèi)接收到一定量的輸入信號(hào)后,才會(huì)產(chǎn)生輸出信號(hào)。由于尖峰神經(jīng)網(wǎng)絡(luò)很少發(fā)射尖峰,因此與典型的人工神經(jīng)網(wǎng)絡(luò)相比,它們的數(shù)據(jù)量要少得多,原則上所需的功率和通信帶寬也要少得多。科學(xué)家們指出,傳統(tǒng)的電子設(shè)備不太適合運(yùn)行尖峰神經(jīng)網(wǎng)絡(luò),這導(dǎo)致市場(chǎng)需要開發(fā)新的神經(jīng)形態(tài)硬件來運(yùn)行它們。

作為原理的證明,研究人員使用他們的設(shè)備創(chuàng)建了一個(gè)尖峰神經(jīng)網(wǎng)絡(luò),當(dāng)用Modified National Institute of Standards and Technology(MNIST)手寫數(shù)字?jǐn)?shù)據(jù)庫(kù)的圖像進(jìn)行分類測(cè)試時(shí),這種簡(jiǎn)單的設(shè)備仍然實(shí)現(xiàn)了大約90%的準(zhǔn)確率。

科學(xué)家們注意到,他們的設(shè)備需要大約1.4到5伏的開關(guān)電壓,與2D材料領(lǐng)域的其他原型相比,這一電壓較低,后者可能需要超過20伏的電壓。盡管如此,他們注意到這一電壓高于180nm CMOS節(jié)點(diǎn)處使用的電壓。然而,他們認(rèn)為這種電壓可能不會(huì)阻礙這項(xiàng)技術(shù)的發(fā)展,因?yàn)橛性S多商業(yè)微芯片在更高的電壓下工作,例如,最先進(jìn)的3D-NAND閃存在大約20伏的電壓下編程,所有用于汽車應(yīng)用的雙極CMOS微芯片都需要高達(dá)40伏的電壓。

此前,IBM的研究人員曾試驗(yàn)過在微芯片上放置2D材料的好處。Lanza說,2011年,他們制造了一個(gè)包含一個(gè)石墨烯晶體管和兩個(gè)電感器的電路,并在2014年開發(fā)了一個(gè)更大的電路,其中包含三個(gè)石墨烯晶體、四個(gè)電感器、三個(gè)電容器和兩個(gè)電阻器。然而,IBM顯然放棄了這種方法,“可能是因?yàn)檗D(zhuǎn)移單層2D材料的困難,”他說。相比之下,Lanza和他的同事使用了一種更耐用的18層厚的材料。他預(yù)測(cè),“現(xiàn)在許多其他科學(xué)家將在功能性微芯片上而不是非功能性SiO2襯底上創(chuàng)建他們的原型,這將引發(fā)更多的發(fā)現(xiàn)。”

Lanza還指出,2D材料通常屬于材料科學(xué)家,而不是微芯片工程師。他說:“要做我們做的實(shí)驗(yàn),你需要使用特定的軟件設(shè)計(jì)一個(gè)微芯片,然后制作一個(gè)多項(xiàng)目的晶圓帶,或者像我們的情況一樣,制作一個(gè)完整的晶圓。如果你使用180納米節(jié)點(diǎn)的CMOS技術(shù),就像我們的情況一樣,第一個(gè)成本為25000美元,第二個(gè)成本為100000美元。許多研究小組不僅無法設(shè)計(jì)這個(gè),他們甚至負(fù)擔(dān)不起。在我們的案例中,清華大學(xué)的同事提供了晶圓,我集成了材料。”

Lanza提到,他們的研究已經(jīng)吸引了領(lǐng)先半導(dǎo)體公司的興趣。科學(xué)家們現(xiàn)在的目標(biāo)是超越4平方厘米的硅微芯片,“制造整個(gè)300毫米的晶圓”。

科學(xué)家們?cè)?月27日的《自然》雜志上詳細(xì)介紹了他們的發(fā)現(xiàn)。

審核編輯 :李倩

-

憶阻器

+關(guān)注

關(guān)注

8文章

72瀏覽量

19839 -

微芯片

+關(guān)注

關(guān)注

0文章

61瀏覽量

13562 -

AI芯片

+關(guān)注

關(guān)注

17文章

1860瀏覽量

34919

原文標(biāo)題:神奇的混合憶阻器AI芯片可擴(kuò)展

文章出處:【微信號(hào):IEEE_China,微信公眾號(hào):IEEE電氣電子工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

吉時(shí)利源表軟件在憶阻器測(cè)試中的應(yīng)用

TDK成功研發(fā)出用于神經(jīng)形態(tài)設(shè)備的自旋憶阻器

AI芯片的混合精度計(jì)算與靈活可擴(kuò)展

憶阻器誘導(dǎo)的超混沌、多渦旋和極端多穩(wěn)態(tài)小數(shù)階HNN:鏡像加密和FPGA實(shí)現(xiàn)

我們?cè)跍y(cè)試憶阻器時(shí)到底在測(cè)試什么?#憶阻器 #類腦計(jì)算 #存算一體 #芯片 #GPU

憶阻器通向計(jì)算新未來,自旋憶阻器進(jìn)一步降低能耗

risc-v多核芯片在AI方面的應(yīng)用

如何利用憶阻器技術(shù)改變高精度的科學(xué)計(jì)算

AI時(shí)代,憶恒創(chuàng)源如何定義SSD?

基于VO2憶阻器的無線物聯(lián)網(wǎng)混合系統(tǒng)

知合計(jì)算完成數(shù)億元融資,致力于研發(fā)高性能通用可擴(kuò)展處理器

英特爾專家為您揭秘第五代英特爾? 至強(qiáng)? 可擴(kuò)展處理器如何為AI加速

第五代英特爾至強(qiáng)可擴(kuò)展處理器,為AI加速而生

清華大學(xué)研究小組開發(fā)出了創(chuàng)新性的超分子憶阻器納米R(shí)RAM

神奇的混合憶阻器AI芯片可擴(kuò)展

神奇的混合憶阻器AI芯片可擴(kuò)展

評(píng)論