上一篇文章時鐘分頻系列——偶數分頻/奇數分頻/分數分頻,IC君介紹了各種分頻器的設計原理,其中分數分頻器較為復雜,這一篇文章IC君再跟大家聊聊分數分頻的具體設計實現。

一個分數分頻器由兩部分組成:以ZN和ZN+1為分頻系數的多路分頻器,還有一個ACC計數器。

1ZN/ZN+1分頻器設計

ZN/ZN+1分頻器的設計包含了偶分頻器和奇分頻器,首先定義ZN/ZN+1分頻器的模塊名字MDIV。 下圖是MDIV的引腳信號的名字,及功能定義:

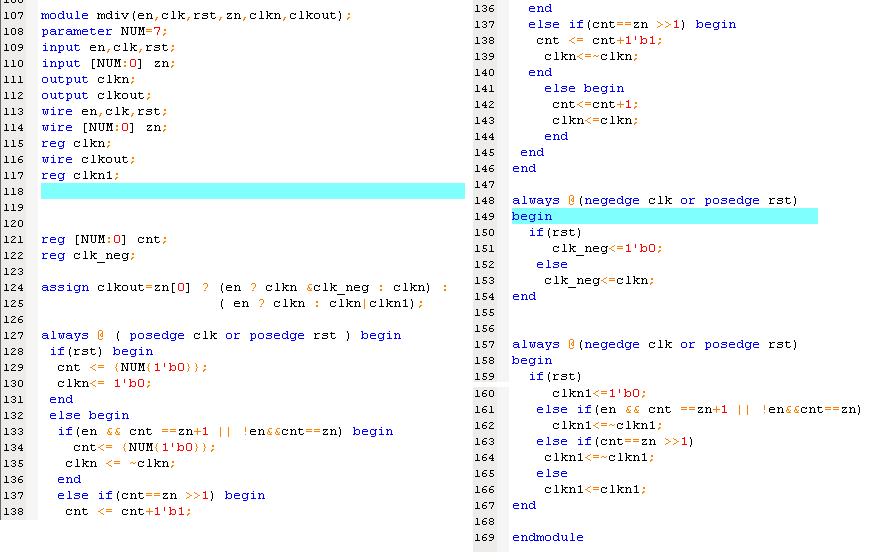

廢話不多說,Verilog硬件描述語言實現MDIV的代碼如下:

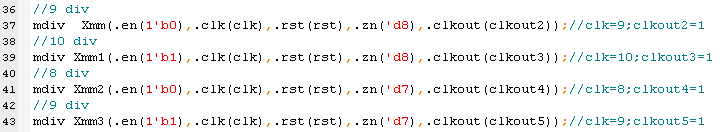

MDIV調用方法如下:

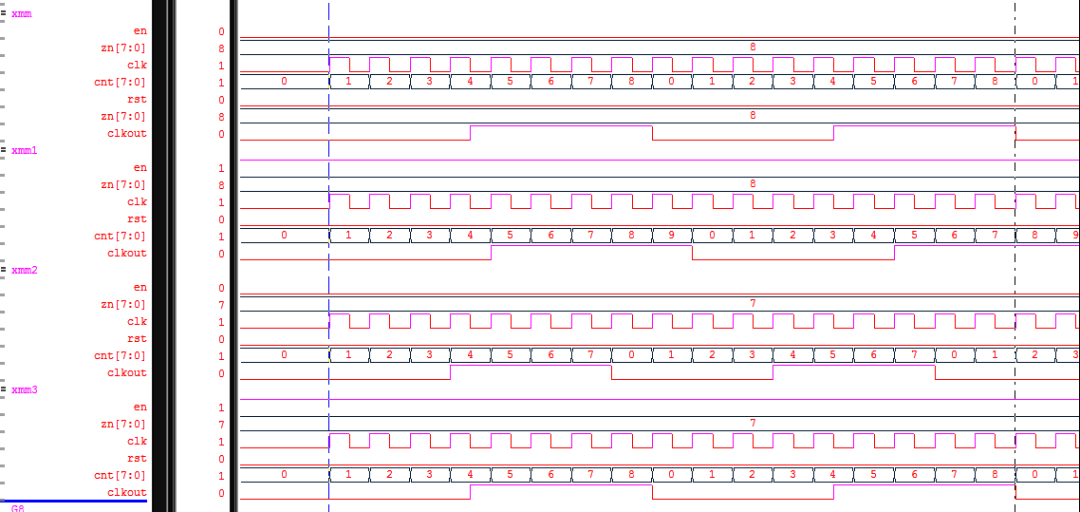

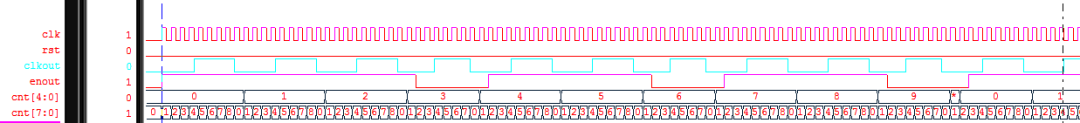

具體的仿真波形如下所示:

2ACC計數器設計

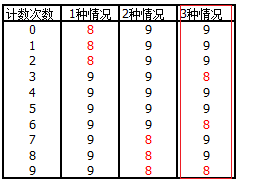

ACC計數器就是控制做N次ZN分頻和M次ZN+1次分頻,具體控制過程可以分為以下幾種情況:

第1種情況 :先做N次ZN分頻,再做M次ZN+1次分頻;

第2種情況: 先做M次ZN+1次分頻,再做N次ZN分頻;

第3種情況 :把N次ZN分頻平均插入到M次ZN+1分頻中;

第4種情況 :把M次ZN+1次分頻平均插入到N次ZN分頻中。

組合N次ZN分頻和M次ZN+1次分頻的情況很多。 第1、2種情況前后時鐘頻率不太均勻,因此相位抖動比較大;

第3、4種情況前后時鐘頻率均勻性稍好,因此相位抖動會減小。

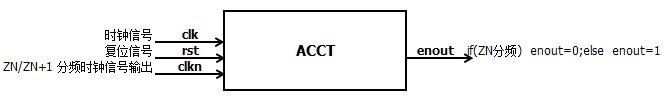

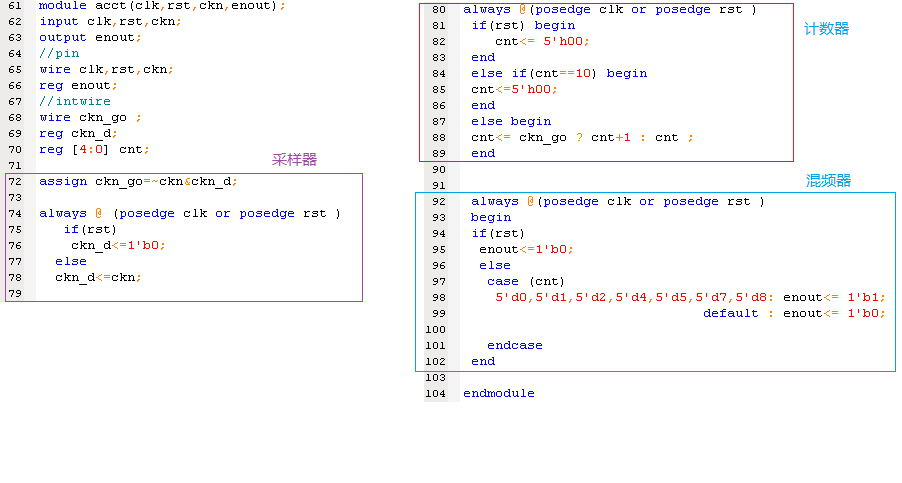

下面以8.7分頻為例子設計ACC計數器模塊名ACCT,下圖為模塊ACCT的引腳:

8.7分頻的原理是用3次8分頻和7次9分頻的對應的時鐘總時間來等效原時鐘87個周期的總時間。

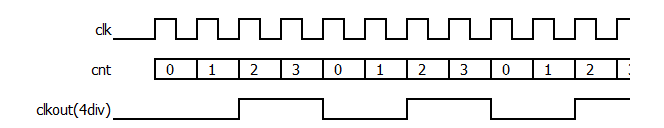

下圖選用前面所述的第3種情況,把3次8分頻平均地插入到7次9分頻中,這個過程也叫混頻。

采用第3種情況設計ACCT的Verilog代碼代碼如下所示:

代碼的92-102行就是第3種情況混頻,修改98行的數字可以得到不同的混頻。

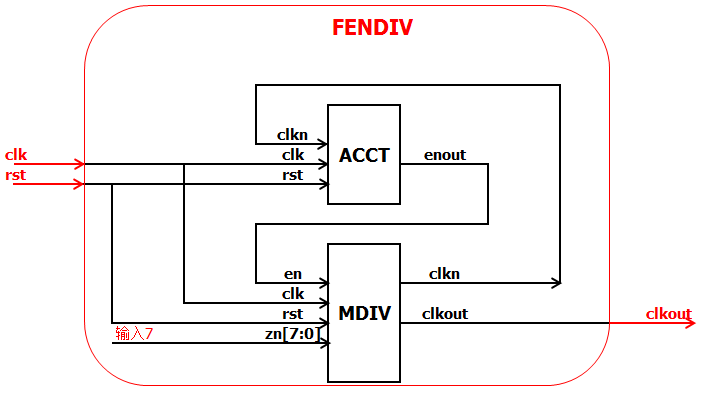

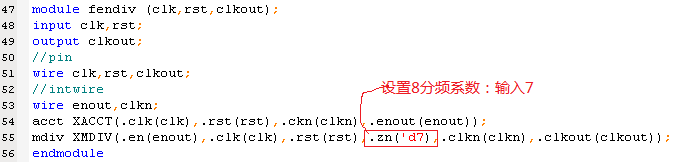

38.7分頻器設計

完成了模塊MDIV 和ACCT之后,就可以用組成一個8.7分頻器,這個分頻器的模塊名是FENDIV,框圖如下所示:

Verilog代碼如下:

最終生成的clkout波形如下所示:

有興趣的可以試試用MDIV 和ACCT設計一個10.3分頻器?

-

電路設計

+關注

關注

6637文章

2398瀏覽量

201167 -

分頻器

+關注

關注

43文章

445瀏覽量

49587 -

Verilog

+關注

關注

28文章

1333瀏覽量

109721 -

計數器

+關注

關注

32文章

2241瀏覽量

93978 -

時鐘分頻

+關注

關注

0文章

4瀏覽量

5708

發布評論請先 登錄

相關推薦

奇數分頻如何得到呢? 解讀奇數分頻和邏輯分析儀(ILA)的使用

基于Verilog的FPGA分頻設計

分頻器的作用是什么 半整數分頻器原理圖分析

偶數分頻/奇數分頻/分數分頻詳解

基于Verilog的分數分頻電路設計

基于Verilog的分數分頻電路設計

評論