1

概述

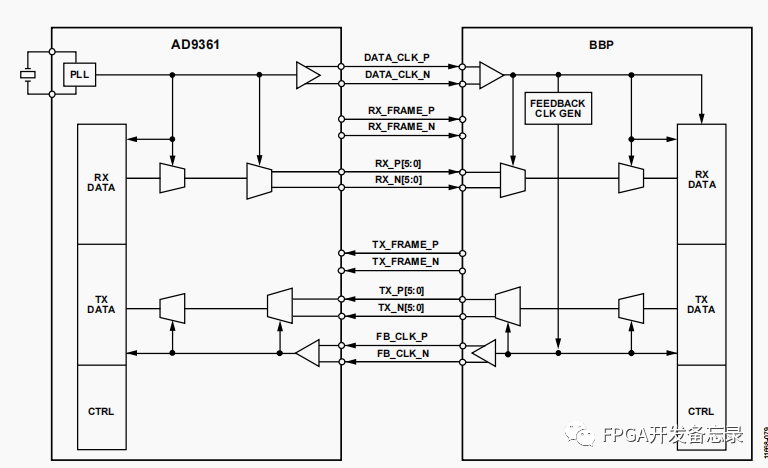

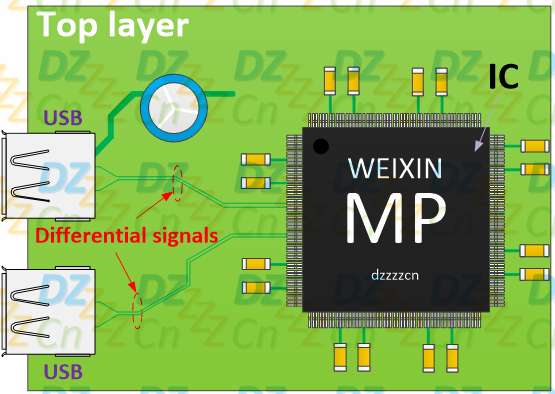

接下來將介紹AD9361數據路徑在低電壓差分信號(LVDS)模式下運行。AD9361數據接口使用并行總線(P0和P1)在AD9361和BBP之間傳輸數據樣本。這個總線傳輸使用簡單的硬件握手信號進行控制。在LVDS模式,兩個總線都與差分LVDS信令一起使用。9361的LVDS接口有助于連接到具有LVDS能力的自定義的ASIC和FPGA。

當一個系統需要在噪聲環境中有優越的交換性能和高于CMOS標準接口能提供的更高的傳輸速率時,通常會選用LVDS接口。當使用LVDS接口時,建議所有的的路徑長度不超過12英寸以及保持差分路徑緊挨著且等長。下面是LVDS模式下的數據路徑。

2

LVDS接口模式下的數據路徑信號

數據路徑接口由下面這些信號組成。

2.1

數據時鐘(DATA_CLK)

DATA_CLK是由9361產生的差分信號并提供給BBP為RX數據路徑提高主時鐘。BBP使用主時鐘作為數據樣本的基帶處理和接口的數據傳輸的時序參考。DATA_CLK在接收操作時為RX_D[5:0]提供了具有DDR操作的源同步定時。SDR在LVDS模式無效。

DATA_CLK的頻率取決于系統架構(包括射頻通道,過采樣程度以及帶寬(BW)模式)。頻率通過SPI接口寫入到AD9361。

DATA_CLK可以被AD9361停止(以響應來自BBP的項目)在接口空閑期間減少電力消耗。如果沒有使能DATA_CLK,從 nontoggling狀態的切換必須符合電力層對對clean信號轉換的需求,且valid層始終由AD9361驅動。

2.2

FB_CLK

FB_CLK是由BBP驅動的差分LVDS信號,是DATA_CLK反饋的一個信號。FB_CLK為TX_D[5:0]在Tx bursts期間提供了具有雙邊沿捕獲的源同步定時。

FB_CLK在空閑期間可被BBP停止,以此來減少電能消耗。假如這樣的話,從 nontoggling狀態的切換必須符合電力層對對clean信號轉換的需求,且valid層始終由BBP驅動。

2.3

RX_FRAME

RX_FRAME是由AD9361驅動的差分LVDS信號,送到BBP 作為9361提供的數據采樣的幀信號。切換到高時指示幀信號的開始。RX_FRAME在突發傳輸開始時可以被設置為一個單一的到高的變遷,在整個突發傳輸中保持高,或者也可以設置為每個幀信號開始都有一個上升沿的脈沖序列(占空比為50%)

2.4

RX_D[5:0]

RX_D[5:0]是由6個差分對組成的差分LVDS數據總線。它由9361驅動送到接收數據的BBP。數據以數據字對在總線上傳輸,創建了12bit的數據總線。

2.5

RX_FRAME

TX_FRAME是由BBP驅動的差分LVDS信號,供給9361作為由BBP提供的數據采樣的幀信號。切換到高時指示幀信號的開始。Tx_FRAME可以接受在突發傳輸開始時的一個到高信號的切換,在整個突發中保持高,或者在每幀開始時有上升邊緣的脈沖序列(50%占空比)

AD9361一直傳輸空數據(全為0)直到第一個TX_FRAME信號指示有效數據。當Tx路徑在FDD獨立模式下完成一次傳輸操作時并且數據路徑沒有自動刷新時,這將是一個有用的特征。在這種情況下TX_FRAME將會維持低電平來完成數據刷新操作。更多細節參考狀態機使能部分。

注意:RX_FRAME和TX_FRAME都是接口正常工作所必須要的信號。

2.6

TX_D[5:0]

TX_D[5:0]是由6個差分對組成的差分LVDS信號。它由BBP驅動送到9361,數據由發射器輸出。數據以數據字對在總線上傳輸,創建了12bit的數據總線。

2.7

ENABLE

ENABLE是由BBP驅動到9361,在TDD模式提供數據突發傳輸控制(與TXNRX)。BBP提供的ENABLE信號至少觸發一個DATA_CLK周期,以指示每個突發的開始,隨后第二次也至少觸發一個DATA_CLK周期來指示突發傳輸結束。AD9361在內部跟蹤ENABLE脈沖的序列,以正確地解釋每個脈沖是每個突發傳輸的開始還是結束。ENABLE信號也能配置為電平模式,其中信號的狀態(而不是脈沖)決定ENSM何時在狀態之間移動。

在LVDS模式,該端口一直為有效狀態(高電平)。在TDD模式,BBP和9361都忽略了inactive方向上的數據。開始和結束延遲(由AD9361采樣的ENABLE脈沖與總線上第一和最后一個有效數據采樣之間)取決于數據路徑配置的不同。Rx_FRAME和Tx_FRAME信號分別由BBP和AD9361用來確定有效數據。FB_CLK信號用于對輸入進行采樣。

在FDD模式下,ENABLE信號作為單個控制輸入來確定ENSM的狀態.還有一種替代的FDD模式,其中ENABLE信號可以重新定義為RxON,控制Rx功能的ENSM直接由硬件輸入來控制。該模式稱為FDD獨立控制模式,BBP獨立地控制RX功能,這樣可以節省能源消耗。

2.8

TXNRX

TXNRX是由BBP驅動到9361,當ENSM在TDD模式時提供數據突發傳輸控制(與ENABLE)。當ENABLE被AD9361采樣為高時開始一個突發時,TXNRX上的電平也會被采樣來確定數據的方向。在TDD模式,TXNRX采樣為高指示發送數據,采樣為低電平指示接收突發傳輸。

TXNRX電平信號必須維持在整個數據突發傳輸(以一個有效的電平邏輯)。在采樣ENABLE啟動脈沖之前,TXNRX信號可以建立任意數目的周期(≥0),在采樣ENABLE完成脈沖后,也可以改變任意次數的周期(≥0)。需要注意的是,TXNRX信號應該只在ENSM處于ALERT狀態時改變狀態,因為TXNRX上升和下降邊緣在TDD模式下直接開關相應的合成器。

在正常的FDD模式下,TXNRX信號將被忽略,但必須保持在一個有效的邏輯電平。也有一種可替換的FDD模式,TXNRX信號可被重定義為TxON,直接的硬件輸入到ENSM來控制TX功能。在FDD獨立控制模式,BBP獨立地控制TX功能,這樣可節省消能源耗。

3

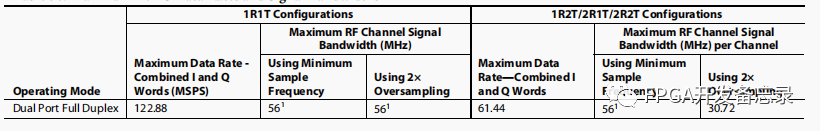

LVDS最大時鐘速率和信號帶寬

下表中列出的數據比較了LVDS數據總線配置在不同允許的工作模式下的最大數據時鐘速率和信號帶寬。列出了以下兩種情況下的最大射頻帶寬:使用避免混疊的最小采樣率進行采樣,使用避免混疊的最小采樣率進行采樣,采樣采用兩倍的過采樣。每種模式的細節將在后面的章節中給出。在LVDS模式下,最大DATA_CLK速率增加到245.76 MHz。該時鐘和56 MHz最大模擬濾波器帶寬限制了射頻信道信號帶寬。請注意,TDD和FDD模式的數據總線定時是相同的,因為每個路徑(傳輸和接收)都有一個專用的總線。

4

雙端口全雙工模式(LVDS)

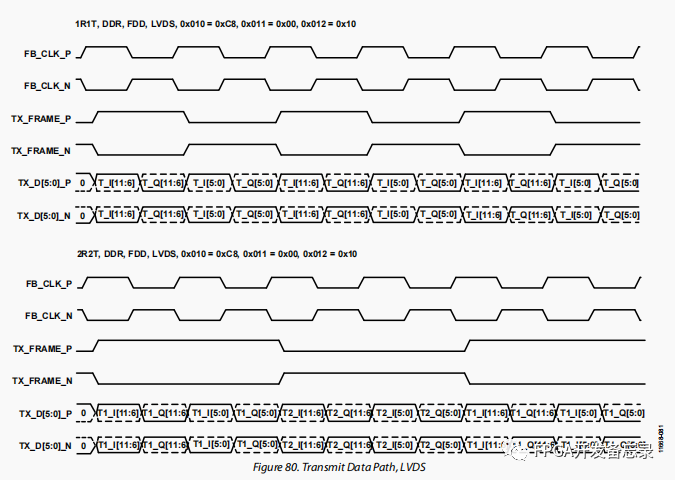

雙總線全雙工LVDS模式通過SPI寫寄存器使能,在這個模式,p0和p1都被作為LVDS信號,并且數據總線(D[11:0])被分割成單獨的子總線(Rx_D[5:0]和Tx_D[5:0])。每個子總線同時運行,允許在BBP和AD9361之間進行全雙工傳輸和接收數據。傳輸數據(Tx_D[5:0])、FB_CLK和Tx_FRAME是由BBP驅動的,這樣在FB_CLK、Tx_D[5:0]和Tx_FRAME之間的建立和保持時間允許AD9361使用FB_CLK捕獲Tx_D[5:0]和Tx_FRAME。

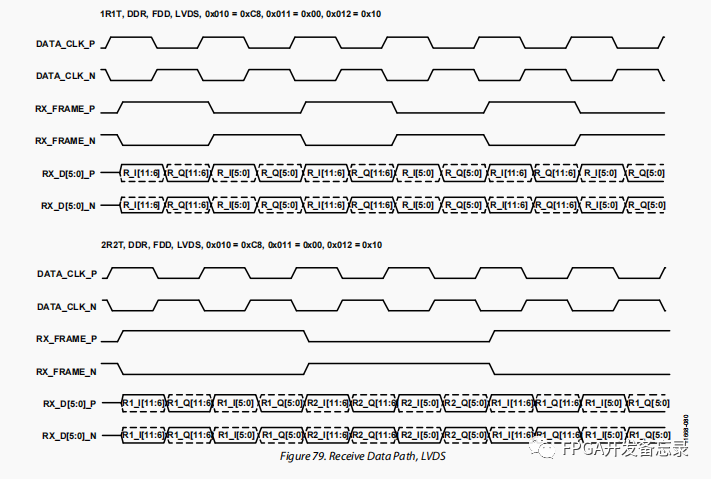

Tx_D[5:0]總線上的數據采樣由Tx_FRAME信號構成,如時序圖所示。傳輸數據樣本以兩個數據包的補體格式攜帶,每個數據包中的第一個6位字包含MSB,第二個6位字包含LSB。最大的正樣本值是0x7FF,第一個字是0x1F,第二個字是0x3F,最大負值是0x800,第一個字是0x20,第二個字是0x00。Tx_D[5]是最重要的位,而Tx_D[0]是每個字中最不重要的位。

接收數據(RX_D[5:0]),DATA_CLK和RX_FRAME由AD9361驅動,DATA_CLK,RX_D[5:0]和RX_FRAME之間的建立保持時間允許BBP使用DATA_CLK去捕捉RX_D[5:0]和RX_FRAME。RX_D[5:0]總線上的數據采樣由RX_FRAME組成,如時序圖所示。傳輸數據樣本以兩個數據包的補體格式攜帶,每個數據包中的第一個6位字包含MSB,第二個6位字包含LSB。最大的正樣本值是0x7FF,第一個字是0x1F,第二個字是0x3F,最大負值是0x800,第一個字是0x20,第二個字是0x00。Tx_D[5]是最重要的位,而Tx_D[0]是每個字中最不重要的位。

注意,在CMOS模式下,FB_CLK必須由DATA_CLK生成,以便保持相同的頻率和占空比。這兩個時鐘信號之間沒有相位關系的要求。

如前所述,I和Q數據采樣在每個數據總線上進行時間交錯。對于1R1T系統,I和Q采樣以4路交錯的方式攜帶:IMSB, QMSB, ILSB, QLSB, …在這種情況下,Tx_FRAME和Rx_FRAME信號與數據切換相一致。當啟用50%占空比框架時,高狀態時是IMSB和QMSB,低狀態時是Ilsb和QLSB,然后,這些信號再次用IMSB調高,以指示新幀的開始。

對于2R2T系統,來自RF路徑1和路徑2的I和Q樣本以8種方式交錯攜帶:I1 MSB, Q1 MSB, I1 LSB, Q1 LSB, I2 MSB, Q2 MSB, I2 LSB, Q2 LSB, …在這種情況下,Tx_FRAME和Rx_FRAME信號與數據切換相一致。當啟用50%占空比框架,高狀態時是I1 LSB, Q1 LSB, I2 MSB, Q2 MSB,低狀態時是 I2 MSB, Q2 MSB, I2 LSB, Q2 LSB.然后,這些信號再次用IMSB調高,以指示新幀的開始。

對于2R1T或1R2T配置的系統,時鐘頻率、總線傳輸速率和采樣周期以及數據捕獲時序與2R2T的系統的配置相同。

然而,在只使用一個通道的路徑中,每個數據組中的禁用通道的I-Q對都未使用。這些未使用的IQ對將會被9361所忽略。例如,2R1T系統使用TX通道1,突發發送將會有4個未使用的slot:I1 MSB, Q1 MSB, I1 LSB, Q1 LSB, X, X, X, X, …在這種情況下,Tx_FRAME和Rx_FRAME與數據切換一致,高電平代表I1MSB, Q1MSB, I1LSB, Q1LSB,而低電平代表未使用的slot。這些信號再次用I1LSB切換高,以指示新幀的開始。未使用的Xslot可以由BBP填充任意的數據值

這些值可以是常量值,也可以重復前面的數據樣本值,以降低總線切換點,從而降低功耗。

5

數據路徑功能時序(LVDS)

圖79和圖80中的時序圖說明了雙端口FDD LVDS模式下總線信號之間的關系。時序圖中的差分數據用實線和虛線繪制,以說明數據線的差分性質。

請注意,由于2R1T和1R2T系統遵循2R2T時序圖,因此在圖79和圖80中省略了它們。

LVDS 模式中不支持以下bit:

-交換端口—在LVDS模式下,P0為Tx,P1為Rx。

無法更改此配置.

-單端口模式—兩個端口都在LVDS模式下啟用。

-FDD Full端口—在LVDS中不支持。

-FDD Alt Word Order—在LVDS中不支持。

-FDD交換bit—在LVDS中不支持。

-

CMOS

+關注

關注

58文章

5680瀏覽量

235137 -

差分信號

+關注

關注

3文章

367瀏覽量

27649 -

lvds接口

+關注

關注

1文章

128瀏覽量

17386 -

FPGA開發

+關注

關注

1文章

43瀏覽量

14891 -

AD9361

+關注

關注

8文章

34瀏覽量

37070

發布評論請先 登錄

相關推薦

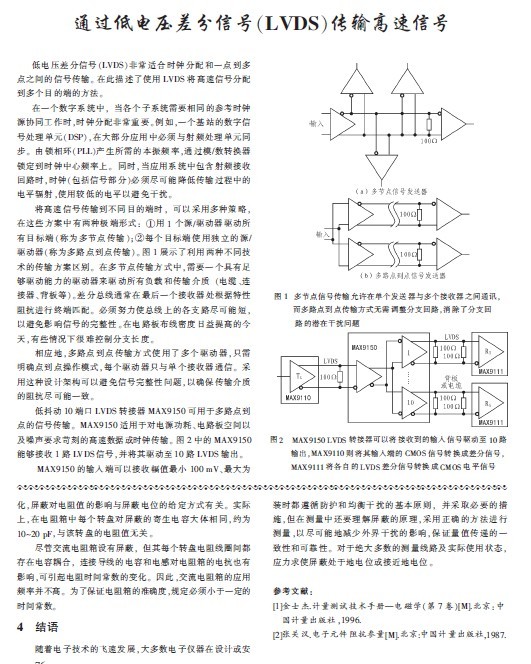

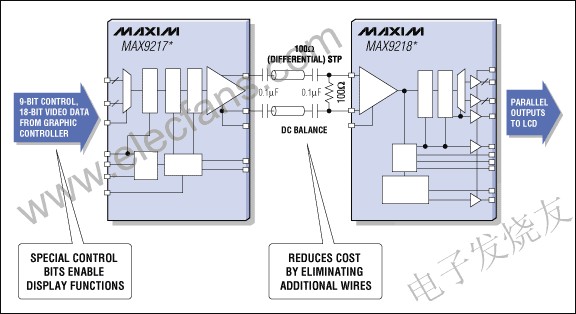

通過低電壓差分信號(LVDS)傳輸高速信號

通過低電壓差分信號(LVDS)傳輸高速信號

一文詳解LVDS低電壓差分信號

AD9361數據路徑在低電壓差分信號(LVDS)模式下運行

AD9361數據路徑在低電壓差分信號(LVDS)模式下運行

評論