FPGA之三八譯碼器

一聽到三八譯碼器這個東西可能會感覺有點熟悉,其實在STC89C51系列單片機中,里面就有一個三八譯碼器,就是一開始的流水燈程序,LED0-7這八個LED!但是怎么在FPGA中實現三八譯碼器呢?其實很簡單。

1、創(chuàng)建好工程,像上一篇文章那樣,我就不多說了,忘記的同學可以到下面這個網址查看,

https://blog.csdn.net/Jiang_YW/article/details/89220995

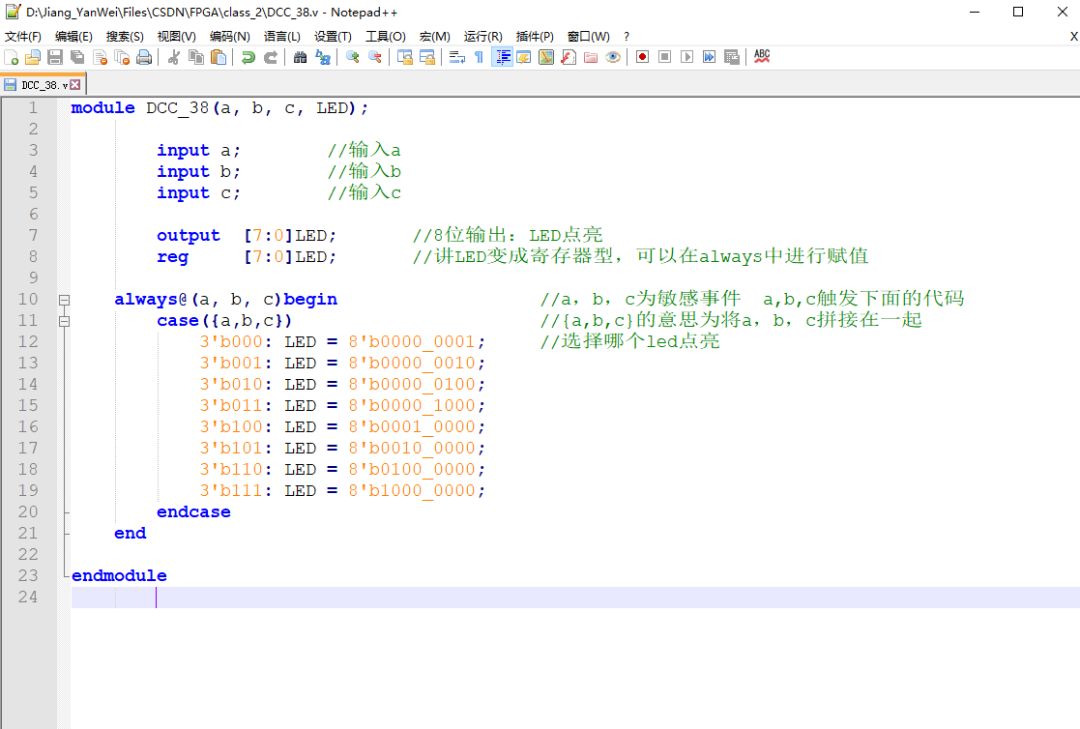

2、創(chuàng)建好工程以后,再新建一個Verilog HDL文件,我命名為DCC_38.v,然后把文件添加到工程里面。

建議新手先學一下Verilog HDL語法,不然對這些內容會看不懂,Verilog相對于VHDL要簡單,而且看起來要更相似與C語言,學過C的話,再學Verilog會簡單一點點。

推薦網址:https://www.cnblogs.com/SYoong/p/5849168.html

有好幾個章節(jié),有興趣的的同學可以學學。

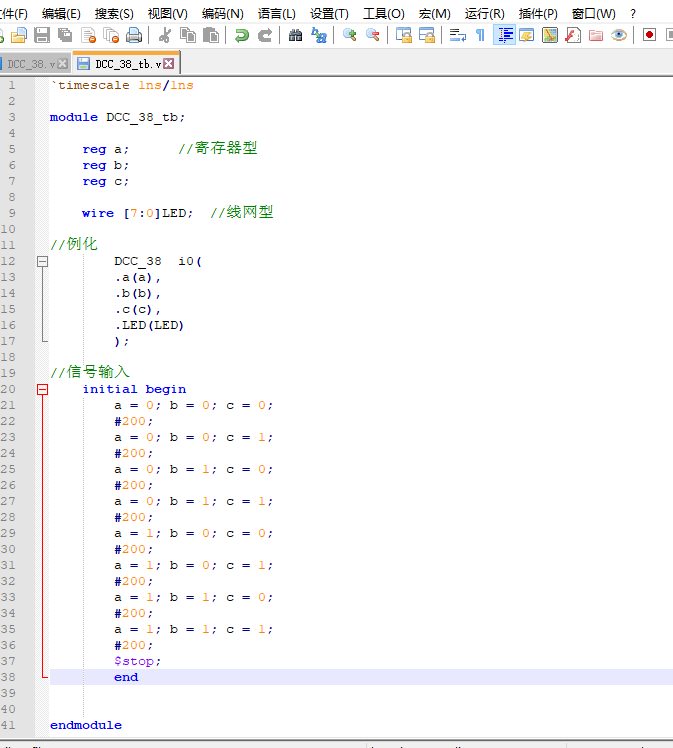

3、把上面工程編譯一遍沒錯之后,就可以開始寫tb(testbench)文件了,再新建一個DCC_38_tb.v文件,編寫激勵程序。

寫完之后也添加到盡快工程里面進行編譯。

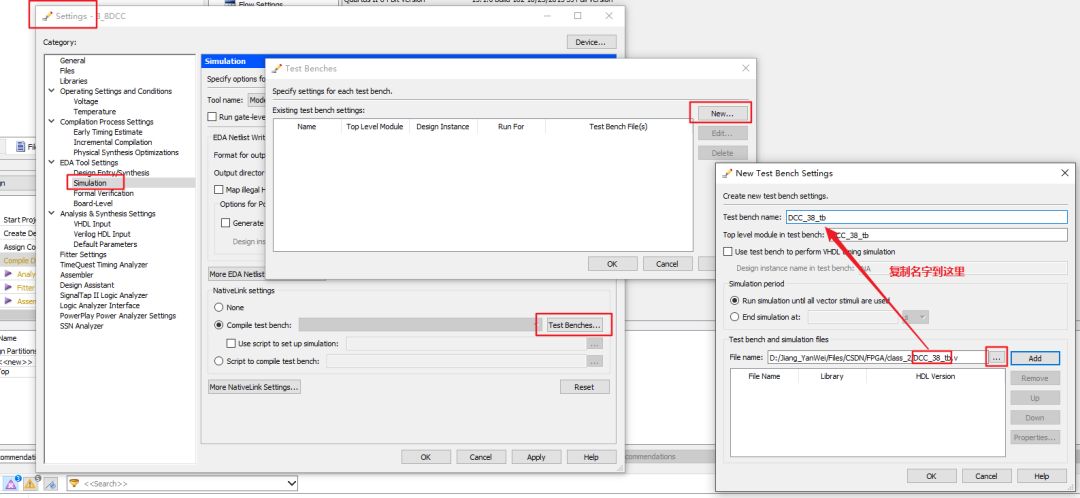

4、點擊Assignment → Setting

按上圖操作完成之后,點擊add跟OK,保存好即可。

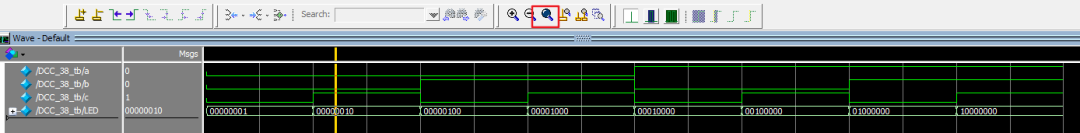

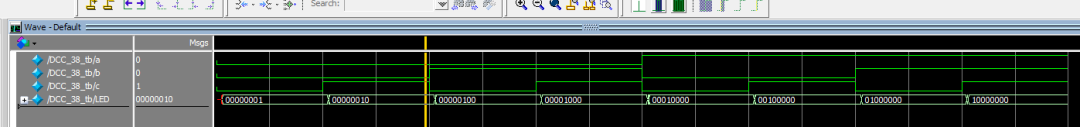

一開始沒仿真圖出來,點擊上面紅色框的黑色放大鏡即可。

由上圖可見仿真沒有錯誤,那么就先關閉ModuleSim。

6、然后點擊Gate Level Simulation進行后仿真,點擊Run。操作與上圖一樣

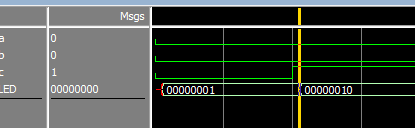

在圖里可以看見LED的輸出有一點點的延遲,這是正常現象。

為什么這一瞬間LED的值會為零呢?

實際上是芯片0000_0001→0000_0000 → 0000_0010進行了兩次的反轉,其他的也一樣。

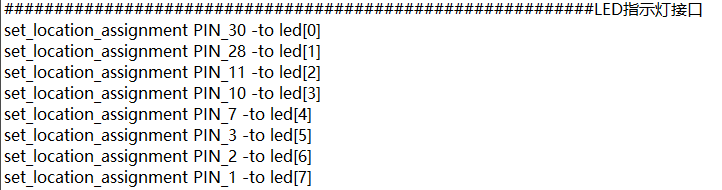

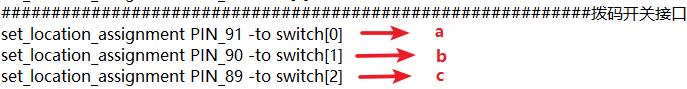

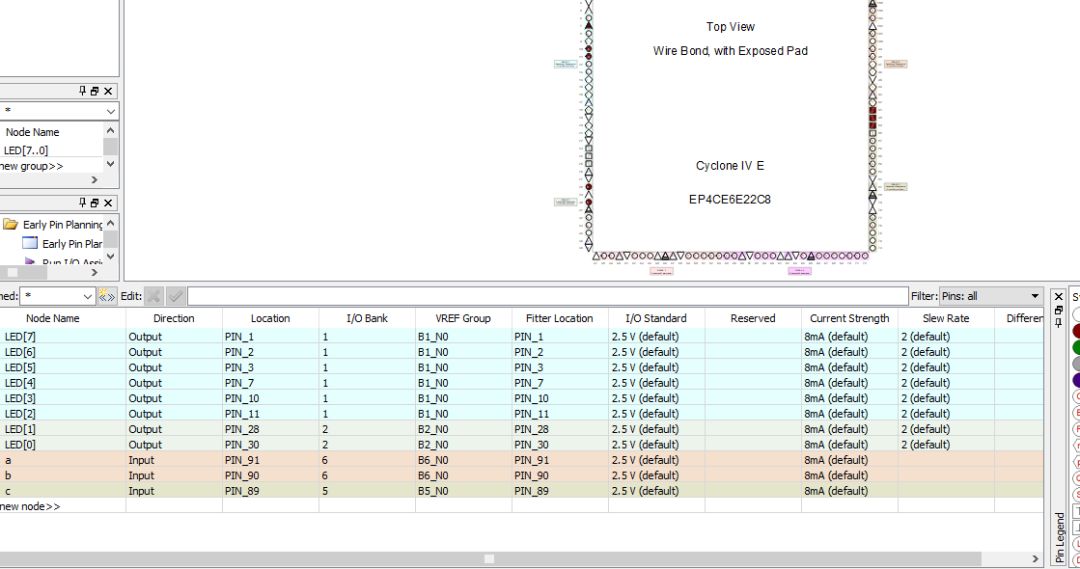

7、點擊Pin Planner,參考引腳配置,進行引腳分配

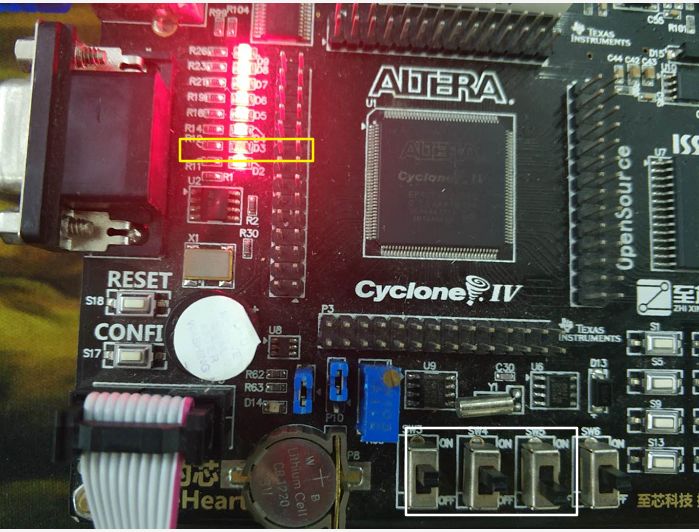

8、再編譯一遍程序,就可以燒錄到板子里面。

上圖只看左邊三個開關,第四個忽略

程序ok。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602006 -

單片機

+關注

關注

6032文章

44525瀏覽量

633256 -

譯碼器

+關注

關注

4文章

310瀏覽量

50285 -

STC

+關注

關注

14文章

299瀏覽量

66126

發(fā)布評論請先 登錄

相關推薦

怎么實現BCH譯碼器的FPGA硬件設計?

三八譯碼器的應用

三八譯碼器的相關資料推薦

基于FPGA的高速RS編譯碼器實現

基于FPGA的RS碼譯碼器的設計

基于FPGA 的LDPC 碼編譯碼器聯合設計

譯碼器的邏輯功能_譯碼器的作用及工作原理

譯碼器的分類和應用

通過采用FPGA器件設計一個Viterbi譯碼器

關于Actel 的FPGA的譯碼器的VHDL源代碼

FPGA之三八譯碼器

FPGA之三八譯碼器

評論