使用 NoC 可以大大簡(jiǎn)化 SoC的開發(fā),但這在很大程度上取決于誰(shuí)在開發(fā)NoC。

作者:Michael Frank and Frank Schirrmeister

除了簡(jiǎn)易的產(chǎn)品以外,幾乎所有的現(xiàn)代系統(tǒng)級(jí)芯片 (SoC) 設(shè)備都將利用片上網(wǎng)絡(luò)(NoC) 來(lái)實(shí)現(xiàn)其片上通信。有些人質(zhì)疑是否有必要使用 NoC,或者采用更基本的方法是否能足夠滿足需要。

Part.1

SoC中有什么?

SoC 是一種集成電路(IC),它集成了計(jì)算機(jī)或其他電子系統(tǒng)的大部分或全部組件。SoC 由稱為知識(shí)產(chǎn)權(quán)(IP) 模塊的多個(gè)功能單元組成。其中有許多模塊將來(lái)自第三方供應(yīng)商;剩下的部分- 那些提供“秘密武器”,將此SoC與競(jìng)爭(zhēng)產(chǎn)品區(qū)分開來(lái) - 將由自己內(nèi)部開發(fā)創(chuàng)建。

這些 IP 模塊可以包括處理器內(nèi)核,如微處理器單元(MPU)、圖形處理單元(GPU) 和神經(jīng)處理單元(NPU)。除了各種類型的存儲(chǔ)器 IP 外,其他 IP 模塊還可以執(zhí)行通信、實(shí)用程序、外設(shè)和加速功能。

Part.2

總線、Crossbar Switch和NoC

每個(gè) IP 塊都表示在系統(tǒng)內(nèi)存空間中的某個(gè)位置。術(shù)語(yǔ)“事務(wù)”(transaction) 是指從系統(tǒng)內(nèi)存空間的地址中寫入或讀取數(shù)據(jù)字節(jié)的操作。為了使SoC發(fā)揮其魔力,IP塊需使用事務(wù)通過(guò)某種形式的互連來(lái)相互“交談”。術(shù)語(yǔ)“啟動(dòng)器”(initiator) 和“目標(biāo)”(target) 是指生成或響應(yīng)事務(wù)的 IP 塊。

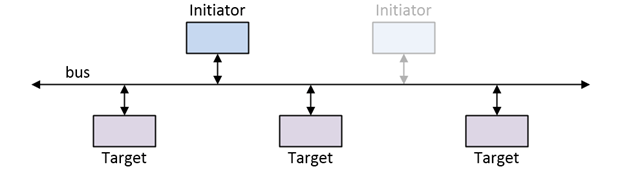

1990年代SoC上使用的主要互連機(jī)制是總線(bus)。高度簡(jiǎn)化的表示如圖 1 所示。請(qǐng)注意,標(biāo)記為“總線”的線路將包括多條實(shí)現(xiàn)數(shù)據(jù)總線、地址總線和相關(guān)控制信號(hào)的線路。

圖 1:簡(jiǎn)化的總線互連結(jié)構(gòu)

在許多早期的SoC設(shè)計(jì)中,只有一個(gè)中央處理器(CPU) 形式的啟動(dòng)器IP塊。當(dāng)啟動(dòng)器在地址總線上放置一個(gè)地址時(shí),所有的目標(biāo) IP 塊都會(huì)看到它,其中一個(gè)會(huì)對(duì)自己說(shuō):“這是我”。當(dāng)啟動(dòng)器隨后發(fā)出讀取命令時(shí),或者當(dāng)它將數(shù)據(jù)放在數(shù)據(jù)總線上并發(fā)出寫命令時(shí),相應(yīng)的目標(biāo)將做出響應(yīng)。

有一些早期的 SoC 可能會(huì)使用多個(gè)啟動(dòng)器。例如,CPU 可能附帶直接內(nèi)存訪問(wèn) (DMA)功能,該功能可用于在不同內(nèi)存區(qū)域和外圍設(shè)備之間快速傳輸大型數(shù)據(jù)塊。隨著設(shè)計(jì)中啟動(dòng)器數(shù)量的增加,有必要實(shí)施某種形式的仲裁方案,允許它們協(xié)商總線的控制。

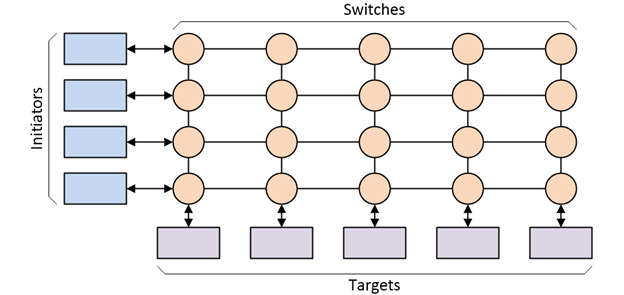

在 2000 年代初期,隨著 SoC 設(shè)計(jì)變得越來(lái)越復(fù)雜(包含越來(lái)越多的 IP 模塊并采用多個(gè)啟動(dòng)器),使用基于 crossbar switch交叉開關(guān)的互連架構(gòu)變得很普遍(圖2)。同樣,此圖中的每一條線代表一條包含數(shù)據(jù)、地址和控制信號(hào)的多線總線。

在 2000 年代初期,隨著 SoC 設(shè)計(jì)變得越來(lái)越復(fù)雜(包含越來(lái)越多的 IP 模塊并采用多個(gè)啟動(dòng)器),使用基于 crossbar switch交叉開關(guān)的互連架構(gòu)變得很普遍(圖2)。同樣,此圖中的每一條線代表一條包含數(shù)據(jù)、地址和控制信號(hào)的多線總線。

圖2: 簡(jiǎn)化的crossbar switch互連架構(gòu)

在這種情況下,任何啟動(dòng)器都可以與任何目標(biāo)通信。當(dāng)事務(wù)從啟動(dòng)器傳遞到目標(biāo)并再次返回時(shí),switch交叉開關(guān)對(duì)事務(wù)進(jìn)行路由,并且多個(gè)事務(wù)可以隨時(shí)在“進(jìn)行中”。每個(gè)switch都具有緩沖事務(wù)的能力,因此如果許多事務(wù)同時(shí)到達(dá),它可以決定哪個(gè)事務(wù)具有更高的優(yōu)先級(jí)。

SoC 設(shè)計(jì)的規(guī)模和復(fù)雜性持續(xù)增長(zhǎng)。大約在 1990 年代初期,SoC 可能只包含幾十個(gè) IP 模塊,整個(gè)設(shè)備可能只包含 20,000 到 50,000 個(gè)邏輯門和寄存器。相比之下,如今,SoC 可以包含數(shù)百個(gè) IP 模塊,每個(gè)模塊包含數(shù)十萬(wàn)甚至數(shù)百萬(wàn)個(gè)邏輯門和寄存器。

在同一時(shí)期,數(shù)據(jù)總線的寬度從8位增加到16位,32位,64位,甚至更高。事實(shí)上,目前數(shù)據(jù)傳輸?shù)牡湫痛笮∈?64 字節(jié)(512 位) 緩存行,這很快就會(huì)導(dǎo)致路由擁塞問(wèn)題。盡管硅芯片工藝的發(fā)展已經(jīng)使晶體管縮小了幾個(gè)數(shù)量級(jí),但由于芯片上導(dǎo)線的寬度沒(méi)有以同樣的速度減小,這些問(wèn)題變得更加嚴(yán)重。

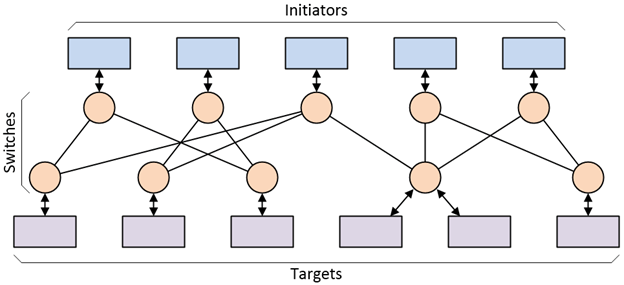

為了解決這些問(wèn)題,今天的設(shè)計(jì)人員采用了片上網(wǎng)絡(luò)(NoC) 的概念。圖 3 是一個(gè)簡(jiǎn)單的 NoC 示例。在這種情況下,事務(wù)就由傳遞的信息包承擔(dān)。每個(gè)數(shù)據(jù)包包含一個(gè)反映目標(biāo)地址的標(biāo)頭和一個(gè)包含數(shù)據(jù)、指令、請(qǐng)求類型等的正文。

圖3: 簡(jiǎn)化的片上網(wǎng)絡(luò)(NoC)互連架構(gòu)

多個(gè)信息包可以在任何特定時(shí)間“傳輸”,并且switch再次具有緩沖事務(wù)并確定事務(wù)優(yōu)先級(jí)的能力。由于每個(gè)啟動(dòng)器不需要能夠與每個(gè)目標(biāo)通信,這可以反映在架構(gòu)中,從而進(jìn)一步降低了互連要求。

Part.3

使用成品還是“自己動(dòng)手”?

從一個(gè)角度來(lái)看,使用 NoC很大程度上簡(jiǎn)化了 SoC 的設(shè)計(jì),但這在很大程度上取決于誰(shuí)在開發(fā) NoC。術(shù)語(yǔ)“套接字”(socket) 是指IP塊與NoC之間的物理接口(例如,數(shù)據(jù)寬度) 和通信協(xié)議。SoC行業(yè)已經(jīng)定義并采用了幾種socket協(xié)議(OCP,APB,AHB,AXI,STBus,DTL等)。

除了不同的數(shù)據(jù)寬度外,同一設(shè)計(jì)中的IP模塊可能以不同的頻率計(jì)時(shí)。由于 SoC 設(shè)計(jì)可能涉及數(shù)百個(gè) IP 塊,其中許多來(lái)自其他第三方供應(yīng)商,因此 IP 可能使用不同的socket協(xié)議。為了適應(yīng)這種多樣性,可能需要在啟動(dòng)器和目標(biāo)socket之間轉(zhuǎn)換事務(wù)。

支持多個(gè) SoC 項(xiàng)目的內(nèi)部 NoC 需要多個(gè)維度的可配置性和靈活性。因此,從頭開始開發(fā) NoC 可能與設(shè)計(jì) SoC 的其余部分一樣復(fù)雜和耗時(shí)。此外,開發(fā)人員現(xiàn)在有兩件事需要驗(yàn)證和調(diào)試 - NoC和設(shè)計(jì)的其余部分。

解決措施是使用現(xiàn)成的NoC解決方案,例如 Arteris的FlexNoC。在這種情況下,F(xiàn)lexNoC直觀的界面使設(shè)計(jì)人員能夠識(shí)別構(gòu)成架構(gòu)的IP模塊以及每個(gè)模塊的socket特性(寬度、協(xié)議、頻率等)。開發(fā)人員還可以指定哪些啟動(dòng)器需要與哪些目標(biāo)通信。此時(shí),生成NoC實(shí)際上是一個(gè)“按鈕”操作。

Part.4

SoC 到底有多復(fù)雜?

回到SoC設(shè)計(jì)何時(shí)需要片上網(wǎng)絡(luò)的問(wèn)題。直覺的答案可能是較小的設(shè)計(jì)可能被豁免。但是,在最近與Semico Research的Rich Wawrzyniak的討論中,他證實(shí)我們已經(jīng)在客戶那里看到的情況是:即使在工業(yè)和物聯(lián)網(wǎng)領(lǐng)域的較小設(shè)計(jì)中,用戶也經(jīng)常面臨數(shù)十到數(shù)百個(gè)不得不組裝和協(xié)調(diào)的IP塊。

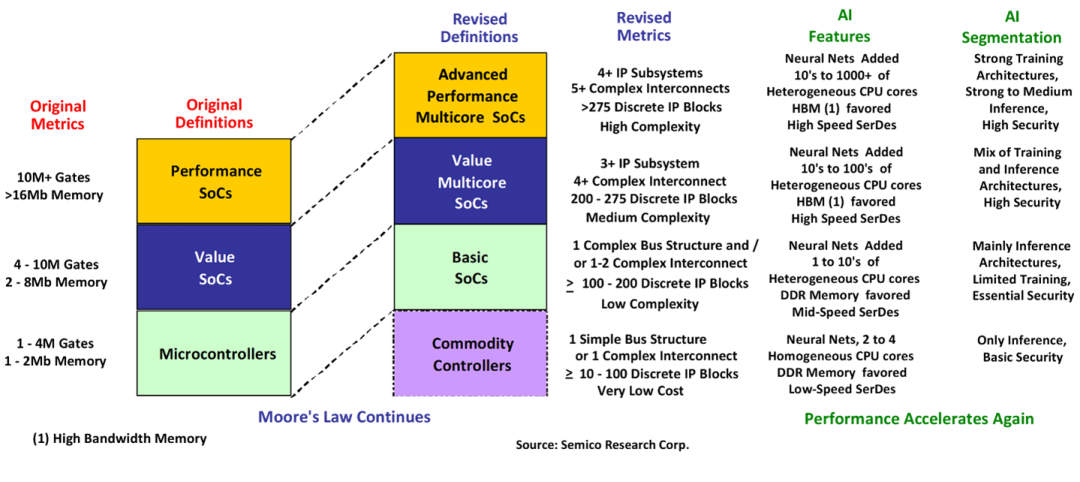

如圖 4 所示,Semico 定義了四類 SoC。其中三種- 具有100-200個(gè)離散模塊和1+互連的基本SoC,具有200-275個(gè)模塊和4+復(fù)雜互連的特定價(jià)值多核SoC,以及具有>275模塊和5+復(fù)雜互連的高性能SoC - 是NoC自動(dòng)化的明確靶心目標(biāo)。但是除此之外,即使是較簡(jiǎn)單的商用控制器,設(shè)計(jì)人員也要面臨著10到100個(gè)需要交互的離散模塊。

對(duì)于較小的設(shè)計(jì),工程師傾向于“自己做NoC”。但通常情況下,他們很快就會(huì)意識(shí)到:他們應(yīng)該打電話給Arteris來(lái)利用NoC自動(dòng)化。

圖4: Semico根據(jù)復(fù)雜性將SoC分為四類

+

結(jié)論

在本專欄的開頭,提出了“我的SoC設(shè)計(jì)何時(shí)需要NoC?”的問(wèn)題。簡(jiǎn)單的答案是,當(dāng)今日益復(fù)雜的SoC設(shè)計(jì)始終需要一個(gè)NoC來(lái)優(yōu)化實(shí)現(xiàn)出色路由和性能目標(biāo)。實(shí)施前衛(wèi)的NoC的簡(jiǎn)單方法是使用Arteris的FlexNoC 。

關(guān)于 Arteris

Arteris是系統(tǒng)IP的先進(jìn)提供商,包括 片上網(wǎng)絡(luò)(NoC) 互連 IP 和 IP 部署技術(shù)兩部分,可加速各種電子產(chǎn)品的系統(tǒng)級(jí)芯片(SoC)半導(dǎo)體開發(fā)和集成。垂直應(yīng)用包括汽車、移動(dòng)、消費(fèi)電子、企業(yè)數(shù)據(jù)中心、5G 通信、工業(yè)和物聯(lián)網(wǎng),利用 AI/ML 等技術(shù)和功能安全為寶馬、博世、百度、 Mobileye、三星、東芝和恩智浦等客戶提供服務(wù)。Arteris IP產(chǎn)品包括FlexNoC互連IP,Ncore緩存一致性IP,CodaCache獨(dú)立末級(jí)緩存,ISO 26262 安全,人工智能,自動(dòng)時(shí)序收斂和Magillem SoC 組裝自動(dòng)化。Arteris IP 產(chǎn)品可以幫助客戶提升性能、降低功耗和面積、提高設(shè)計(jì)復(fù)用效率、加快 SoC 開發(fā)速度,從而降低開發(fā)和生產(chǎn)成本。

審核編輯 :李倩

-

模塊

+關(guān)注

關(guān)注

7文章

2673瀏覽量

47347 -

soc

+關(guān)注

關(guān)注

38文章

4122瀏覽量

217955 -

啟動(dòng)器

+關(guān)注

關(guān)注

0文章

60瀏覽量

13147

原文標(biāo)題:我的SoC設(shè)計(jì)何時(shí)需要NoC?

文章出處:【微信號(hào):ArterisIP,微信公眾號(hào):ArterisIP】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺(tái)之PL通過(guò)NoC讀寫DDR4實(shí)驗(yàn)(4)

NoC DDRMC LPDDR4上運(yùn)行AMD Versal? Adaptive SoC DCMAC設(shè)計(jì)示例

技術(shù)文章:如何利用NoC來(lái)進(jìn)行FPGA內(nèi)部邏輯的互連

利用NoC資源解決FPGA內(nèi)部數(shù)據(jù)交換的瓶頸

如何利用NoC資源去支撐FPGA中的創(chuàng)新設(shè)計(jì)

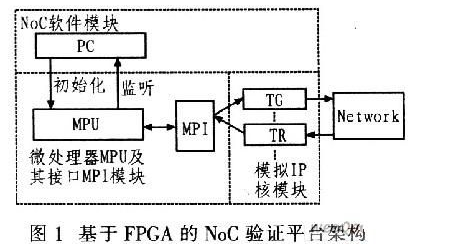

怎么構(gòu)建一種基于FPGA的NoC驗(yàn)證平臺(tái)?

NoC是什么?NoC有哪些技術(shù)優(yōu)勢(shì)?

采用FPGA的NoC驗(yàn)證平臺(tái)實(shí)現(xiàn)方案

你不看,我不看,冷知識(shí)何時(shí)能變燙

SoC中有什么?SoC到底有多復(fù)雜?

從SoC到NoC:芯片架構(gòu)的演進(jìn)與變革

?SoC設(shè)計(jì):NoC 配置和實(shí)施流程

AMD Versal系列FPGA NoC介紹及實(shí)戰(zhàn)

AMD Versal系列FPGA NoC介紹及實(shí)戰(zhàn)

傳智驛芯聯(lián)手Arteris,利用創(chuàng)新NoC技術(shù)駕馭復(fù)雜SoC設(shè)計(jì)

我的SoC設(shè)計(jì)何時(shí)需要NoC?

我的SoC設(shè)計(jì)何時(shí)需要NoC?

評(píng)論