高頻高速電子產品的快速發展需要PCB具有高性能的系統結構,而不僅是有支撐作用的電子元器件。目前的電子系統設計普遍信號頻率高于100 MHz,用來進行信號傳輸的高頻高速印刷電路板也越來越容易受到信號完整性問題的影響。信號傳輸過程更容易出現反射、串擾等信號完整性問題,且頻率越高、傳輸速率越快,信號損耗越嚴重,如何降低信號在傳輸過程中的損耗、保證信號完整性是高頻高速PCB發展中的巨大挑戰。高頻時代PCB產品的信號完整性由PCB原材料和PCB設計產品兩部分來提升。PCB材料的電性能可以通過測試介質層的介電常數、介質損耗以及導體銅箔粗糙度值來衡量;PCB產品的電性能主要通過測試阻抗和插入損耗(傳輸損耗)來衡量。主要介紹PCB原材料介質層的介電常數、介質損耗和導體銅箔粗糙度測試以及PCB產品阻抗、插入損耗設計和測試應用。

5G、物聯網以及無人駕駛技術都處于高速發展階段,需要在高頻高速條件下傳輸信號。PCB(Printed Circuit Board,印制電路板)系統需要成為具有高性能的系統結構,而不再僅是起支撐作用的電子元器件。目前,電子系統設計普遍信號頻率高于100 MHz,用來進行信號傳輸的高頻高速印刷電路板也越來越容易受到信號完整性問題的影響。信號傳輸過程更容易出現反射、串擾等信號完整性問題,且頻率越高、傳輸速率越快,信號損耗越嚴重,如何降低信號在傳輸過程中的損耗、保證信號完整性是高頻高速PCB發展中的巨大挑戰。

高頻時代PCB產品的信號完整性電性能從PCB原材料和PCB設計產品兩部分來提升。PCB材料的電性能可以通過測試介質層的介電常數( D k )、介質損耗( D f )以及導體銅箔粗糙度值來衡量;PCB產品的電性能主要通過測試阻抗和插入損耗(傳輸損耗)來衡量。

本文主要介紹PCB原材料介質層的介電常數、介質損耗和導體銅箔粗糙度測試以及PCB產品阻抗、插入損耗設計和測試應用。

1 PCB原材料介質層的參數介紹與測試

1.1 PCB原材料介質層的 D k 、 D f 及其測試

1.1.1 介電常數( D k )、介質損耗( D f )

介電常數:材料如果在受到外部電場作用時能夠儲存電能,就稱為“電介質”。比如說,電容可以存儲電荷,而當電容平板中間填充有介質時,存儲的電荷會更多。介電常數越大,儲存的電荷就越多,阻礙信號傳輸能力越大。

介質損耗:絕緣材料或電介質在交變電場中,由于介質電導和介質極化的滯后效應,使電介質內流過的電流相量和電壓相量之間產生一定的相位差,即形成一定的相角,此相角的正切值即損耗因子 D f ,由介質電導和介質極化的滯后效應引起的能量損耗叫做介質損耗,也就是說, D f 越高,介質電導和介質極化滯后效應越明顯,電能損耗或信號損失越多,是電介質損耗電能能力的表征物理量,也是絕緣材料損失信號能力的表征物理量。因此,PCB材料介質層的 D k , D f 越低,制作出的PCB產品插入損耗越低。

1.1.2 SPDR(Split Post Dielectric Resonator)法測試 D k 、 D f

測試高頻材料電性能特性的方法很多,有傳輸線法、自由空間法、同軸探針法和諧振腔法,其中諧振腔法是最適合用于低損耗材料的測試。SPDR就是其中一種分離介質諧振腔法,是單頻點的低損耗測試方法。SPDR的結構使用了極低損失的介電材料,使其能夠建立具有更高 Q 因數且熱穩定性優于傳統全金屬腔體的諧振器。SPDR的主要優勢是:

1)較之傳輸反射法具有出色精度;

2)能夠測試低損耗材料(傳輸反射技術無法測試損耗較低的材料);

3)不需要特殊的樣本制備,可對基片和介質層進行方便、快速的無損測試。

SPDR法是無損測試方法,通過測定共振器內插入介質層前后的共振頻率和 Q 值的變化量,測試 D k 和D f 值,測試夾具與測試原理如圖1所示。不同頻率使用不同的共振器目前提供的SPDR夾具可從1.1 GHz覆蓋到15 GHz。

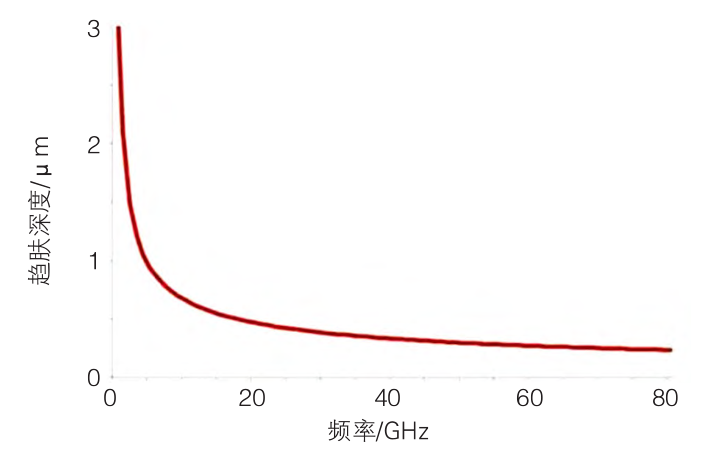

圖1 趨膚深度與頻率的關系1.2 導體銅箔粗糙度的測試

1.2.1 導體銅箔趨膚效應

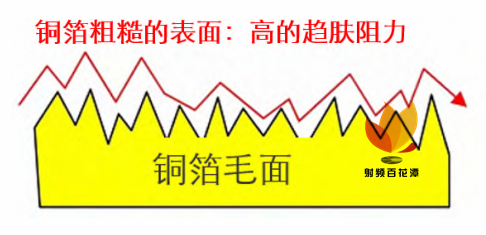

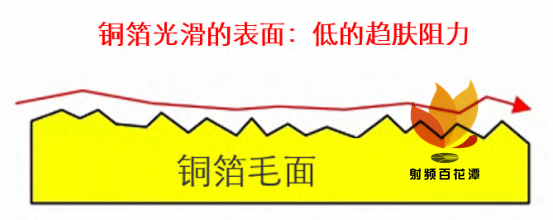

在高頻高速條件下,信號傳輸越來越集中于導體“表層”,即趨膚效應(Skin Effect)。當頻率達1 GHz時,其信號在導體表面的趨膚深度僅為2.10 μm;當信號傳輸頻率提高到10 GHz時,其信號在導體表面的趨膚深度為0.66 μm;而在毫米波頻段(>30 GHz),趨膚深度進一步降低至0.40 μm以下(如圖1所示)。如果導體表面粗糙度大于趨膚深度時,信號傳輸僅在粗糙度的厚度范圍內進行,使傳輸信號的駐波、反射越來越嚴重,并導致信號傳輸路徑變長,增加傳輸損耗(如圖2所示),信號在導體表面粗糙度低于趨膚深度時,傳輸路徑短,降低傳輸損耗(如圖3所示)。因此,導體銅箔粗糙度越低,制作出的PCB產品插入損耗(傳輸損耗)越低。

圖2 信號在粗糙度大的銅箔表面傳輸

圖3 信號在粗糙度低的銅箔表面傳輸

1.2.2 粗糙度測試

常規粗糙度的測試參數有:

1)線粗糙度:R a , R z, R q ;

2)面粗糙度:S a , S z , S q , S dr 。

R a , R z, R q 和 S a , S z , S q 粗糙度的定義同常規粗糙度的定義,這里需要特別強調的是 S dr 粗糙度。

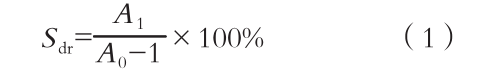

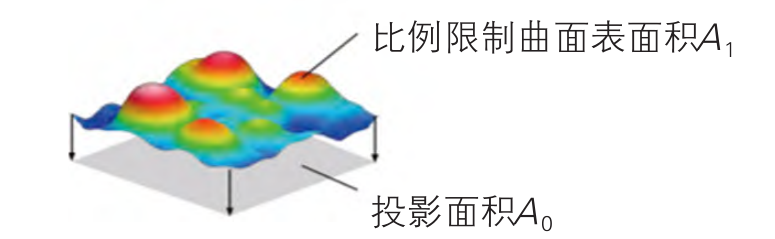

S dr 是界面擴展面積比,定義區域的擴展面積(表面積)表示相對于定義區域的面積增大了多少。如圖4所示,其計算公式為:

圖4 S dr 的定義圖

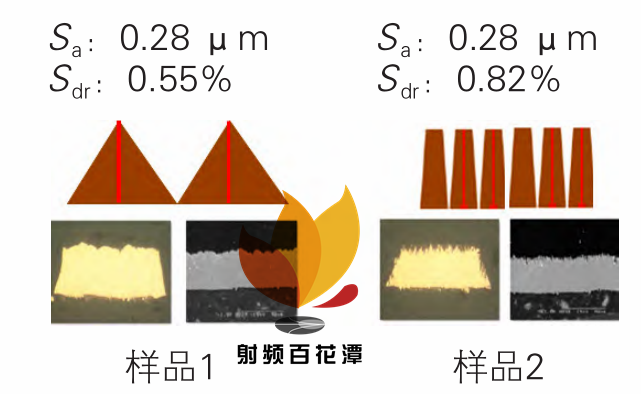

為什么要測 S dr ?如圖5所示,樣品1與樣品2測量的 S a 值相同,測量 S dr 后可以發現樣品2表面粗糙度較大。

圖5 相同 S a 值樣品的 S dr 不同

2 PCB產品阻抗設計和測試應用

2.1 PCB產品阻抗設計

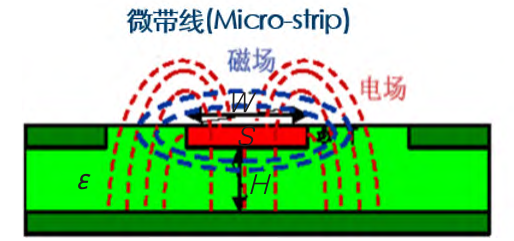

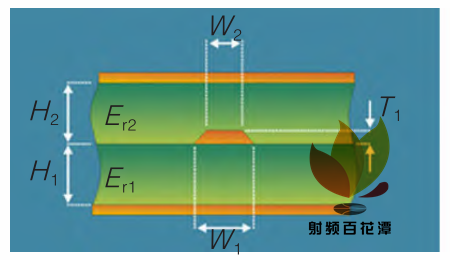

2.1.1 微帶線(Micro-strip)和帶狀線(Stripline)的設計如圖6所示,微帶線(Micro-strip)是一種分布于電路板外層的傳輸線,通過介電材料與單個接地平面分離。微帶線設計特點為:

1)電場穿透兩種不同的介質層,較難控制阻抗;

2)空氣的介電常數較PCB為低,所以整體微帶線的介電常數較低;

3)受控阻抗走線的寬度較寬;

4)因為在PCB的表面,所以較易受外界干擾。

圖6 微帶線

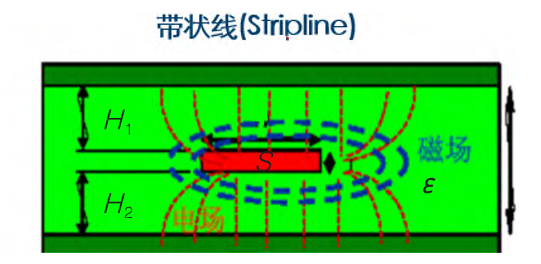

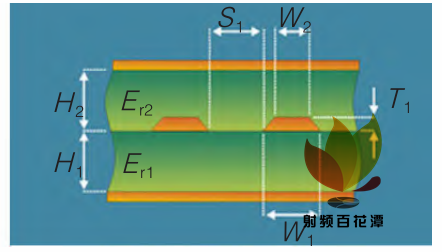

如圖7所示,帶狀線(Stripline)是由介電材料包圍的傳輸線,介于PCB內層兩個接地平面之間。帶狀線設計特點為:

1)電場只在PCB范圍內,較易控制阻抗;

2)介電常數較高;

3)受控阻抗走線的寬度要小于微帶線中相同阻抗下走線的的寬度,這是因為有第二個接地面的存在,這些更小的走線寬度可以實現更高的布線密度;

4)因為在PCB的里面,所以不易受干擾。

圖7 帶狀線

因此,做樣品設計時,推薦使用帶狀線設計,阻抗易于控制且抗外界干擾能力更強。

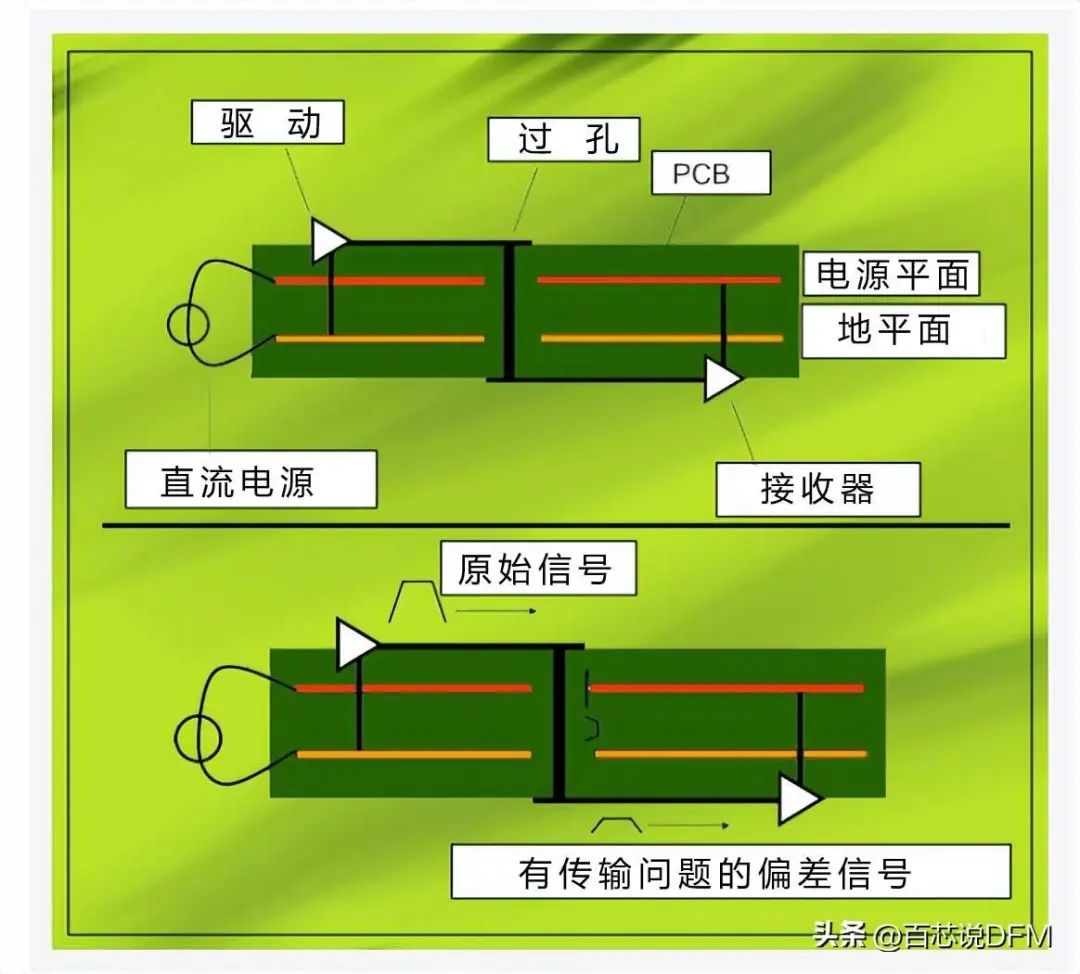

2.1.2 單分和差分設計

對于帶狀線,差分匹配好就不存在遠端噪聲。與單分信號相比,差分信號在信號完整性方面有很多優勢。比如有更好的抗噪聲能力,對衰減不敏感,在高頻電路設計中的應用越來越廣泛,電路中關鍵的信號往往都要采用差分結構設計,如圖8和圖9所示。

圖8 單分(單根走線)

圖9 差分(雙根走線)

2.2 PCB產品阻抗測試2.2.1 阻抗控制

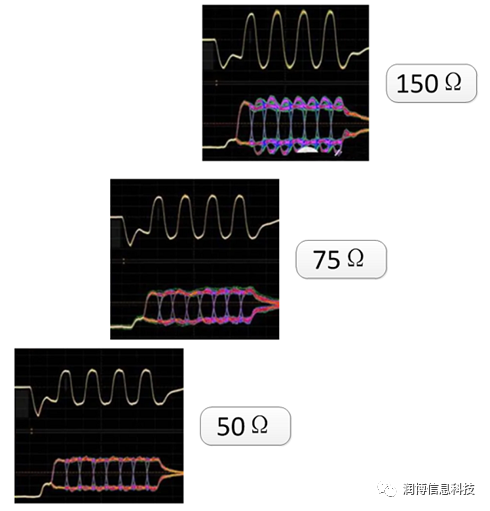

為了使電路板走向高密度、小體積及單一零件趨勢,多層板組裝高速零件時,訊號線的“特性阻抗”必須控制在一定范圍內,使高頻信號順利傳輸,以減少線路傳輸阻力、反射、失真、干擾等問題,此種品質要求稱為“阻抗控制”(一般單分阻抗控制在50 Ω,差分阻抗控制在100 Ω)。

2.2.2 阻抗測試

阻抗測試設備有3種類型:1)阻抗測試儀;2)示波器;3)網絡分析儀。

阻抗測試設備帶寬頻率越高,其組成的階躍信號上升寬度越窄,阻抗測試精度越高。

3 PCB產品插入損耗設計和測試應用

3.1 PCB產品插入損耗設計

3.1.1 高頻產品走線設計

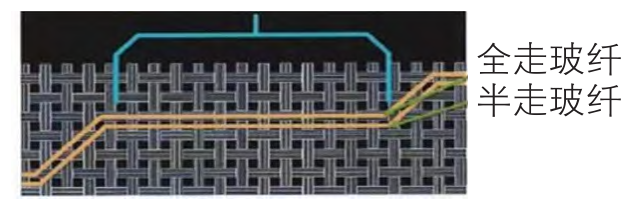

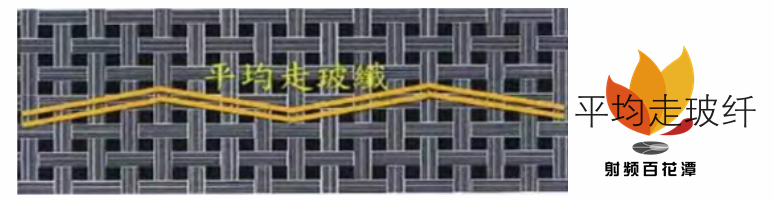

低頻時玻纖布對PCB的電氣性能影響較小,可以認為介質是均勻的,但高頻時,介質層局部特性將會對PCB的電氣特性有很大影響。因為玻纖布的相對介電常數和環氧樹脂存在較大差異(環氧樹脂約為3,玻纖布約為6),所以板面不同位置的介電常數存在差異,從而導致板面不同位置阻抗的差異。同時,同一阻抗線,由于位置不同,介電常數也不均勻,對于差分的影響更為明顯,如圖10和圖11所示。針對上述現象,可能的一些解決方式為:

1)走線避開玻纖束的編織間距;

2)差分走線間距正好避開玻纖束的編織間距;

3)之字形走線;

4)帶一定角度(一般15°角度傾斜)的走線;

5)設計人員旋轉設計;

6)PCB廠家旋轉基板;

7)使用高端基板材料;

8)使用更緊密的玻纖材料(玻纖束編織間距小)。

圖10 不正確的高頻走線

圖11 正確的高頻走線

3.1.2 去嵌入設計

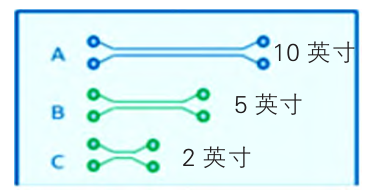

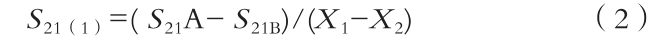

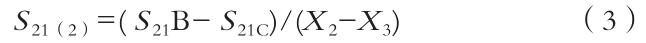

如圖12所示,為了消除測試誤差和過孔影響,設計三條不同長度的傳輸線,一般設計傳輸線線長分別為2英寸(1英寸=25.4 mm)、5英寸、10英寸。通過利用鄰近的長短二組線路分別測試插損。二組數據相減除以長度差異即可知純線路的插損值,可以比較兩組插損數據對比的差異值,來判定此次測試插損的精準性。即結構A、B、C的插損值都為各自傳輸線插損值與過孔插損值的和。

圖12 去嵌入設計

每英寸傳輸線插損值為:

每結構分成傳輸線插損值為:

若兩組傳輸線插損值

10%,則說明此次測試插損值精準性正常。

3.1 PCB產品插入損耗測試3.1.1 插入損耗

指輸出端口的輸出功率與輸入端口的輸入功率之比。

定義為:

式中:P i 為輸入到輸入端口的功率;P o 為從輸出端口接收到的功率。

3.2.2 信號完整性

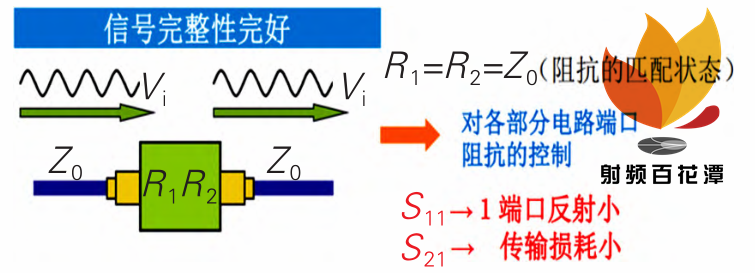

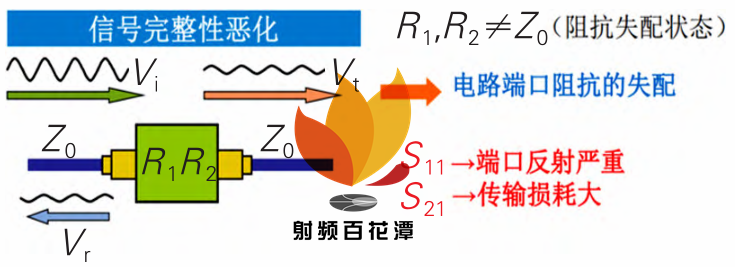

為了滿足信號完整性,測試電性能插損之前,先要測試產品阻抗匹配到50 Ω或100 Ω,這個和測試電性能Loss(損耗)儀器設計有關,測試電性能Loss儀器一般都是采購單端50 Ω,差分100 Ω的設計。產品的阻抗與儀器端口阻抗匹配時,測試端口幾乎沒有反射,測試插入損耗準確(如圖13所示);如果產品的阻抗與儀器端口阻抗不匹配及失配的狀態下,就會導致測試插入損耗時測試端口反射嚴重,導致測試插入損耗誤差大,測試結果不準確(如圖14所示)。

圖13 信號完整性完好

圖14 信號完整性惡化

3.2.3 插入損耗測試

常用的插入損耗測試方法有探針臺法、PLTS-AFR法和Delta-L法。表1是這3種測試方法的介紹。

表1 三種插入損耗測試方法

4 結論

本文簡述了高頻時代PCB產品的信號完整性電性能的測試。主要內容包括:1)PCB原材料介質層的D k 、 D f 以及導體銅箔粗糙度測試方法,可以直接評估高頻原材料的電性能,可以指導工廠選擇最優電性能的PCB原材料;2)PCB產品的阻抗與插入損耗設計與測試方法,介紹了如何通過阻抗設計匹配提高插入損耗測試精度,以及根據市場需求、測試頻率、操作方便性、測試精度選擇什么類型的插入損耗測試夾具作為測試參考。

作者:房蘭霞 來源:電子工藝技術

審核編輯:湯梓紅

-

pcb

+關注

關注

4318文章

23022瀏覽量

396424 -

電子元器件

+關注

關注

133文章

3311瀏覽量

104990 -

信號完整性

+關注

關注

68文章

1398瀏覽量

95392 -

傳輸信號

+關注

關注

0文章

46瀏覽量

9594 -

5G

+關注

關注

1353文章

48380瀏覽量

563448

原文標題:PCB信號完整性設計和測試應用

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB信號完整性設計和測試應用

PCB信號完整性設計和測試應用

評論