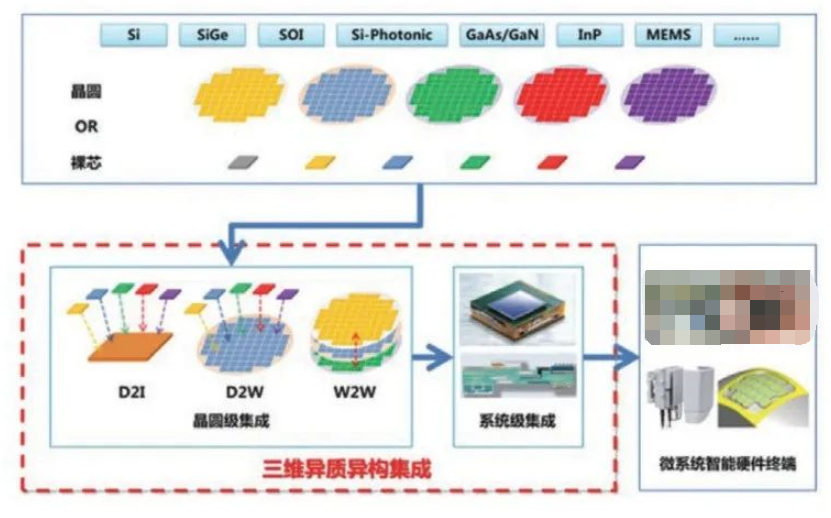

當(dāng)前,傳統(tǒng)集成電路CMOS 工藝按照“摩爾定律”經(jīng)過數(shù)十年的發(fā)展,已經(jīng)開始邊際收益遞減,表現(xiàn)為引入下一代技術(shù)后單個(gè)晶體管成本不降反升,性能提升、面積縮小、功耗降低(PPA)放緩。而通過三維異質(zhì)集成(3D Heterogeneous Integration,3DHI)等先進(jìn)封裝技術(shù)實(shí)現(xiàn)系統(tǒng)層面的小型化、多功能化,已成為集成電路技術(shù)創(chuàng)新的重要方向之一。

中國(guó)工程院院士、浙江大學(xué)微納電子學(xué)院院長(zhǎng)吳漢明曾提出了三條可以突破高算力發(fā)展瓶頸的創(chuàng)新途徑,其中就包括三維異質(zhì)集成晶圓級(jí)集成技術(shù)(另外兩個(gè)創(chuàng)新路徑為存算一體范式、可重構(gòu)計(jì)算架構(gòu))。上海科學(xué)技術(shù)情報(bào)研究所也將三維異質(zhì)集成列為當(dāng)前全球前沿科技發(fā)展的熱點(diǎn)。

總體來看,3DHI 技術(shù)具有以下優(yōu)點(diǎn):

一是將芯片封裝架構(gòu)由平面拓展至2.5D 或3D,可實(shí)現(xiàn)更小更緊湊的芯片系統(tǒng);二是可以融合不同的半導(dǎo)體材料、工藝、器件的優(yōu)點(diǎn),實(shí)現(xiàn)更復(fù)雜的功能和更優(yōu)異的性能;

三是將單芯片系統(tǒng)(SOC)分拆成若干小芯片,簡(jiǎn)化了芯片設(shè)計(jì)復(fù)雜度,單個(gè)小芯片功能可以單獨(dú)優(yōu)化,提高了芯片設(shè)計(jì)效率;

四是使用3DHI技術(shù)還可以避免芯片(Die)尺寸增大而帶來良率的下降,各個(gè)Die可以使用不同的最佳工藝,實(shí)現(xiàn)制造成本的降低。

不過,要實(shí)現(xiàn)3DHI,集成工藝方面仍需要突破幾個(gè)關(guān)鍵技術(shù),如:硅通孔(TSV)、晶圓/芯片鍵合技術(shù)、散熱等。

21 世紀(jì)以來,美國(guó)國(guó)國(guó)防部高級(jí)研究局(DARPA)、比利時(shí)微電子研究中心(IMEC)等機(jī)構(gòu)支持開展了大量3DHI 的研究項(xiàng)目。DARPA 先后設(shè)立硅上化合物半導(dǎo)體材料(COSMOS)、多樣化易用異構(gòu)集成(DAHI)、通用異構(gòu)集成及IP復(fù)用策略(CHIPS)、下一代微電子制造(NGMM)等項(xiàng)目,持續(xù)、系統(tǒng)地支持3DHI 技術(shù)研發(fā)。

產(chǎn)業(yè)鏈各環(huán)節(jié)企業(yè)如日月光、臺(tái)積電、英特爾、三星、美光、AMD等均積極布局3DHI 技術(shù),隨著先進(jìn)封裝工藝與前道制程結(jié)合更加緊密,臺(tái)積電、英特爾和三星等上游芯片制造企業(yè)成為3DHI 技術(shù)創(chuàng)新的最重要參與者。

英特爾嘗試通過晶體管、封裝和芯片設(shè)計(jì)協(xié)同優(yōu)化繼續(xù)摩爾定律演進(jìn)。公司提供嵌入式多芯片互連橋接(EMIB)、Foveros 3D封裝等異質(zhì)集成技術(shù)。EMIB通過一個(gè)橋接硅片,將不同芯片組合在一起,可實(shí)現(xiàn)50μm-40μm的凸點(diǎn)間距。Foveros 是英特爾開發(fā)的晶圓級(jí)3D 封裝技術(shù),可以實(shí)現(xiàn)在邏輯芯片堆疊,其凸點(diǎn)間距可達(dá)50-36μm。此外,英特爾還在研發(fā)下一代Foveros Omni和FoverosDirect 技術(shù)。前者支持分拆芯片(die disaggregation)設(shè)計(jì),為芯片到芯片的互連和模塊化設(shè)計(jì)提供更高的靈活性;后者實(shí)現(xiàn)了由傳統(tǒng)凸點(diǎn)焊接到銅對(duì)銅直接鍵合(Hybird bonding)的轉(zhuǎn)變,可以實(shí)現(xiàn)10微米以下的凸點(diǎn)間距,芯片互連密度提高一個(gè)數(shù)量級(jí)。兩項(xiàng)技術(shù)計(jì)劃在2023年實(shí)現(xiàn)量產(chǎn)。

臺(tái)積電推出3D Fabric 先進(jìn)封裝平臺(tái),提供扇入型晶圓級(jí)封裝(Fan-in WLP)、整合扇出型封裝(InFO),2.5D片上晶圓基板(CoWoS)封裝,以及3D集成片上系統(tǒng)(SoIC)等封裝技術(shù)。臺(tái)積電CoWoS 在芯片與基板中間加入硅中介層,實(shí)現(xiàn)重新布線及高密度互聯(lián);SoIC采用無凸點(diǎn)(no Bump)直接鍵合技術(shù),實(shí)現(xiàn)CoW(Chip on Wafer)、WoW(Wafer on Wafer)直接互連。2020年,臺(tái)積電投資100 億美元在中國(guó)臺(tái)灣地區(qū)竹南科學(xué)園建設(shè)全球首座全自動(dòng)化3D Fabric先進(jìn)封裝廠AP6,預(yù)計(jì)2022年下半年開始生產(chǎn)。2021年2月,臺(tái)積電投資186億日元,在日本茨城縣設(shè)立半導(dǎo)體材料研發(fā)中心,與日本企業(yè)合作開展3D IC封裝與散熱相關(guān)材料研發(fā)。三星的先進(jìn)封裝平臺(tái)包括I-Cube、X-Cube、R-Cube 和H-Cube。I-Cube 是采用硅中介層的2.5D 封裝方案,能夠?qū)⒁粋€(gè)或多個(gè)邏輯芯片(CPU、GPU 等)和多個(gè)高帶寬內(nèi)存(HBM)芯片水平集成在硅中介層上。R-Cube 則是三星的低成本2.5D 封裝方案。H-Cube 是三星電子在2021 年11 月新推出的2.5D 封裝解決方案,專用于需要高性能和大面積封裝技術(shù)的高性能計(jì)算(HPC)、人工智能等領(lǐng)域。X-Cube 是三星的3D IC 封裝方案(表1)。

表1:主要芯片企業(yè)三維異質(zhì)封裝技術(shù)發(fā)展概況

在“863計(jì)劃”“973計(jì)劃”等支持下,中國(guó)機(jī)構(gòu)在3DHI方面也取得一系列成果。中國(guó)科學(xué)院物理研究所解決了硅上異質(zhì)外延生長(zhǎng)Ⅲ-Ⅴ族材料的難題;中科院上海微系統(tǒng)所研制了多種硅基異質(zhì)材料集成襯底,如:絕緣體上碳化硅、絕緣體上鈮酸鋰、絕緣體上Ⅲ-Ⅴ族等。中芯國(guó)際、長(zhǎng)電、通富微電、長(zhǎng)江存儲(chǔ)、華為海思等企業(yè)也在3DHI技術(shù)開發(fā)、應(yīng)用方面取得長(zhǎng)足進(jìn)步。長(zhǎng)江存儲(chǔ)開發(fā)的Xtacking 堆棧技術(shù),將CMOS外圍電路堆疊在NAND芯片下方,構(gòu)建了高密度、高速存儲(chǔ)結(jié)構(gòu)。而在上游支撐設(shè)備及工具軟件方面,也有一批企業(yè)實(shí)現(xiàn)技術(shù)突破。華海清科針對(duì)3D IC研制的12英寸晶圓減薄拋光一體機(jī)已進(jìn)入生產(chǎn)驗(yàn)證;中微半導(dǎo)體的深硅刻蝕機(jī)已經(jīng)應(yīng)用在歐洲客戶MEMs生產(chǎn)線;上海微電子裝備成功研制出2.5D3D先進(jìn)封裝***,具有高分辨率、高套刻精度和超大曝光視場(chǎng)等特點(diǎn),可滿足超大尺寸芯片異構(gòu)集成的應(yīng)用需求。芯和半導(dǎo)體是英特爾UCIe聯(lián)盟中為數(shù)不多的EDA工具企業(yè),公司與新思科技合作開發(fā)3D IC封裝設(shè)計(jì)分析平臺(tái)。

審核編輯 :李倩

-

晶圓

+關(guān)注

關(guān)注

52文章

4846瀏覽量

127805 -

封裝技術(shù)

+關(guān)注

關(guān)注

12文章

545瀏覽量

67961 -

芯片封裝

+關(guān)注

關(guān)注

11文章

479瀏覽量

30567

原文標(biāo)題:三維異構(gòu)集成技術(shù)發(fā)展的競(jìng)爭(zhēng)態(tài)勢(shì)分析

文章出處:【微信號(hào):jbchip,微信公眾號(hào):電子元器件超市】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

世界級(jí)專家為你解讀:晶圓級(jí)三維系統(tǒng)集成技術(shù)

三維觸控技術(shù)突破“二向箔”的束縛

三維快速建模技術(shù)與三維掃描建模的應(yīng)用

廣西掃描服務(wù)三維檢測(cè)三維掃描儀

三維設(shè)計(jì)應(yīng)用案例

三維可視化的應(yīng)用和優(yōu)勢(shì)

上海黃浦三維媒體動(dòng)畫技術(shù)

基于LTCC技術(shù)的三維集成微波組件

三維人臉建模技術(shù)分析及應(yīng)用

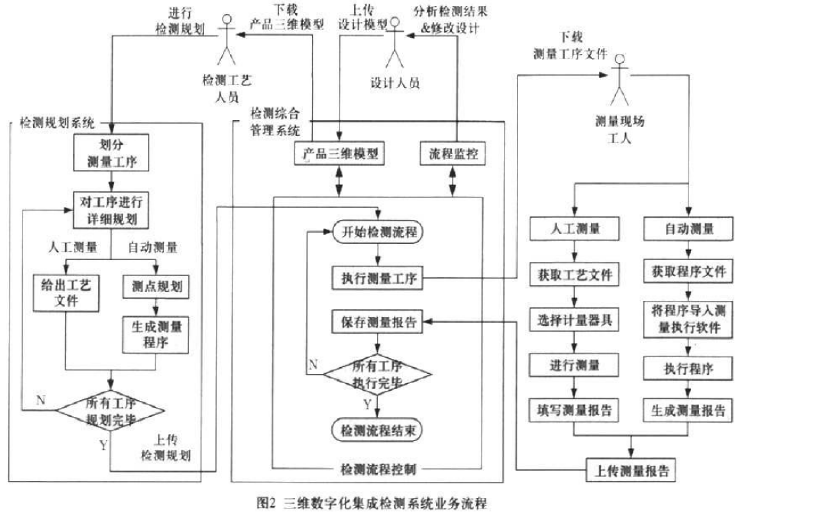

三維數(shù)字化集成檢測(cè)系統(tǒng)實(shí)現(xiàn)關(guān)鍵技術(shù)分析

蔡堅(jiān):封裝技術(shù)正在經(jīng)歷系統(tǒng)級(jí)封裝與三維集成的發(fā)展階段

基于三維集成技術(shù)的紅外探測(cè)器

淺談三維單片異構(gòu)集成的發(fā)展歷程

三維異構(gòu)集成技術(shù)發(fā)展的競(jìng)爭(zhēng)態(tài)勢(shì)分析

三維異構(gòu)集成技術(shù)發(fā)展的競(jìng)爭(zhēng)態(tài)勢(shì)分析

評(píng)論