在本文中,我們將討論具有高共模抑制并提供高和相等輸入阻抗的儀表放大器(儀表放大器)。我們還將探討常用儀表放大器(通常稱為三運儀表放大器)的優缺點。

在本系列的前幾篇文章中,我們討論了儀表放大器(儀表放大器)應具有 高共模抑制 以及 高阻抗和相等輸入阻抗 以成功提取小差分信號。

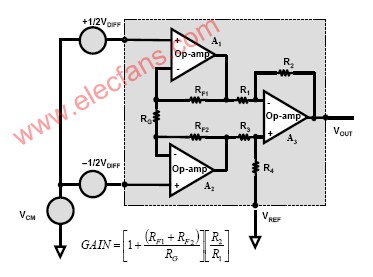

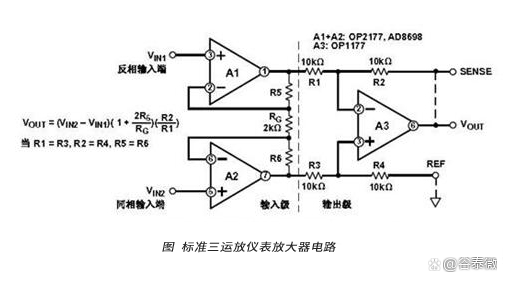

在本文中,我們將介紹一種常用的儀表放大器,通常稱為三運放大器儀表放大器。我們將看到,三運放儀表放大器采用具有幾個有趣功能的巧妙架構。

經典的三運放儀表放大器

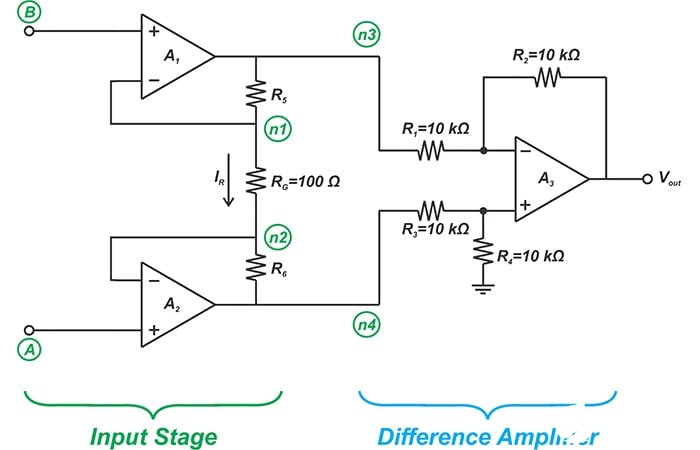

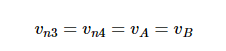

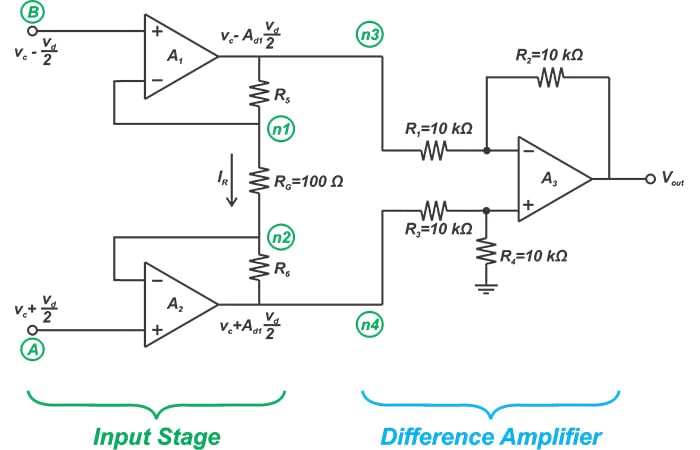

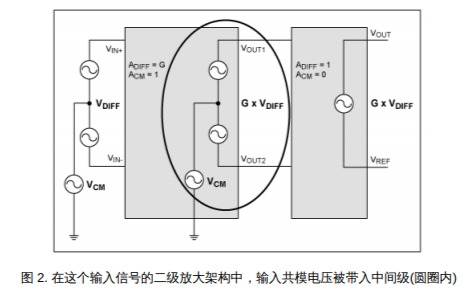

圖1所示的三運放結構是一種常用的儀表放大器電路,可提供高CMRR和平衡、高輸入阻抗。

圖1

上面的示意圖可以分解為兩部分。輸入級主要用作緩沖器。輸出級為 上一篇文章中討論的差動放大器.正如我們將在下面看到的,三運放儀表放大器采用了具有幾個有趣功能的巧妙架構。

高平衡輸入阻抗

節點A和B都連接到相應運算放大器的同相輸入端。這提供了高、平衡的輸入阻抗,而無需訴諸復雜的反饋技術。

輸入級可提供高差分增益和共模抑制比

讓我們首先計算輸入級的微分增益。負反饋連同運算放大器的高增益將迫使 A 1和 A 2的反相和非反相輸入具有相同的電壓。因此,我們有:

通過 R G并因此通過 R 5和 R 6 的電流將為:

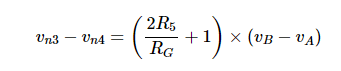

因此,當 R 5 =R 6時,差分放大器輸入端的電壓差將為:

這簡化為

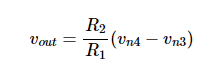

我們知道差動放大器的增益為:

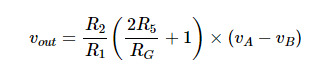

因此,我們有:

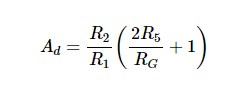

因此,電路的總差模增益為:

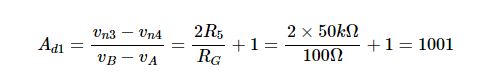

公式1顯示輸入級的差分增益AD1,可以通過選擇 R 的值進行調整5 和 RG.例如,圖 1 和 R 中的典型值5=50 kΩ, AD1 將是:

輸入級的共模增益是多少?基于以上分析,v一個=vB、R 兩端的電壓G 將為零。因此,沒有電流會流過R5/ 1G和 R6;我們有:

總而言之,輸入級可以給我們很大的差分增益,同時以單位增益傳遞共模信號。這導致輸入級的CMRR相對較高。接下來,差動放大器將進一步抑制該殘余共模信號。輸入級的一個有趣特性是,增加差分增益也會增加CMRR。

通過設置單個電阻的值來調節增益

從公式1可以看出,我們可以通過調整單個電阻R的值來調整儀表放大器的差分增益。G.這很重要,因為與電路中的其他電阻不同,R 的值G 不需要與任何其他電阻器匹配。

例如,如果我們嘗試通過更改 R 的值來設置增益5,我們還需要更改 R6 因此。實現匹配的可調電阻比調整單個電阻更具挑戰性。

源電阻未出現在增益公式中

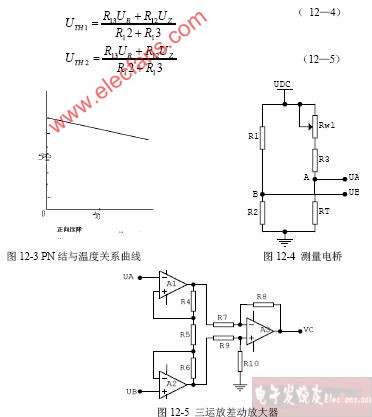

考慮下面圖2所示的橋梁測量系統。

圖2.

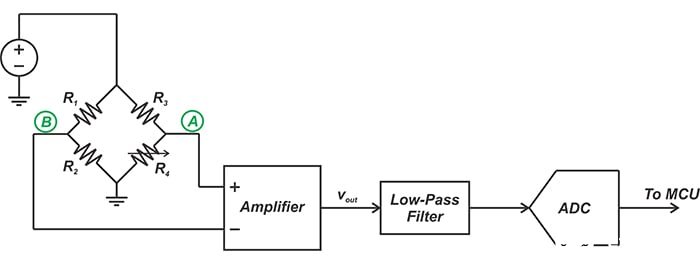

應用戴維寧定理,我們可以對橋梁進行建模,如圖 3 所示。

圖3.

在這里,RTh1 和 RTh2 是兩個橋分支的等效電阻;和 VTh1 和 VTh2 是節點 A 和 B 的戴維寧等效電壓。此外,上圖通過R模擬放大器輸入端“看到”的阻抗在1和 Rin2.

該模型表明,分壓器是由放大器的輸入阻抗和電橋的等效電阻產生的。該分壓器確定放大器輸入端出現的電壓。因此,對于輸入阻抗相對較小的增益級(如差動放大器),總增益將是R的函數。Th1 和 RTh2.這會導致增益可預測性差并降低精度。

但是,三運放儀表放大器在其輸入端提供非常高的阻抗。因此,電橋的戴維寧等效電壓出現在放大器輸入端,而不會被分壓器衰減。由于源電阻不會出現在增益方程中,因此我們獲得了更可預測的增益和更高的精度。

減小共模電壓范圍

三運放儀表放大器的一個限制是,如果我們試圖在輸入級實現非常高的差分增益,則輸入共模范圍可能會受到限制。

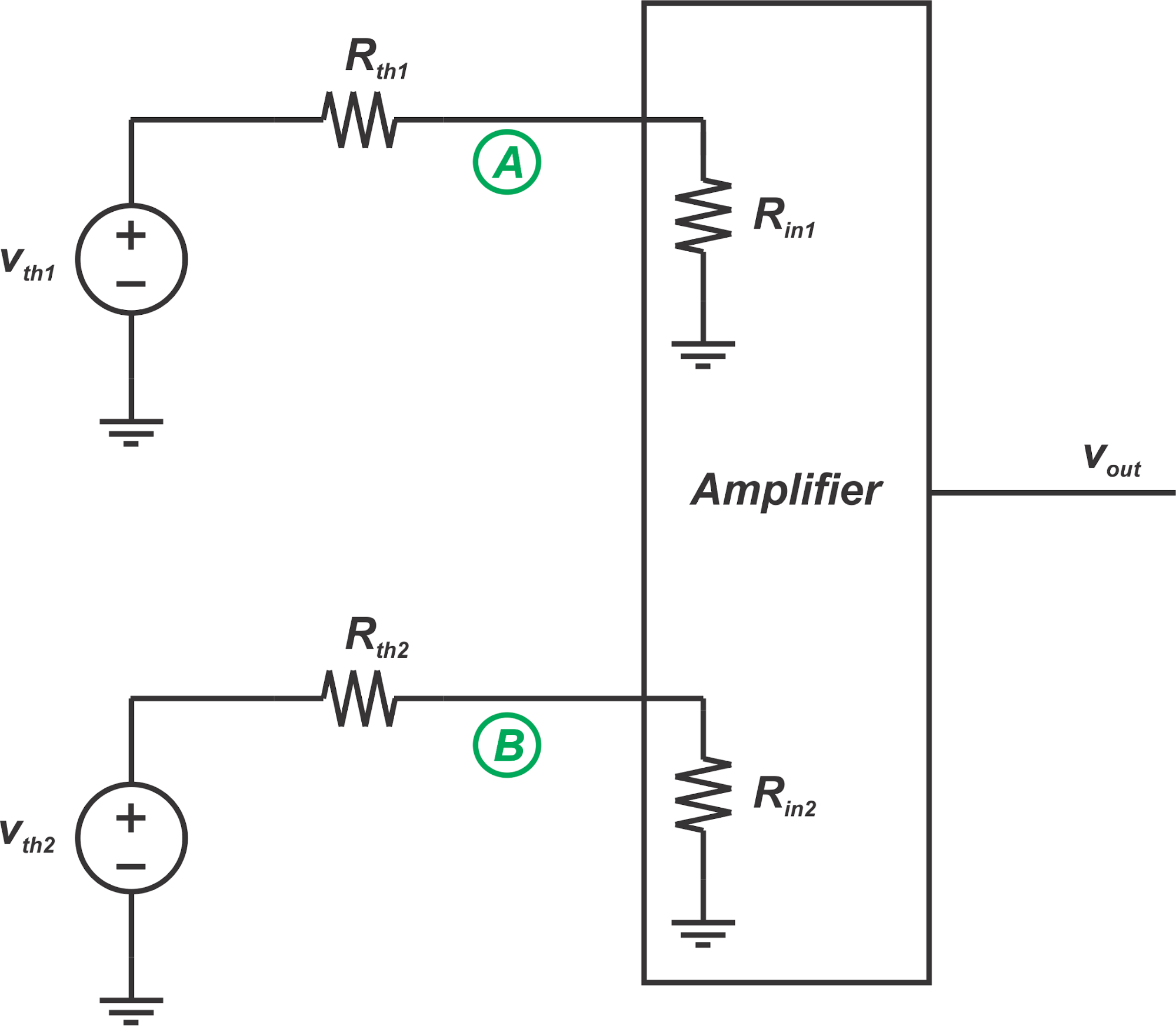

如圖4所示,當差模信號為vd 在 V 共模電壓下運行c 施加到輸入,節點 n 處的電壓3 和 n4 將分別為 (v_c-A_{d1}frac{vd}{2}) 和 (v_c+A_{d1}frac{vd}{2})。在這里,一個D1 是上述公式2給出的輸入級的差分增益。在c?一個d1在d2vc?Ad1vd2 和 在c+一個d1在d2vc+Ad1vd2分別。在這里,一個

圖4

與 vd=10 mV 和 AD1=1000,節點n處的電壓4 將為 vc+5V.該電壓應在輸出放大器的共模范圍內,A3,所以它不會飽和。如您所見,根據輸入級的差模增益,我們需要設置輸入共模電壓v的上限c.

結論

三運放儀表放大器是一種常用的結構,可以放大差分信號,同時剝離任何共模電壓。該電路的一個優點是,不需要與電路中任何其他電阻匹配的單個電阻決定了增益。這使我們能夠更輕松地調整電路增益。此外,對于三運放大器儀表放大器,源阻抗在增益計算中不起作用。

這些優勢是以額外的信號延遲和減小共模電壓范圍為代價實現的。

-

儀表放大器

+關注

關注

17文章

406瀏覽量

71145 -

三運放

+關注

關注

0文章

2瀏覽量

6165

發布評論請先 登錄

相關推薦

三運放儀表放大器的放大倍數分析

了解三運放儀表放大器

了解三運放儀表放大器

評論