似乎幾乎每周,半導體行業(yè)包羅萬象的晴雨表摩爾定律都會被宣布死亡、垂死或?qū)嶋H上比以往任何時候都更健康。隨著爭論繼續(xù)猜測其健康狀況,可以肯定的是,隨著FinFET技術(shù)取代了傳統(tǒng)2D平面柵極市場的更大份額,單一的單片芯片設(shè)計將變得不可持續(xù)。

清算之日

越來越多的公司正在通過制造標準化的“小芯片”并從中組裝一系列更復雜的設(shè)計來恢復“系統(tǒng)級封裝(SiP)”或“異構(gòu)集成(HI)”方法。這種將類似樂高的硅片組合成單個封裝設(shè)備的模塊化方法并不是什么新鮮事,自 1980 年代以來一直存在于 MCM 中。就連戈登·摩爾(Gordon Moore)的原始文章也承認,他的理論終將迎來清算的一天,并且需要一種更橫向的方法。

為什么現(xiàn)在使用小芯片?

Chiplet 提供了一種靈活、可擴展且經(jīng)濟高效的方法,可以滿足現(xiàn)代系統(tǒng)不斷變化的復雜性需求。

與SoC更均勻的單芯片集成相比,這種異構(gòu)方法可以大大降低制造和設(shè)計成本,因為并非所有小芯片都必須在最新的節(jié)點上制造。例如,核心邏輯小芯片可以利用頂級晶圓廠的最新和最好的產(chǎn)品,而I/O小芯片可以在更小、更實惠的代工廠生產(chǎn)。因此,SiP 可以提供比單芯片 SoC 更大的優(yōu)勢,例如更高的晶圓良率和更快的上市時間,盡管將它們集成到具有專用小芯片基板(中介層)的單個封裝中很復雜。

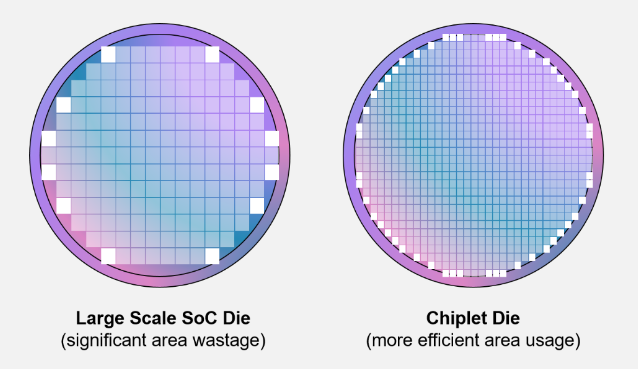

隨著每個前進工藝節(jié)點的特征尺寸減小,缺陷密度也相應增加,這給制造商帶來了重大問題。結(jié)合復雜SoC設(shè)計的絕對尺寸較大,對于大型單片設(shè)計,每個晶圓的可用優(yōu)質(zhì)芯片明顯減少。如果隨著我們越來越向亞納米技術(shù)邁進,缺陷密度繼續(xù)增長,除了減小模具本身的尺寸之外,還有什么選擇?

然而,可以通過生產(chǎn)更小的設(shè)計(小芯片)組裝成更大的設(shè)計(SiP)來提高良率。另一個好處是更好的晶圓利用率,這是通過每個晶圓封裝比大型SoC芯片更多的小芯片來實現(xiàn)的,這浪費了大量空間。

今天的小芯片實施

系統(tǒng)的靈活性意味著只有與功能更新相對應的小芯片需要重新設(shè)計,從而最大限度地減少設(shè)計過渡到新節(jié)點的總體工作量。成本節(jié)約也可以沿著供應鏈傳遞,無需針對不同市場單獨設(shè)計的產(chǎn)品系列。這通過替換適當?shù)男⌒酒瑏碓趦r格和性能上與目標細分市場相匹配,從而簡化了庫存單位 (SKU) 成本。

鑒于基于小芯片的設(shè)計的優(yōu)勢,許多行業(yè)重量級人物已經(jīng)開始他們的小芯片計劃也就不足為奇了:英特爾的 Agilex FPGA 和 SoC、AMD 及其 EPYC 和銳龍處理器系列、NVIDIA 使用他們的小芯片互連技術(shù) NVLink-C2C,甚至臺積電在 2020 年推出了他們的 3DFabric 技術(shù)來幫助客戶設(shè)計自己的基于小芯片的 SiP。為了不錯過這一行動,美國政府還投入了資源,通過DARPA的通用異構(gòu)集成和知識產(chǎn)權(quán)重用策略(CHIPS)探索這種有前途的芯片設(shè)計風格。最后,證明基于小芯片的設(shè)計不僅僅是一種曇花一現(xiàn)的時尚,已經(jīng)有人推動了小芯片相互通信的方式正式化,通用小芯片互連快遞(UCIe)開放標準正在被英特爾、AMD、Arm、臺積電、三星、高通、谷歌和微軟等公司推廣。

安全隱患

由于流行趨勢傾向于基于小芯片的方法而不是單片單芯片SoC,我們可能會將超過十個小芯片集成到單個設(shè)計中,每個小芯片可能來自不同的晶圓。從安全角度來看,當從單個SoC芯片移動到多個SiP芯片時,攻擊面的數(shù)量將迅速增加。采購的每個小芯片都涉及許多可能的鑄造來源和設(shè)計公司。不僅需要保護多組 I/O,而且每個供應商不一定遵守同一組安全協(xié)議。

目前,這可能不是一個問題,因為小芯片只占據(jù)很小的市場份額。然而,隨著小芯片開始得到更廣泛的采用,小芯片供應商的數(shù)量將會擴大,管理不同的安全約定將很快成為一個重大風險。

小芯片供應鏈風險

連接國際供應商的地緣政治緊張局勢只會增加復雜性,尤其是在美國和中國之間的緊張局勢繼續(xù)加劇的情況下,雙方都試圖將本已脆弱的半導體供應鏈分叉。因此,通過供應鏈從一個位置到另一個位置安全地跟蹤組件對于確保SiP至關(guān)重要。因此,供應鏈中的任何潛在薄弱環(huán)節(jié)都是攻擊者插入受感染小芯片的成熟目標,可能帶有惡意負載、特洛伊木馬或間諜軟件。

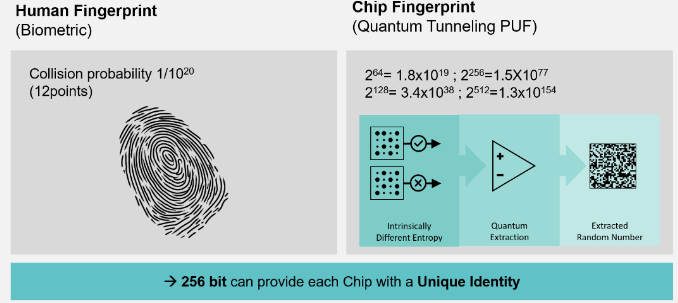

PUF 芯片指紋識別

鑒于在向基于小芯片的架構(gòu)過渡期間面臨的這些新的安全挑戰(zhàn),令人欣慰的是,目前與 SoC 一起部署的相同 PUF 保護也可以為 SiP 創(chuàng)建基礎(chǔ)信任根。當集成到設(shè)計中時,它們可以為每個小芯片提供源自PUF芯片指紋的唯一標識(UID)。

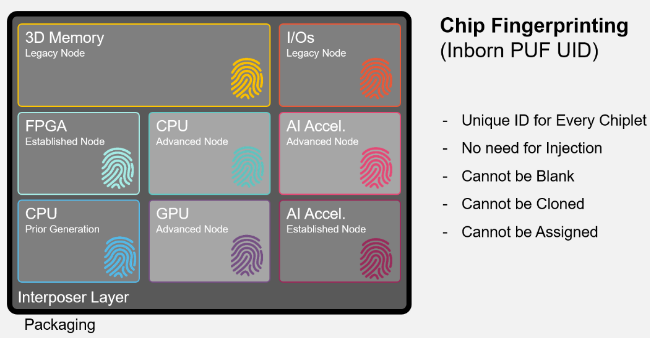

嵌入到SiP中每個小芯片中的物理不可克隆功能(PUF)將匯集基于小芯片設(shè)計的碎片化特性,并支持四個中央安全功能。

身份驗證:通過識別每個小芯片,PUF將確保每個小芯片都真正來自合法供應商。

配置:在驗證每個小芯片是真實的后,中央安全服務器可能會將其打開,以防止假冒或被篡改的小芯片通過未經(jīng)授權(quán)的渠道進入供應鏈。配置還可用于打開和關(guān)閉系統(tǒng)中的功能,針對特定市場或目標客戶定制每個設(shè)計,同時為這些不同情況使用相同的基本SiP。

跟蹤:當每個小芯片都有一個唯一的標識符時,在整個設(shè)計和組裝過程中跟蹤它們變得更加容易。對于安全漏洞可能造成災難性后果的客戶(例如汽車或航空市場)而言,通過SiP供應鏈留下清晰的審計跟蹤尤為重要。

分析:當我們能夠識別每個小芯片時,我們可以收到有關(guān)每個小芯片狀態(tài)的反饋。這些數(shù)據(jù)可以安全地發(fā)回,用于實時分析、故障分析,甚至是無法承受停機時間的關(guān)鍵任務應用程序的連續(xù)狀態(tài)監(jiān)控。

當然,每個小芯片都可以通過外部密鑰注入過程單獨配置自己的ID,但考慮到將進入復雜設(shè)計的小芯片數(shù)量,通過嵌入能夠進行內(nèi)部密鑰配置的PUF來自動執(zhí)行此操作更有意義,而無需安全,干凈的房間環(huán)境和生成唯一ID所需的相關(guān)安全硬件。

通過在HI設(shè)計中的每個小芯片上添加PUF,可以輕松實現(xiàn)對上述四個功能的支持。或者,如果其中一個小芯片專門用于安全,則可以使用基于PUF的小芯片硬件安全模塊(CHSM)。在這種情況下,SiP將不再需要依賴外部安全服務器來提供服務,例如上述身份驗證過程。

由于 CHSM 執(zhí)行與信任根在 SoC 中執(zhí)行的職責類似,因此 SiP 安全的總體基礎(chǔ)可能來自 CHSM 本身。有了這樣的基礎(chǔ),也可以在SiP中實現(xiàn)類似“安全啟動”的過程。從理論上講,這將從CHSM的身份驗證開始,然后授權(quán)鏈中的下一個小芯片啟用,然后啟動鏈中下一個小芯片的授權(quán)過程,依此類推,直到整個SiP被啟動。根據(jù) CHSM 的配置方式,它還可以充當安全控制器來監(jiān)視其他小芯片是否存在安全屬性違規(guī)、硬件特洛伊木馬和篡改。添加額外的傳感器可以進一步檢測物理篡改,例如通過激光、X 射線、電壓/時鐘毛刺等。捕獲此類故障注入 (FI) 類型的攻擊非常重要,因為它們通常會導致側(cè)信道分析/攻擊。

結(jié)論

無論圍繞摩爾定律終點的爭論如何,都明確需要橫向創(chuàng)新來應對較小工藝節(jié)點的物理極限。小芯片架構(gòu)可能會在這方面發(fā)揮至關(guān)重要的作用。然而,隨著對設(shè)計制造過程的如此徹底的重新構(gòu)想,當我們從SoC轉(zhuǎn)向SiP時,將有一連串不可預測的安全問題需要考慮。

最有可能的情況是在每個 3D 封裝中部署一個經(jīng)過預認證和認證的基于 PUF 的安全元件 (SE) 小芯片。這將允許硬件信任根支持正在使用、傳輸中和靜態(tài)數(shù)據(jù)的安全性。隨著新一代芯片設(shè)計的推向市場,隨著CPU遷移到最先進的工藝,可以繼續(xù)部署相同經(jīng)過驗證和合格的基于PUF的SE小芯片,從而簡化工藝。

想象同一個3D包中的每個小芯片部署基于PUF的保護的未來并不是一件容易的事。面對供應鏈安全風險以及安全組裝、驗證和更新 SiP 的需求,標準化 SiP 安全性似乎是不可避免的。

審核編輯:郭婷

-

傳感器

+關(guān)注

關(guān)注

2548文章

50694瀏覽量

752037 -

芯片

+關(guān)注

關(guān)注

454文章

50426瀏覽量

421860 -

SiP

+關(guān)注

關(guān)注

5文章

499瀏覽量

105264

發(fā)布評論請先 登錄

相關(guān)推薦

紅米NOTE電池保護板碼片方案

“5分鐘快充”時代有效的芯片保護電路

使用片上系統(tǒng)芯片怎么實現(xiàn)傳感器模塊的軟硬件設(shè)計?

基于片上系統(tǒng)芯片的傳感器模塊設(shè)計

ADSL收發(fā)器片上系統(tǒng)芯片的設(shè)計與實現(xiàn)

基于片上系統(tǒng)芯片的傳感器模塊軟硬件設(shè)計

基于軟硬件協(xié)同的數(shù)據(jù)動態(tài)保護機制

保護片上系統(tǒng):小芯片時代的硬件保護

保護片上系統(tǒng):小芯片時代的硬件保護

評論