本篇文章為大家介紹AXI的協議與架構。

內容概括

這次為大家講述的內容包括:

關于AXI協議

AXI架構

0****1

AXI協議

AMBA AXI協議支持用于主從模塊之間通信的高性能、高頻率系統設計。

AXI****協議的定位:

?適用于高帶寬、低時延設計

?不需要復雜的橋就可以滿足高頻時鐘的要求

?滿足大多數模塊的接口需求

?適用于初始延遲較高的存儲器控制

?在總線互聯架構上提供更大的靈活性

?后向兼容AHB和APB接口

**AXI **協議的主要特征:

?地址/控制操作與數據操作分離

?使用byte strobes(字節選通)信號實現非對齊數據傳輸

?使用burst傳輸(突發傳輸)時只需要發送首地址,便可以發送一段數據

?讀數據和寫數據通道獨立,從而支持DMA (low-cost Direct Memory Access)

?支持outstanding功能,可以發送多個地址進行讀寫

02

AXI架構

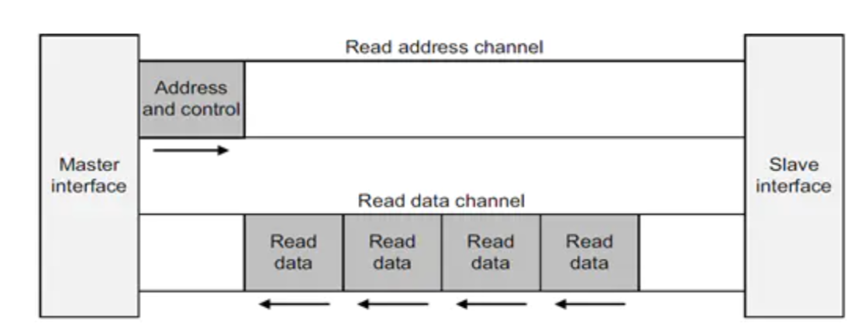

AXI協議是基于burst的傳輸,并且定義了以下5個獨立的傳輸通道:讀地址通道、讀數據通道、寫地址通道、寫數據通道、寫響應通道。

a

讀架構

地址通道攜帶控制消息,用于描述被傳輸的數據屬性;數據傳輸使用寫通道來實現master到slave的傳輸,slave使用寫響應通道來完成一次寫傳輸;讀通道用來實現數據從slave到master的傳輸。

相關信號:

讀地址通道信號:

| 信號名 | 來源 | 描述 |

|---|---|---|

| ARID | master | 讀地址ID |

| ARADDR | master | 讀地址 |

| ARLEN | master | 突發長度 |

| ARSIZE | master | 突發尺寸(每次突發傳輸的byte數) |

| ARBURST | master | 突發類型(FIXED,INCR,WRAP) |

| ARCACHE | master | 存儲類型 |

| ARPROT | master | 保護類型 |

| ARQOS | master | QoS標識符 |

| ARREGION | master | 區域標識符 |

| ARUSER | master | 用戶自定義 |

| ARVALID | master | 讀地址有效(有效時表示ARADDR上地址有效) |

| ARREADY | slave | 寫有效信號(有效時表示從機準備好接收讀地址) |

讀數據通道信號:

| 信號名 | 來源 | 描述 |

|---|---|---|

| RID | slave | 讀ID標簽 |

| RDATA | slave | 讀數據 |

| RRESP | slave | 讀響應 |

| RLAST | slave | 有效時表示為突發傳輸的最后一個 |

| RUSER | slave | 用戶自定義 |

| RVALID | slave | 讀數據有效信號 |

| RREADY | master | 主機就緒信號(有效時表示) |

b

寫架構

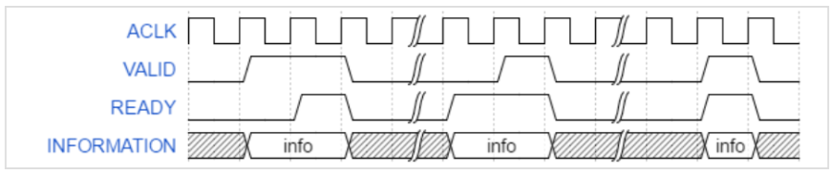

AXI使用基于VALID/READY的握手機制數據傳輸協議,傳輸源端使用VALID表明地址/控制信號、數據是有效的,目的端使用READY表明自己能夠接受信息。

- 讀/寫地址通道:讀、寫傳輸每個都有自己的地址通道,對應的地址通道承載著對應傳輸的地址控制信息。

- 讀數據通道:讀數據通道承載著讀數據和讀響應信號包括數據總線(8/16/32/64/128/256/512/1024 bit)和指示讀傳輸完成的讀響應信號。

- 寫數據通道:寫數據通道的數據信息被認為是緩沖(buffered)了的,master無需等待slave對上次寫傳輸的確認即可發起一次新的寫傳輸。寫通道包括數據總線(8/16...1024 bit)和字節線(用于指示8 bit 數據信號的有效性)。

- 寫響應通道:slave使用寫響應通道對寫傳輸進行響應。所有的寫傳輸需要寫響應通道的完成信號。

寫地址通道信號:

| 信號名 | 來源 | 描述 |

|---|---|---|

| AWID | master | 寫地址ID(用于區分該地址屬于哪個寫地址組) |

| AWADDR | master | 寫地址 |

| AWLEN | master | 突發長度 |

| AWSIZE | master | 突發尺寸(每次突發傳輸的最長byte數) |

| AWBURST | master | 突發方式(FIXED,INCR,WRAP) |

| AWCACHE | master | 存儲類型(標記系統需要的傳輸類型) |

| AWPROT | master | 保護模式 |

| AWQOS | master | QoS標識符 |

| AWREGION | master | region標識符(當slave有多種邏輯接口時標識使用的邏輯接口) |

| AWUSER | master | 用戶自定義信號 |

| AWVALID | master | 寫地址有效信號(有效時表示AWADDR上地址有效) |

| AWREADY | master | 寫從機就緒信號(有效時表示從機準備好接收地址) |

寫數據通道信號:

| 信號名 | 來源 | 描述 |

|---|---|---|

| WDATA | master | 寫數據 |

| WSTRB | master | 數據段有效(標記寫數據中哪幾個8位字段有效) |

| WLAST | master | last信號(有效時表示當前為突發傳輸最后一個數據) |

| WUSER | master | 用戶自定義信號 |

| WVALID | master | 寫有效信號(有效時表示WDATA上數據有效) |

| WREADY | slave | 寫ready信號(有效時表示從機準備好接收數據) |

寫響應通道信號:

| 信號名 | 來源 | 描述 |

|---|---|---|

| BID | slave | 響應ID |

| BRESP | slave | 寫響應 |

| BUSER | slave | 用戶自定義信號 |

| BVALID | slave | 寫響應信號有效 |

| BREADY | master | 寫響應ready(主機準備好接受寫響應信號) |

-

模塊

+關注

關注

7文章

2672瀏覽量

47345 -

AMBA

+關注

關注

0文章

68瀏覽量

14952 -

AXI

+關注

關注

1文章

127瀏覽量

16598

發布評論請先 登錄

相關推薦

深入剖析AXI的協議與架構(上)

深入剖析AXI的協議與架構(上)

評論