在FPGA開發過程中,我們常常會用到一些IP廠商提供的集成化模塊IP,通常情況下,這些IP經過了驗證,可通過一系列配置后直接使用。為方便廣大FPGA開發者、工程師、高校師生和相關企業做定制化開發,同時提高部分功能模塊工作性能,集成的IP通常采用業界比較規范的總線協議,完成功能處理和數據傳輸。目前,常用的IP基本上均提供AXI4、 AXI4-Lite和 AXI4-Stream接口。

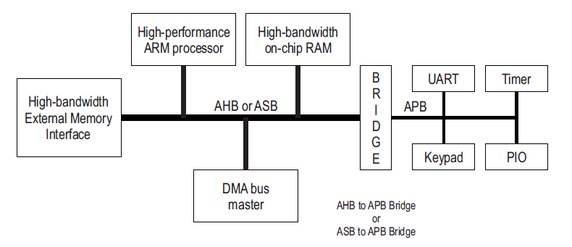

AXI(Advanced eXtensible Interface)是一種總線協議,該協議是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0協議中最重要的一部分,是一種面向高性能、高帶寬、低延遲的片內總線。2010發布的AMBA4.0包含了AXI的第二個版本AXI4。

AXI4包含3種類型的接口:

(1)AXI4:主要面向高性能地址映射通信的需求;

(2)AXI4-Lite:是一個輕量級的,適用于吞吐量較小的地址映射通信總線;

(3)AXI4-Stream:面向高速流數據傳輸。

其中,AXI4和AXI4-Lite在Block Design中常用,AXI4-Stream常用作IP接口。

AXI4協議的優勢:

(1)高效:通過標準化的AXI接口,開發者只需要學習一種IP核的通訊協議即可;

( 2)易用:針對具體應用提供合適的接口協議。

AXI4:面向地址映射的接口,在單地址傳輸的情況下最大允許256個時鐘周期的數據突發長度;

AXI4-Lite:一個輕量級的地址映射單次傳輸接口,占用較少的資源;

AXI4-Stream:去掉了地址傳輸的功能,允許無限制的數據突發傳輸,無需考慮地址映射。

(3)易得:標準化的AXI接口協議資源,不僅可以在xilinx官網上獲得,也可以在全球范圍內ARM的所有合作伙伴處獲得。

大量的IP Core支持AXI4協議;

大量的第三方AXI工具可提供多樣的系統開發、驗證和功能定制。

下面對AMBA協議規范中的AXI4、 AXI4-Lite和 AXI4-Stream進行解析。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602024 -

IP

+關注

關注

5文章

1664瀏覽量

149342 -

AMBA

+關注

關注

0文章

68瀏覽量

14953

發布評論請先 登錄

相關推薦

聊聊AMBA協議的evolution過程

AMBA?CXS協議規范

AMBA CHI協議介紹

AMBA LTI協議規范

SoC Designer Plus AMBA CHI協議包的用戶指南

AMBA 3.0 AXI總線接口協議的研究與應用

什么是AMBA?

快速了解最新的AMBA AXI5協議功能

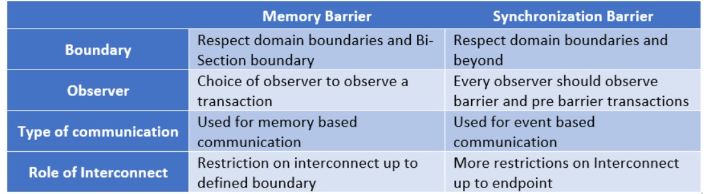

跨越驗證AMBA ACE協議屏障事務的障礙

Arm AMBA AXI-K規范中的一些功能更新

Arm和新思科技繼續就AMBA協議系列的最新擴展密切合作

AMBA協議規范解析

AMBA協議規范解析

評論