前言

Verdi是一個功能強大的debug工具,可以配合不同的仿真軟件進(jìn)行debug,很多企業(yè)常用VCS+Verdi或者Xcelium/xrun+Verdi的方式進(jìn)行代碼的仿真與檢查。Verdi支持對所有設(shè)計和驗證流程進(jìn)行全面的調(diào)試。它能夠幫助工程師理解復(fù)雜和不熟悉的設(shè)計行為,讓困難和乏味的調(diào)試過程自動化,并能讓多樣和復(fù)雜的設(shè)計環(huán)境一致化。在芯片設(shè)計過程中,可以根據(jù)仿真結(jié)果檢查或者理解設(shè)計;在芯片驗證過程中,常常用來調(diào)試(debug)一些錯誤的情況。Verdi既可以閱讀調(diào)試代碼,又可以查看波形,包括數(shù)字設(shè)計的波形和模擬設(shè)計的波形。

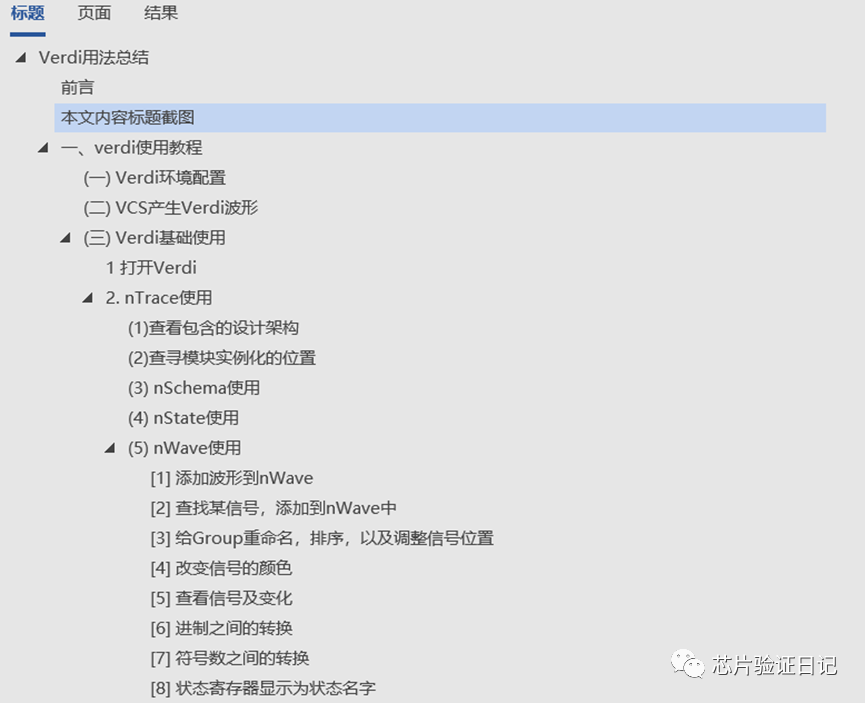

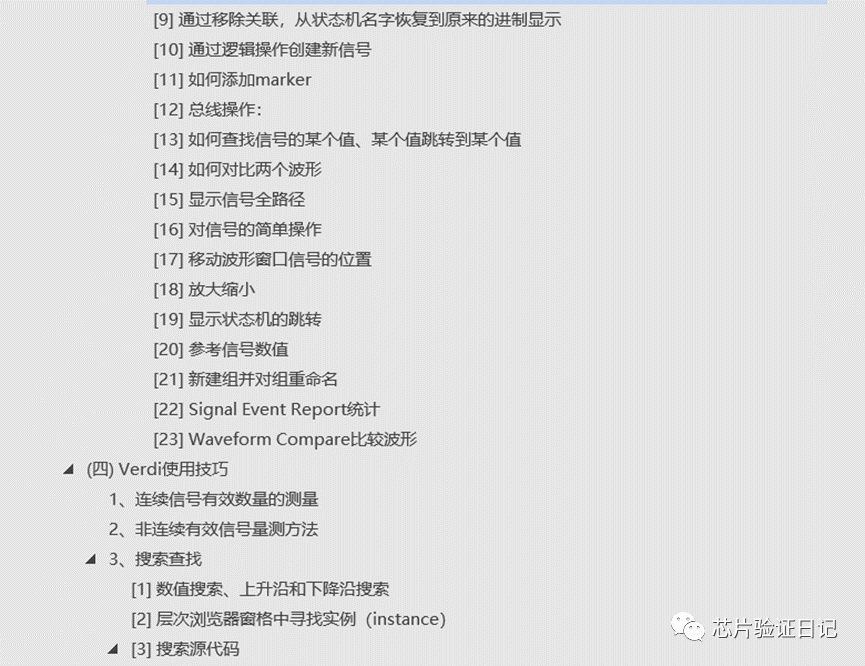

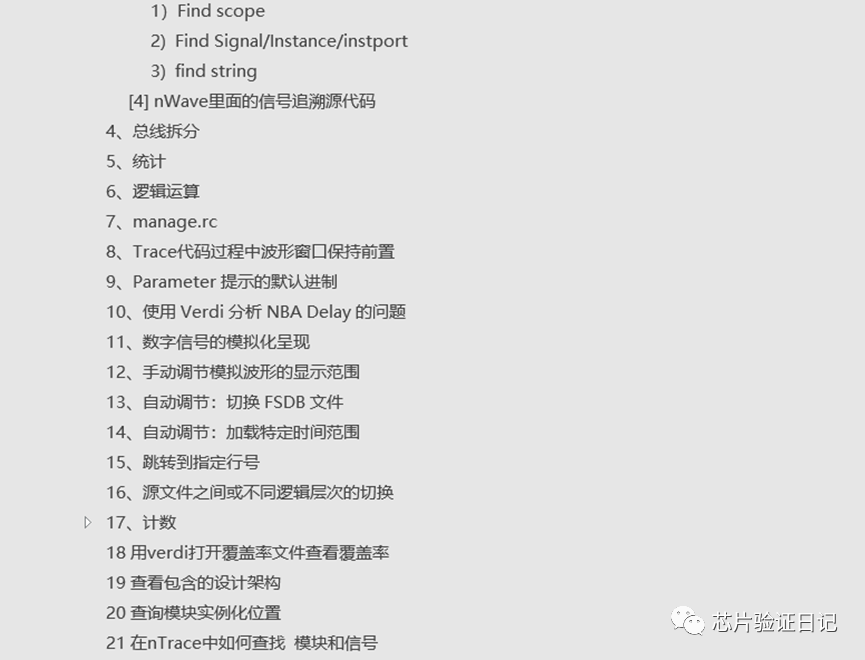

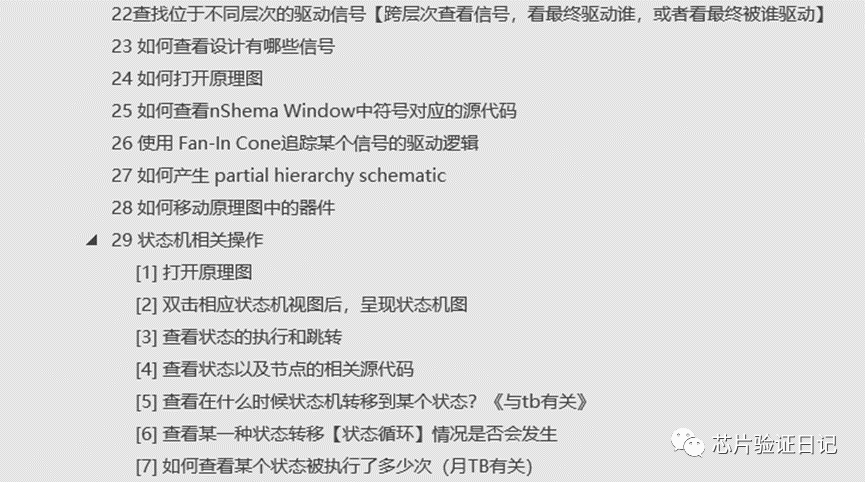

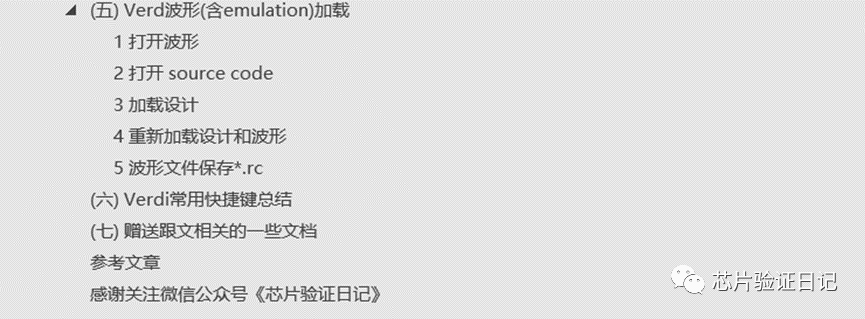

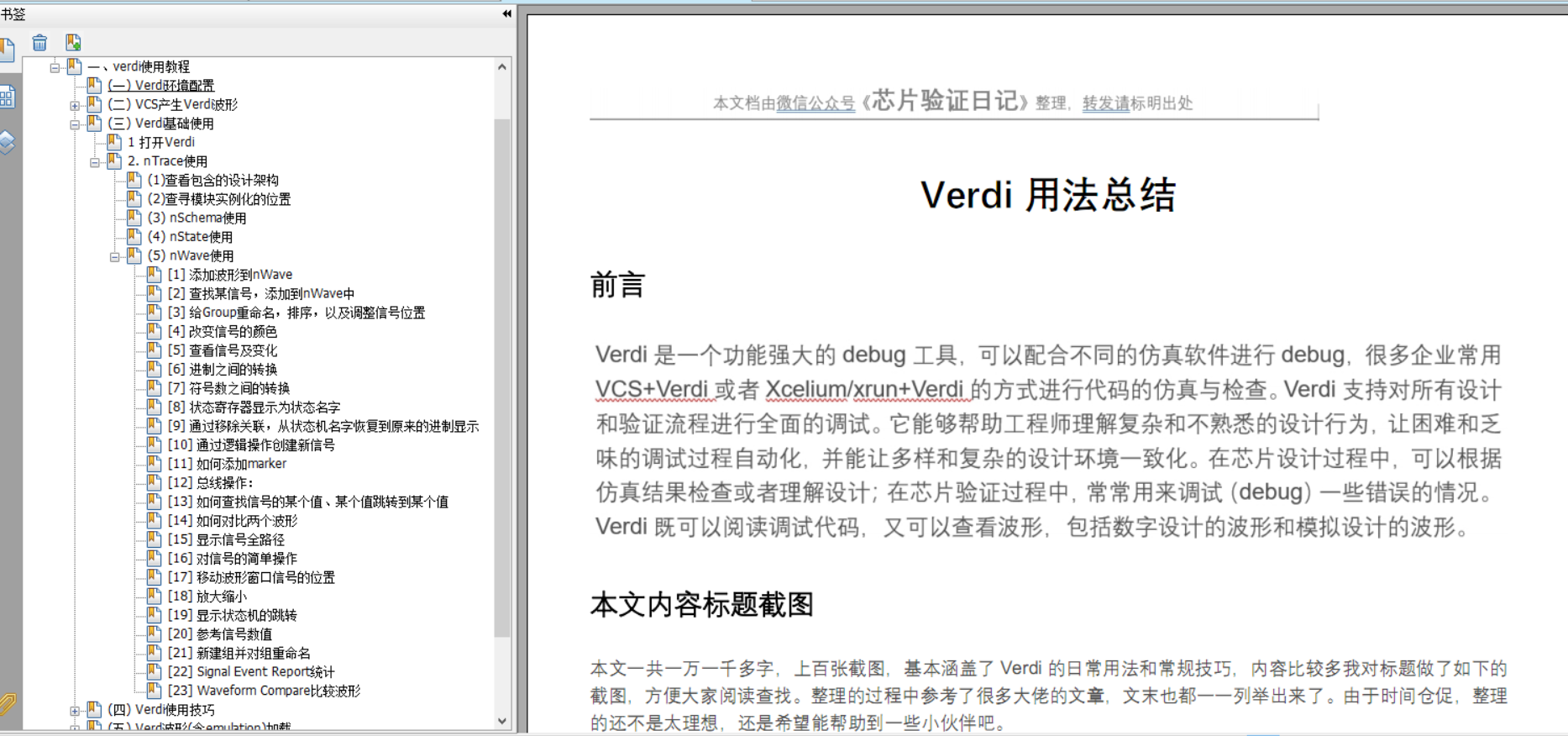

本文內(nèi)容標(biāo)題截圖

本文一共一萬一千多字,上百張截圖,基本涵蓋了Verdi的日常用法和常規(guī)技巧,內(nèi)容比較多我對標(biāo)題做了如下的截圖,方便大家閱讀查找。整理的過程中參考了很多大佬的文章,文末也都一一列舉出來了。由于時間倉促,整理的還不是太理想,還是希望能幫助到一些朋友吧。

一、verdi使用教程

(一) Verdi環(huán)境配置

bashrc中配置

export Verdi_HOME=$Synopsys_Dir/Verdi2015

# export NOVAS_HOME=$Synopsys_Dir/Verdi2015

export PATH=$Verdi_HOME/bin:$PATH

export LD_LIBRARY_PATH="/opt/Synopsys/Verdi2015/share/PLI/lib/linux64"$PATH

export LD_LIBRARY_PATH="/opt/Synopsys/Verdi2015/share/PLI/VCS/linux64"$PATH

上面三個環(huán)境變量的解釋:

VERDI_HOME/NOVAS_HOME:仿真器默認(rèn),且為設(shè)置PATH做準(zhǔn)備

PATH:讓系統(tǒng)(Linux)找到verdi

LD_LIBRARY_PATH:讓系統(tǒng)(Linux)能夠找到Verdi需要的庫文件.so(靜態(tài)庫),.a(動態(tài)庫),.tab(表格文件).

(二)VCS產(chǎn)生Verdi波形

[1] 使用Verilog系統(tǒng)函數(shù),在tb****文件中加入相應(yīng)的系統(tǒng)函數(shù)

initial begin

$fsdbDumpfile("fifo.fsdb");

$fsdbDumpvars(0);

end

[2] 使用UCLI、TCL接口(VCS使用tcl腳本)

global env

fsdbDumpfile "$env(demo_fifo).fsdb"

fsdbDumpvars 0 "top_tb"

run

(三) Verdi基礎(chǔ)使用

1 打開Verdi

(1)verdi -nologo

(2)makefile命令

2. nTrace使用

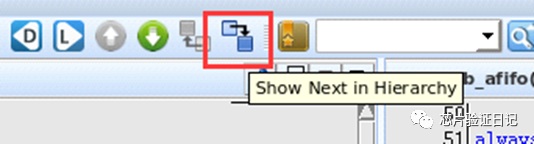

(1)查看包含的設(shè)計架構(gòu)

(2)查尋模塊實例化的位置

①在設(shè)計結(jié)構(gòu)中雙擊實例化模塊的名字->源代碼窗口高亮了模塊名

②再雙擊高亮的模塊名->看到在上層模塊中的哪一行被調(diào)用了

在nTrace中查找模塊和信號

查尋字符串

查看驅(qū)動信號相關(guān)

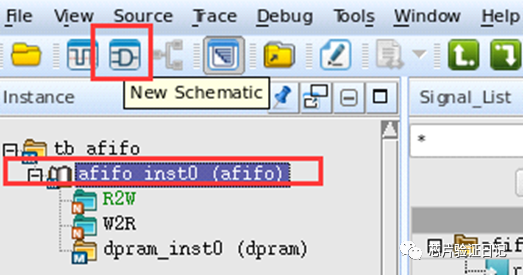

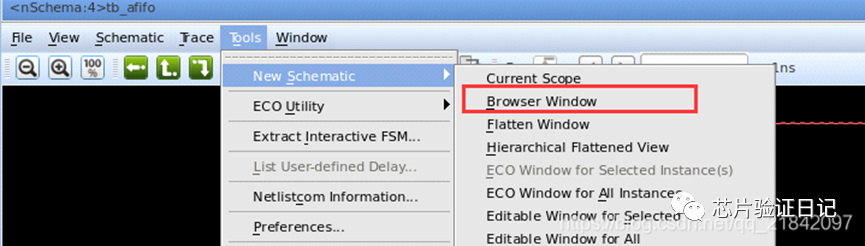

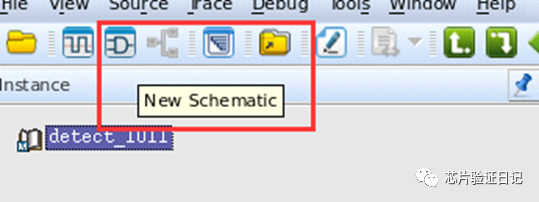

(3) nSchema使用

查看原理圖

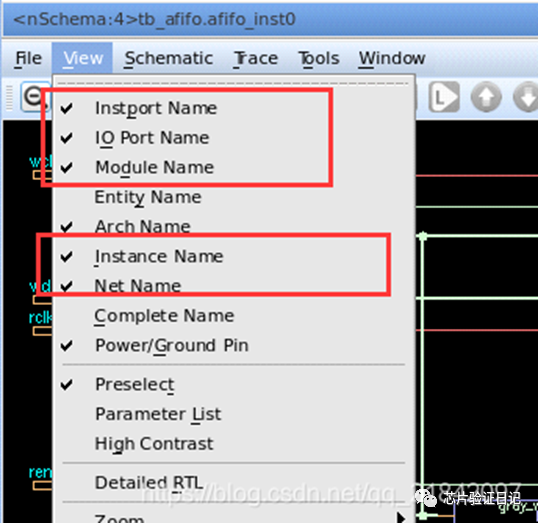

顯示原理圖各信號名

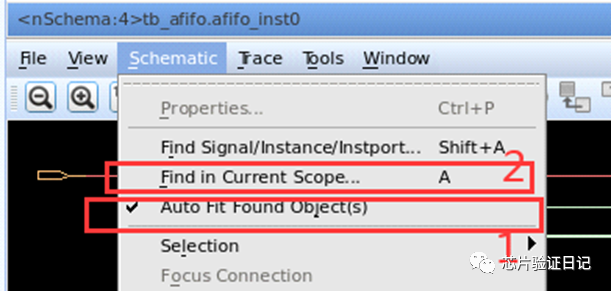

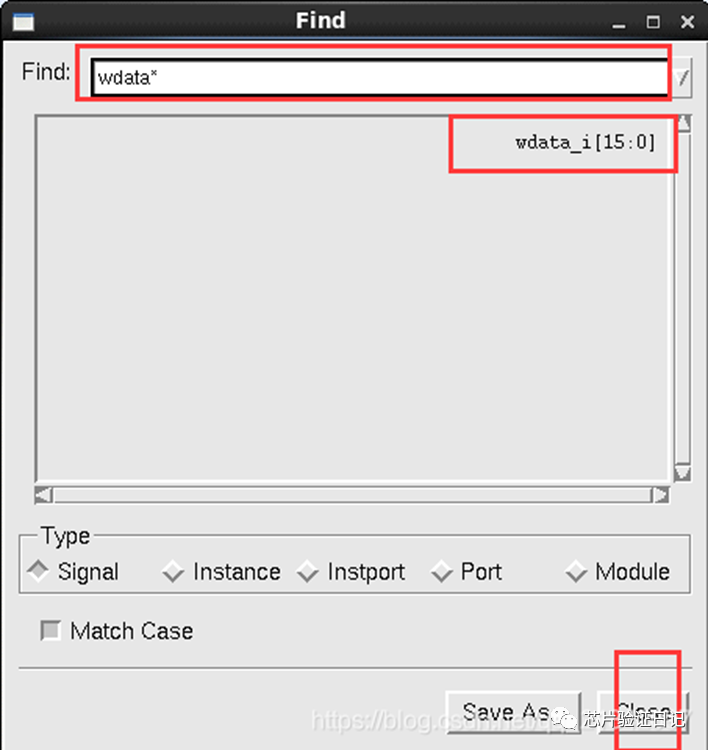

RTL 級 : 在當(dāng)前的層次中查找某個信號

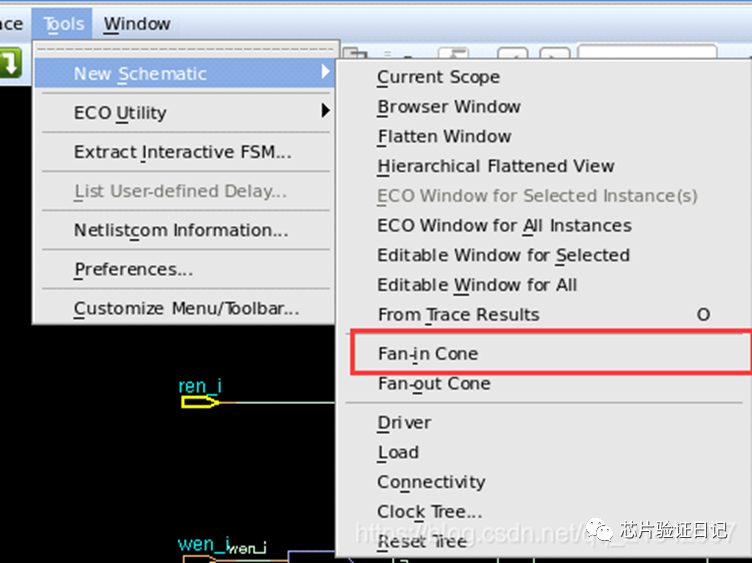

使用Fan-In Cone追蹤某個信號的驅(qū)動邏輯

①首先要用上面的辦法來查找信號②調(diào)用該工具:

產(chǎn)生partial hierarchy schematic

用來查看與選擇特定信號有關(guān)的邏輯/模塊

①選擇需要查看的信號(可以通過shift鍵來選擇多個信號)

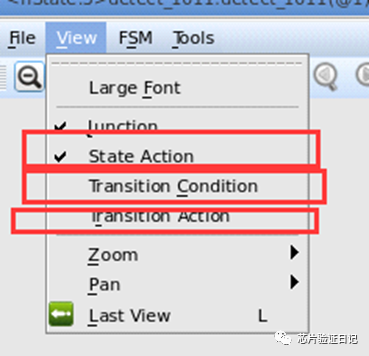

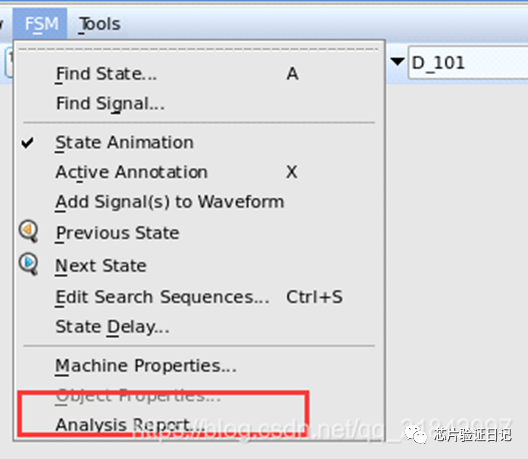

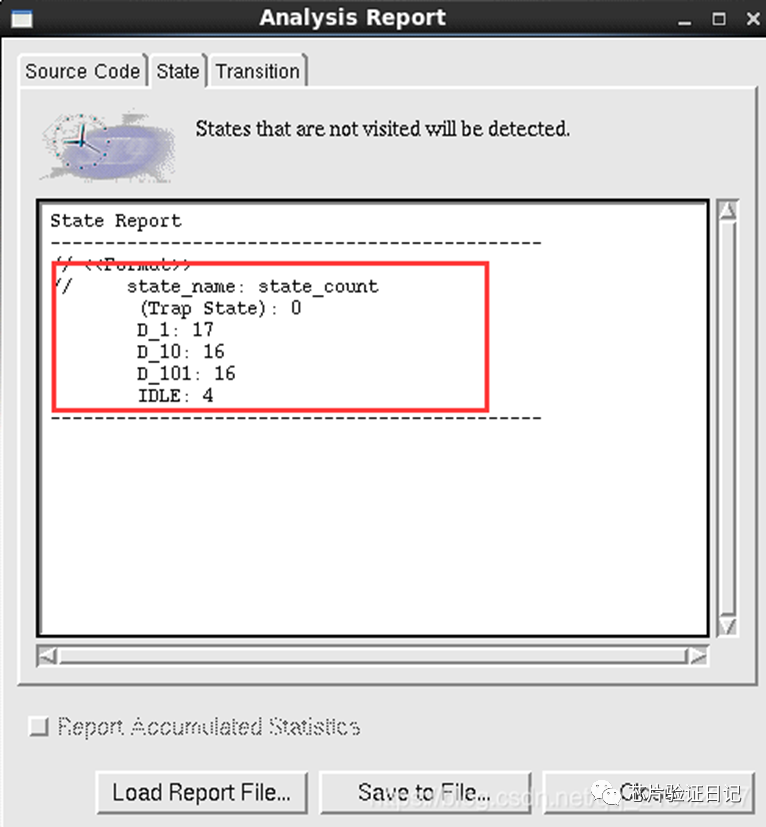

(4) nState使用

查看狀態(tài)機視圖

查看狀態(tài)的執(zhí)行語句和轉(zhuǎn)移條件

查看某個狀態(tài)的執(zhí)行次數(shù)

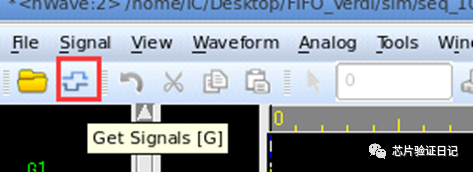

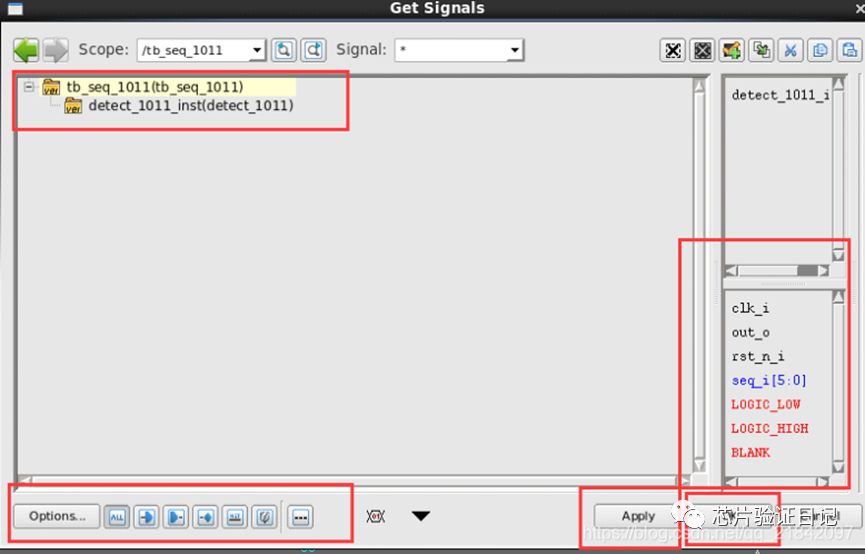

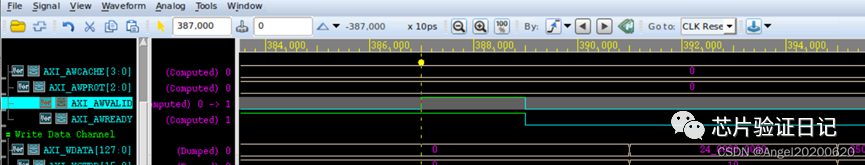

(5) nWave使用

[1] 添加波形到nWave

①我們要打開.v文件

②打開nWave然后打開.fsdb波形文件③正式添加波形:

快捷鍵G或者:

在nTrace中選中信號后,鼠標(biāo)中鍵拖拽,或者ctrl+w進(jìn)行添加

自動加載,用-ssf 命令

verdi -sv -f filelist.f -top tb_top -ssf dut.fsdb &

[2] 查找某信號,添加到nWave中

①通過nTrave查找到該信號②通過上面的方法進(jìn)行添加或者通過get signal來查找

nWave波形窗口,快捷鍵 g 加載信號(Get signals)。在彈出的窗口選中需要添加的信號,點擊滾輪選擇需要添加信號的位置,也可在代碼中(nTrac界面)選中信號 Ctrl+W 將信號加載在波形中

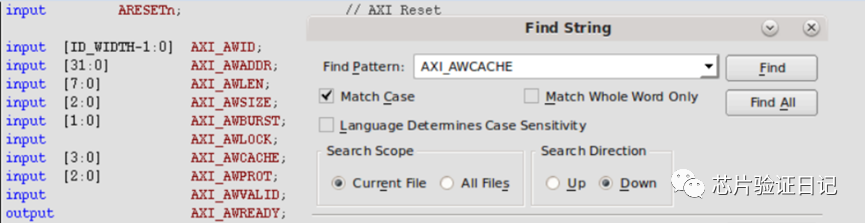

[2--]查找信號

找到模塊里的某個信號,按?彈出find string對話框進(jìn)行查找。

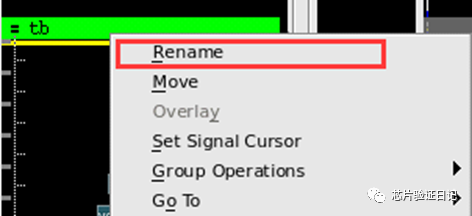

[3] 給Group重命名,排序,以及調(diào)整信號位置

[1]重命名

[2]信號的拖拽:通過鼠標(biāo)中鍵進(jìn)行拖拽。

[3]縮小:快捷鍵z,或者100%匹配:F

[4]放大:左鍵拖選放大范圍shift+Z ctrl+滑輪:進(jìn)行放大或者縮小

[5]移動:鼠標(biāo)中鍵按住信號拖拽中鍵選擇位置:

[6]復(fù)制:ctrl+P,或者右擊信號,選擇復(fù)制的選項

[7]粘貼:ins鍵,或者右擊信號,選擇粘貼的選項(注意:可以通過鼠標(biāo)中鍵選擇粘貼的位置)

[8]刪除:delete鍵

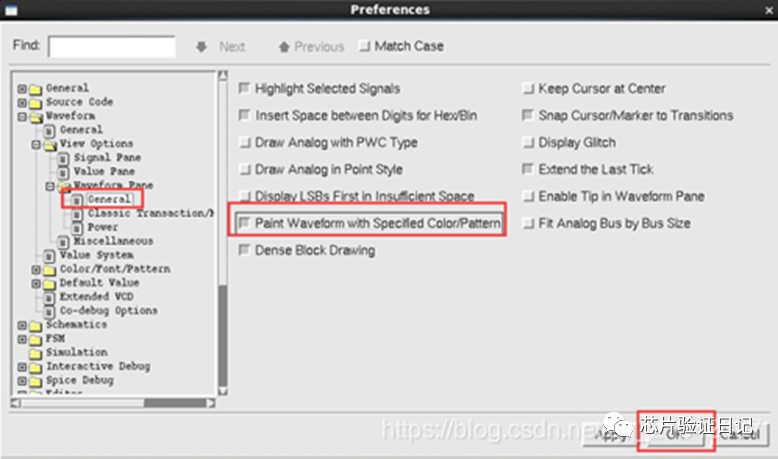

[4] 改變信號的顏色

第一步:Tools->preferences->waveform->viewoption->waveformpane->general->paint waveform with specified color/pattern

第二步:選中信號,然后按快捷鍵C改變信號顏色。

按C或者T修改信號或者波形顏色,按****T 更實用 ,每按一次顏色自動改變。不區(qū)分大小寫。

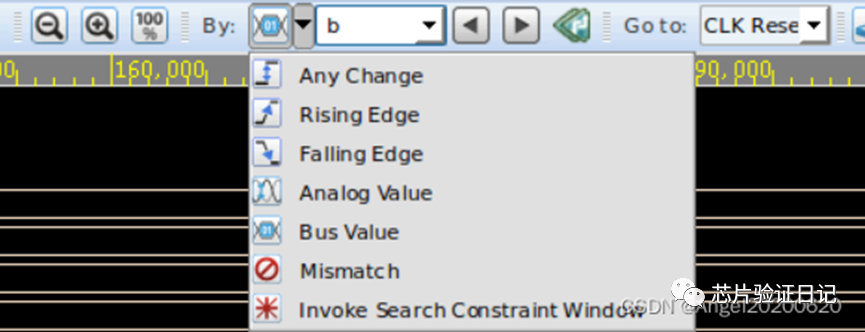

[5] 查看信號及變化

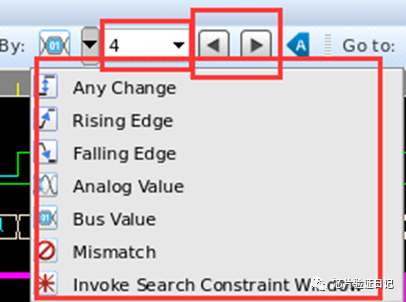

任意值:所有信號變化,一般會應(yīng)用到組合邏輯的指示信號信號沿:用于查找有效指示信號,比如使能信號總線值:主要是用來查找數(shù)據(jù)信號模擬值:查看比如函數(shù)發(fā)生器產(chǎn)生的正弦波信號進(jìn)制之間的轉(zhuǎn)換:

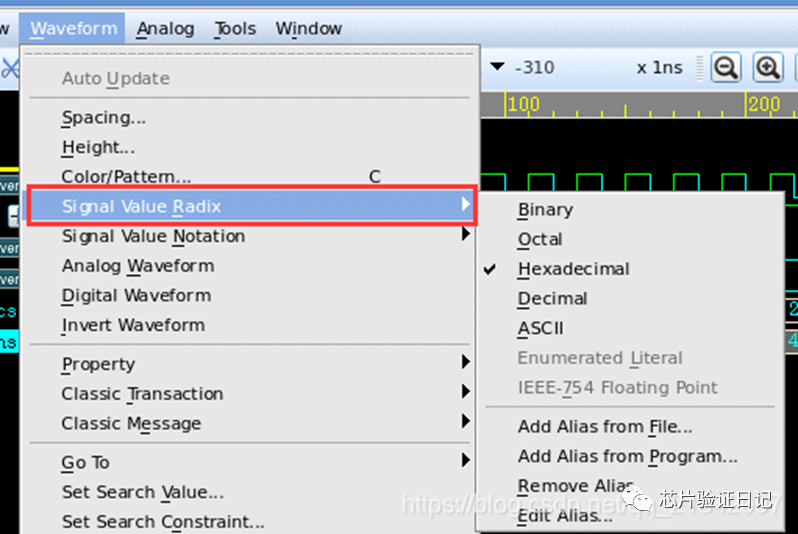

[6] 進(jìn)制之間的轉(zhuǎn)換

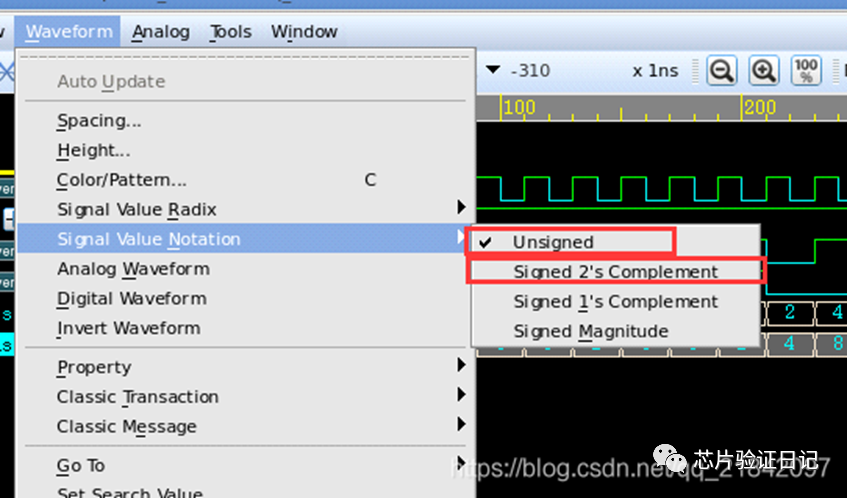

[7] 符號數(shù)之間的轉(zhuǎn)換

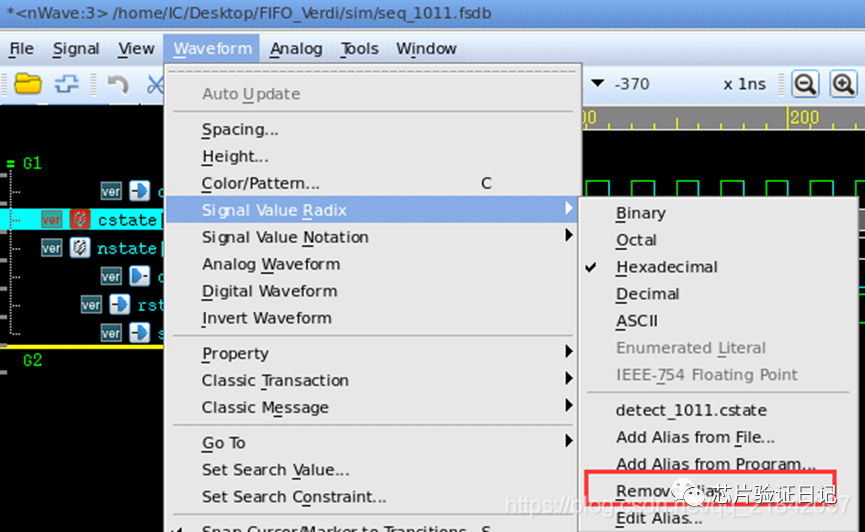

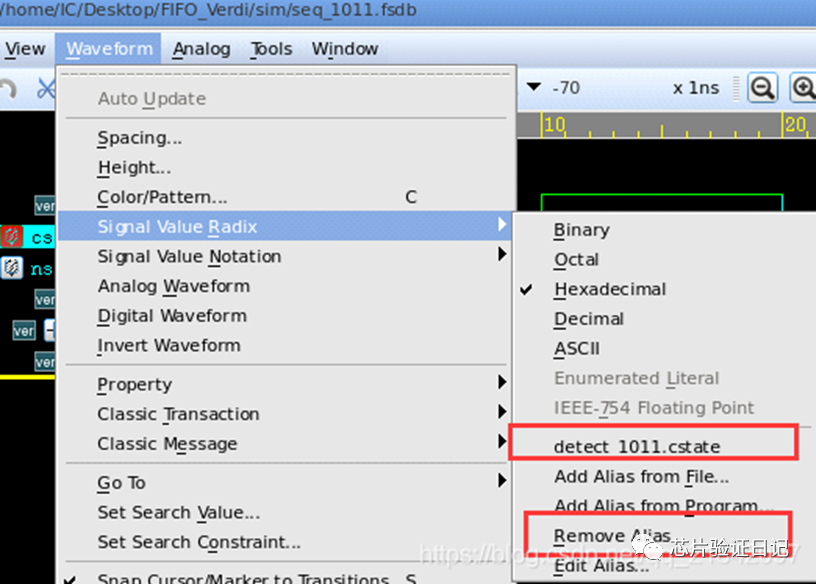

[8] 狀態(tài)寄存器顯示為狀態(tài)名字

nTrace:

或者nWave:

[9] 通過移除關(guān)聯(lián),從狀態(tài)機名字恢復(fù)到原來的進(jìn)制顯示

可以看到,我們打開過狀態(tài)機視圖之后,我們也就可以在狀態(tài)名和進(jìn)制之間轉(zhuǎn)換了:

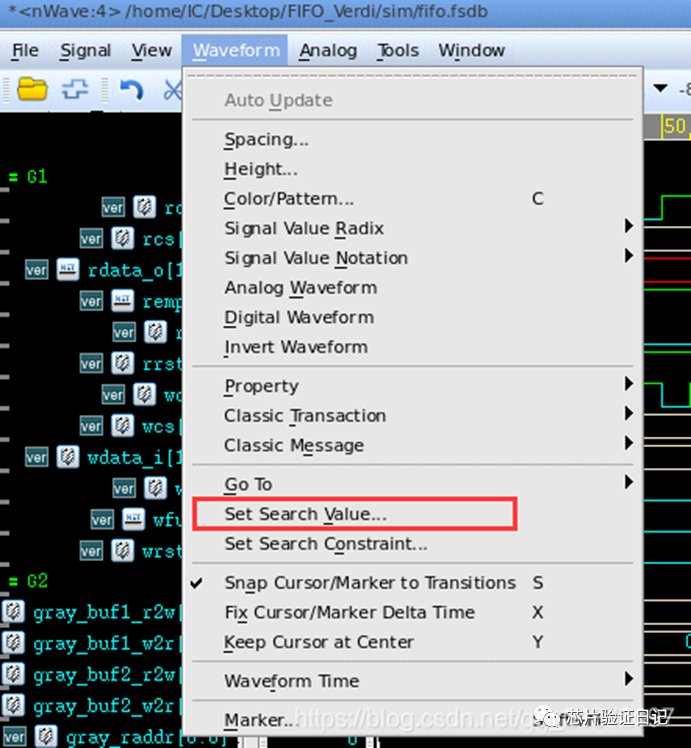

[10] 通過邏輯操作創(chuàng)建新信號

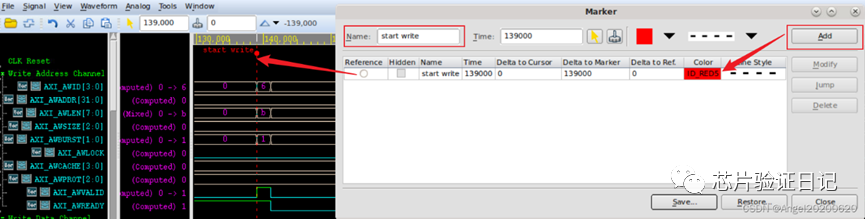

[11] 如何添加marker

shift+M。為方便波形定位,按鍵shift+M使用mark功能標(biāo)記一下,可以自定義名稱和顏色,方便查找。

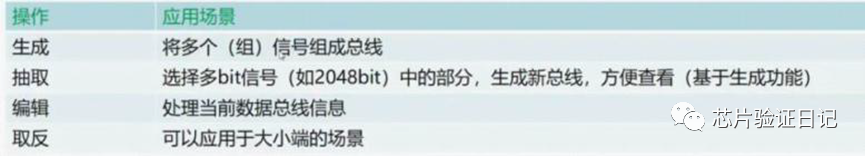

[12] 總線操作:

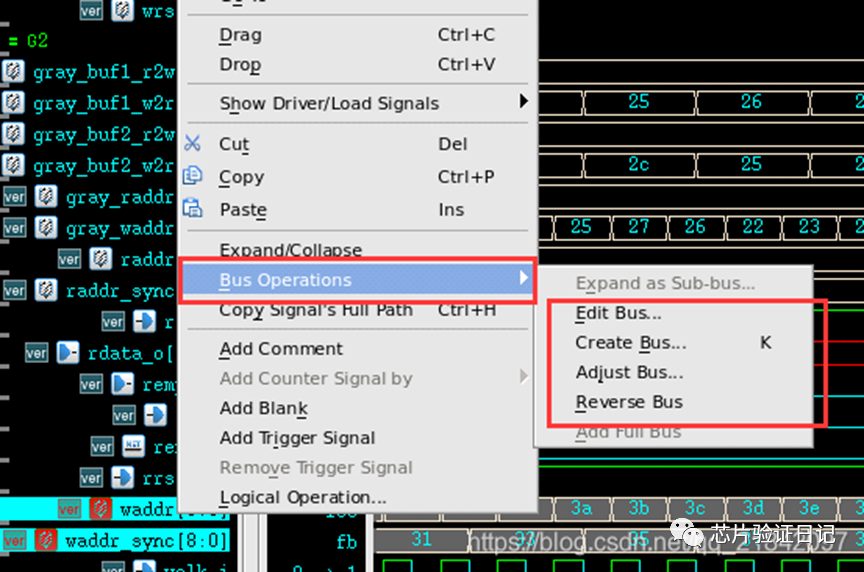

[13] 如何查找信號的某個值、某個值跳轉(zhuǎn)到某個值

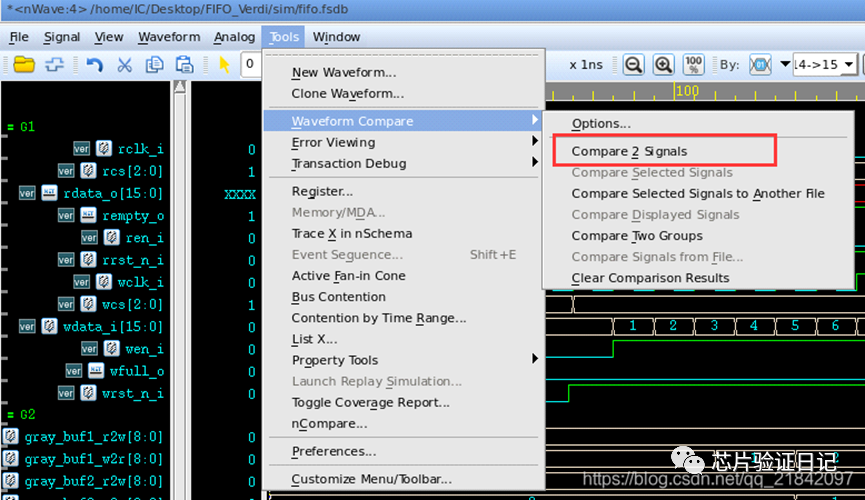

[14] 如何對比兩個波形

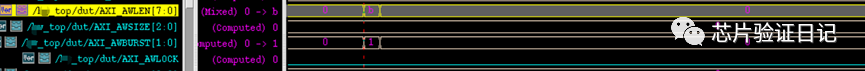

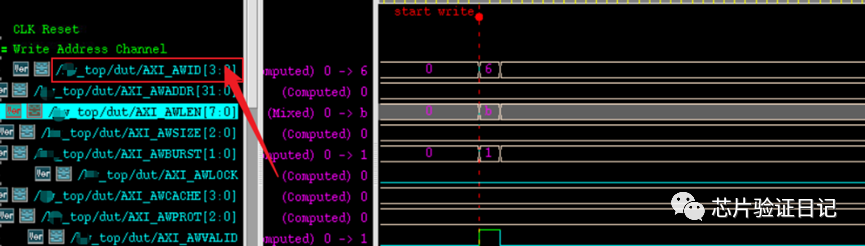

[15] 顯示信號全路徑

按 **=H=** 顯示波形信號全路徑,再按**H**撤銷。不區(qū)分大小寫。

[16] 對信號的簡單操作

點擊波形窗口,選中信號,使用Delete刪除信號。選中信號,使用Ctrl+p復(fù)制選中的信號,然后使用insert按鍵插入,粘貼的位置由黃線所在位置決定。

[17] 移動波形窗口信號的位置

使用滾輪在波形窗口選中信號,然后拖到代碼窗口即可查看選中波形的代碼邏輯

[18] 放大縮小

Z:Zoom In;z:Zoom Out;f:Zoom All

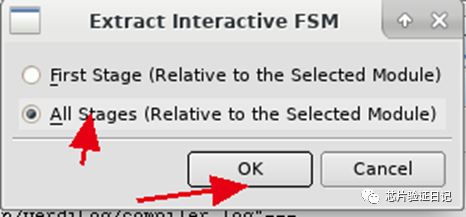

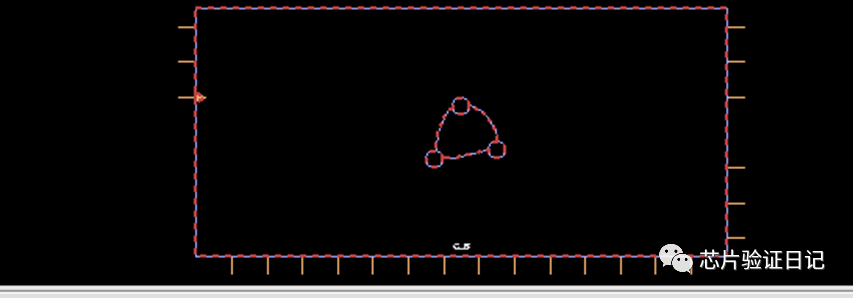

[19] 顯示狀態(tài)機的跳轉(zhuǎn)

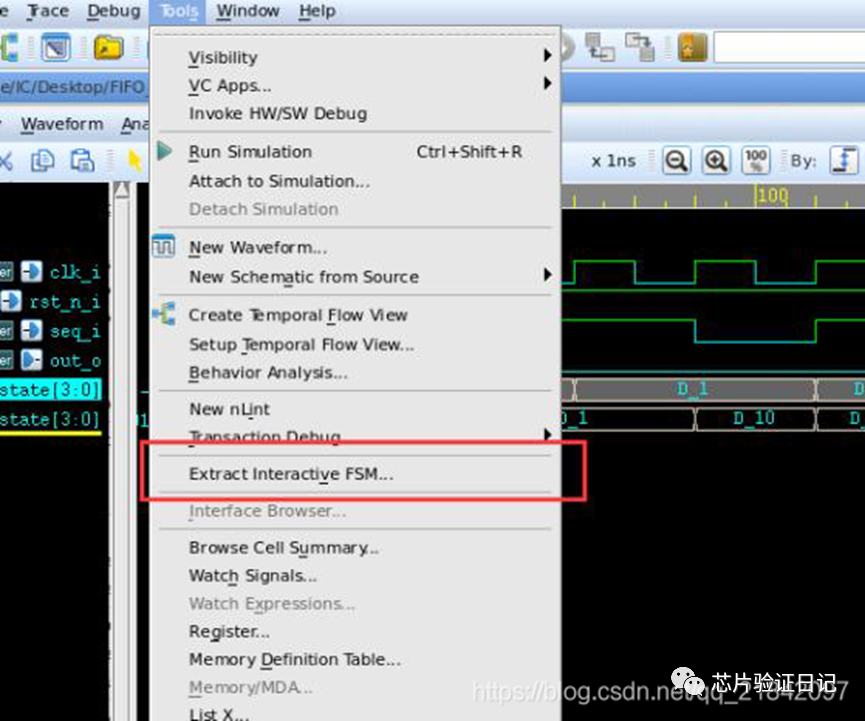

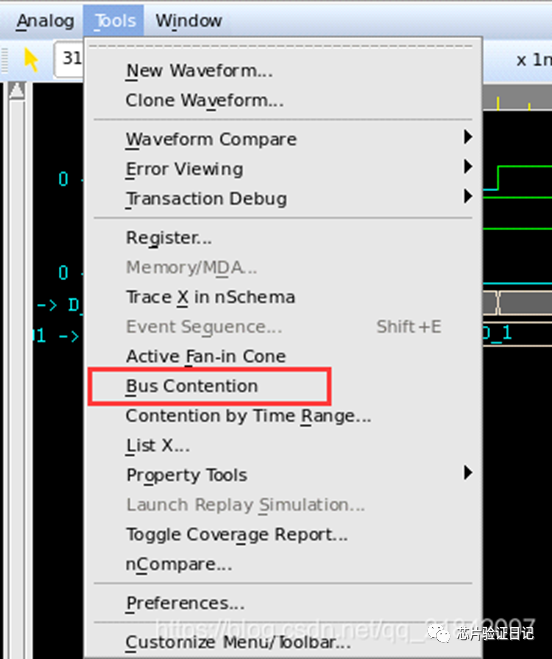

選中狀態(tài)機狀態(tài)的波形,在nWave窗口選中Tools>Bus Contention>打開狀態(tài)機,(關(guān)閉), 返回查看波形已經(jīng)變?yōu)闋顟B(tài)的名稱。 補充:選擇具有狀態(tài)機的模塊選中,然后在主工具欄選擇Tools>Extract interative FSM

點擊OK,然后點擊下面的狀態(tài)機,即可看到狀態(tài)的跳轉(zhuǎn)。

[20] 參考信號數(shù)值

選中Source>Active Annotation即可看到每一個信號,參數(shù)的數(shù)據(jù)顯示。

[21] 新建組并對組重命名

將黃線放到最后一行,添加信號即可新建一個信號組。然后鼠標(biāo)選中右鍵即可進(jìn)行相關(guān)操作,也可以選中一個模塊,直接Ctrl+4即可將接口信號加入波形窗口。

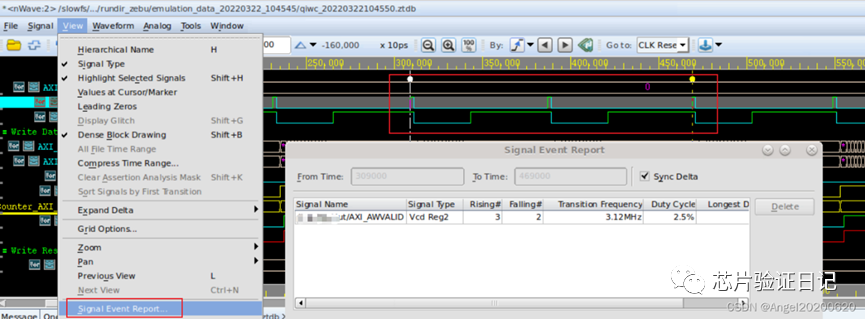

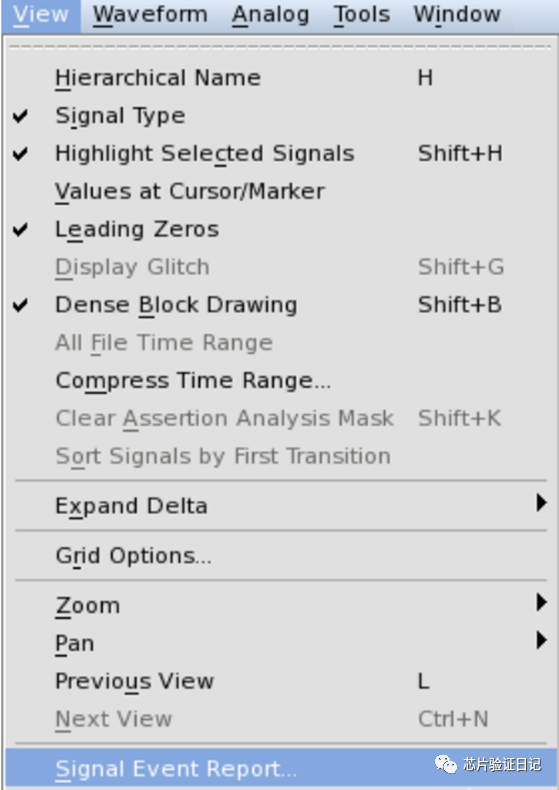

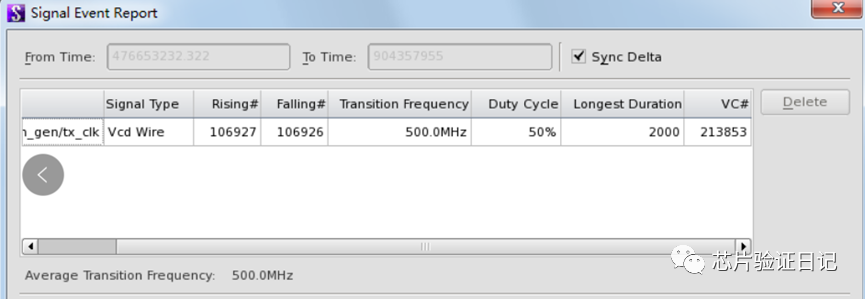

[22] Signal Event Report統(tǒng)計

統(tǒng)計出某個信號在特定時間段內(nèi)的跳變的次數(shù)。

按鼠標(biāo)滑輪中建,添加一條mark標(biāo)記線用于選擇統(tǒng)計區(qū)間。

View -> Signal Event Report

Rising:指的是指定Marker時間段內(nèi)上升沿數(shù);

Falling:指的是指定Marker時間段內(nèi)下降沿數(shù);

=備注:利用Logical Operation和Signal Event Report可以統(tǒng)計非連續(xù)有效信號=

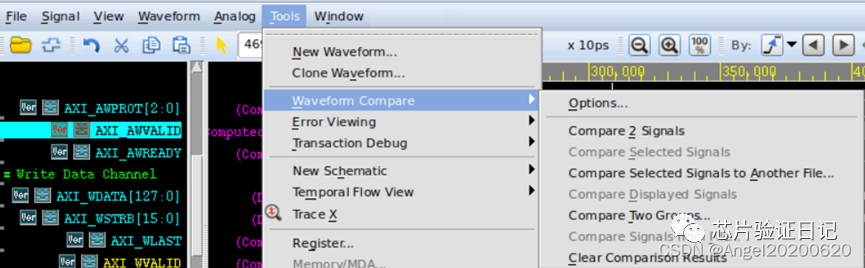

[23] Waveform Compare比較波形

nWave提供了一種綜合比較自動比較不同結(jié)果的能力。在比較完成后,nWave以圖形方式顯示波形窗格中的任何不匹配,然后可以通過每個不匹配來分析差異。

Tools -> Waveform Compare

(四) Verdi使用技巧

1、連續(xù)信號有效數(shù)量的測量

[1] 下面分享一些在實際做項目過程中verdi在debug時的小技巧:連續(xù)信號有效數(shù)量的測量。

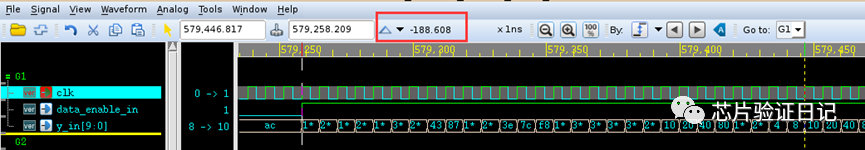

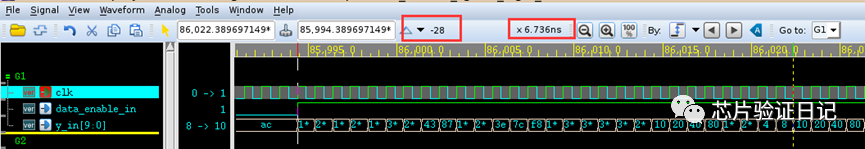

如下圖所示,clk是輸入時鐘信號,data_enable_in是輸入數(shù)據(jù)有效標(biāo)志信號,y_in則是輸入數(shù)據(jù)。在debug的時候,有時我們想要知道白色光標(biāo)和黃色光標(biāo)時間內(nèi)有多少個連續(xù)有效的數(shù)據(jù)y_in。我們該如何做到呢?

一般可以使用以下3種方法:

方法1:最直接也是最笨的辦法,當(dāng)然是手動去數(shù),1、2、3…;如果該時間段內(nèi),數(shù)據(jù)量較少,很快就可以數(shù)出來了。當(dāng)數(shù)據(jù)量較多時,只要你有足夠的耐心和時間,有時還需要一副好眼睛,最終也是可以得到正確的結(jié)果。不過效率非常低下,比較麻煩的是還容易數(shù)錯。

方法2:如果已知時鐘周期(本例子中clkp=6.736ns),則可以計算該時間段內(nèi)時鐘個數(shù)來獲知數(shù)據(jù)量;上面例子的圖中兩個光標(biāo)之間的時間差delta=188.608ns,delta/T=28,因此就是28個數(shù)據(jù)了。是不是要比直接用手動數(shù)快很多了?這個辦法雖然準(zhǔn)確,但是每次都要計算一次,如果需要頻繁的獲知不同時間段內(nèi)的有效數(shù)據(jù)還是太麻煩了一點。

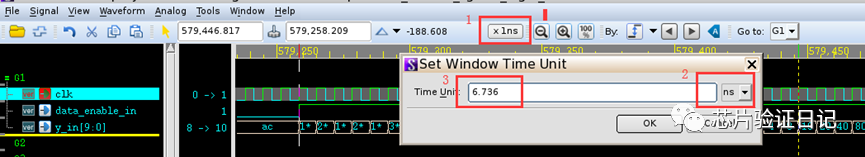

方法3:本文重點要介紹的方法。該方法是通過把時鐘周期設(shè)置為時間單位,這樣兩個光標(biāo)之間的時間差就是該段時間內(nèi)的有效數(shù)據(jù)量了。具體操作方法如下:

如下圖用鼠標(biāo)點擊1,會彈出對話框;點擊2位置倒三角形,下拉選項中選時鐘周期單位是ns;然后再把timeunit 改為clock周期6.736ns,點擊OK.

再看delta顯示出來的值,已經(jīng)變成28了,即為我們要的數(shù)據(jù)量了。

這個方法對于一段時間內(nèi)的連續(xù)有效數(shù)據(jù)來說,應(yīng)該是最簡單有效的獲取數(shù)據(jù)個數(shù)的方法了。任意改變兩光標(biāo)的距離或位置,都很直接的得到該段時間內(nèi)的連續(xù)有效數(shù)據(jù)量。該方法在debug過程中常常會用到,請大家善加利用。

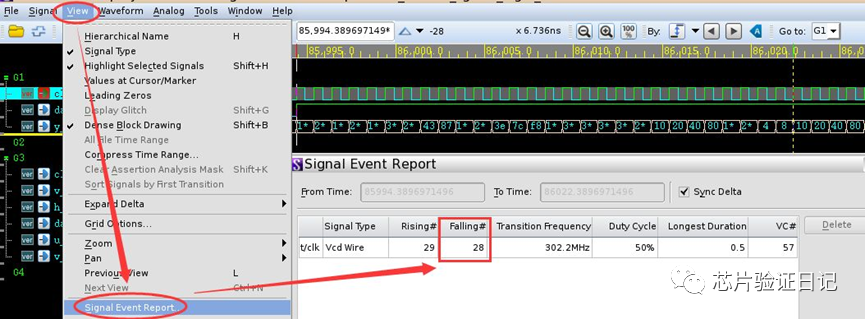

[2]另外還有一個比較有效的辦法是利用verdi的nWave里面的Signal Event Report 功能。該方法雖然稍顯麻煩,但善于利用,也可以變得非常好用。方法如下圖:

a.鼠標(biāo)點擊選中clk 這個信號;b.點擊view菜單,選擇下拉菜單里面的SignalEvent report,就會彈出對話框;c.進(jìn)度條往后拖,會看到Falling#這一欄顯示的數(shù)據(jù)28就是我們要的數(shù)據(jù)量了。

以上就是一段時間內(nèi)連續(xù)有效數(shù)據(jù)的幾個測量方法。debug的時候方法3最簡單便捷,應(yīng)用頻率也較高;但是其他幾個方法在特定的場景下也可以發(fā)揮出自己的作用,需要根據(jù)實際debug的時候靈活應(yīng)用。

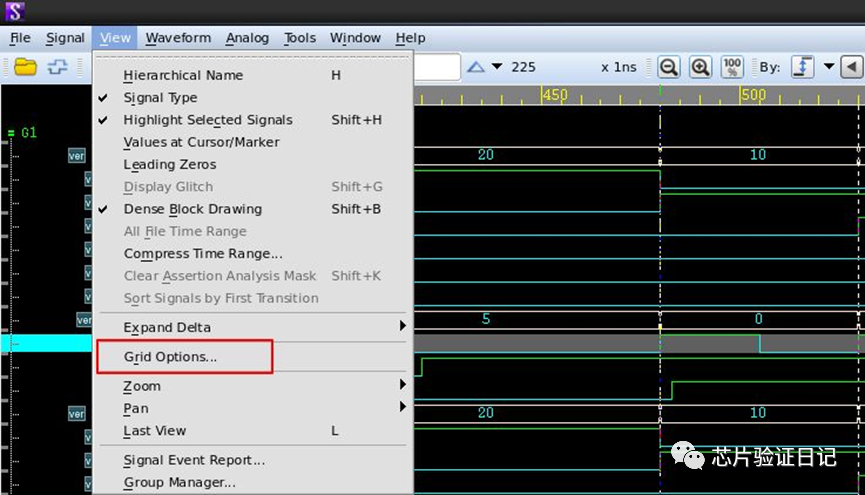

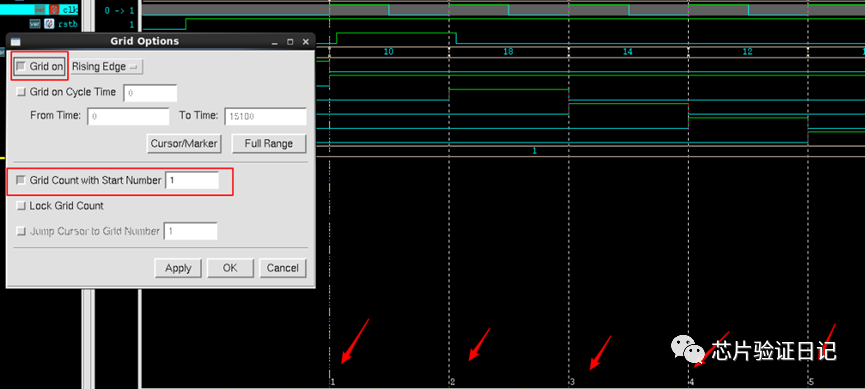

[2]網(wǎng)格法

點擊菜單里面的view選項,選擇Grid Options,如下圖所示:

選中選項Grid on 以及選項Grid Counter with Start Number,如下圖所示,點擊Apply或者OK之后,就可以看到波形里面出現(xiàn)了網(wǎng)格,最下面有數(shù)字出現(xiàn)。這種方法還有一個好處是鼠標(biāo)左鍵點到CLK信號的任意位置,計數(shù)都是從新的地方開始,具有很強的靈活性。

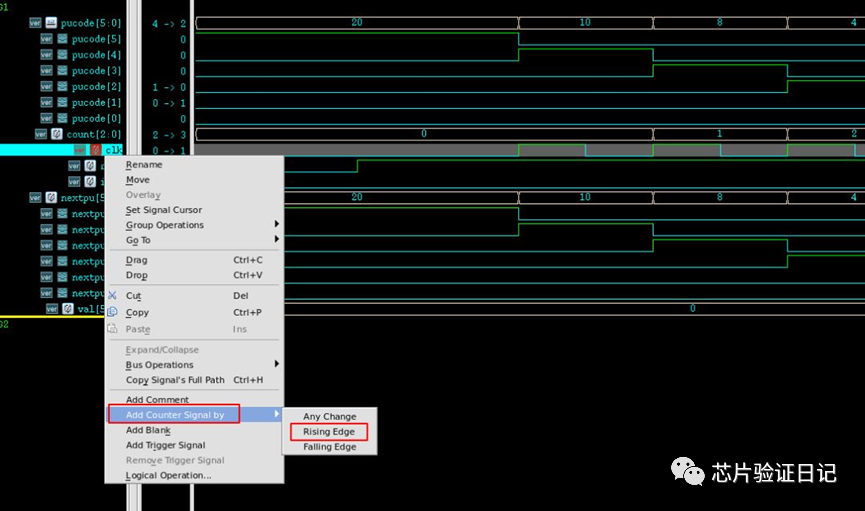

[4] 自動添加計數(shù)器:

右擊CLK信號,選擇Add Counter Signal by,選擇上升沿、下降沿、任意沿中的一個,就會自動產(chǎn)生一個16進(jìn)制的計數(shù)信號,不過它的計數(shù)起點是從CLK的0時刻開始,不能選擇任意時刻,所以缺乏靈活性。

關(guān)于方法3和方法4,更推薦方法3網(wǎng)格法,看起來很強大,大家可以繼續(xù)探索探索。

[5]打開路徑下的verdi.cmd記錄了上一次的全部動作。如果verdi意外關(guān)閉,可以使用verdi -play verdi.cmd來復(fù)原。

[6]可以給clk的上升沿打上標(biāo)記(好像叫l(wèi)abel),在兩個光標(biāo)之間會顯示標(biāo)記的個數(shù),也就是周期數(shù)。

2、非連續(xù)有效信號量測方法

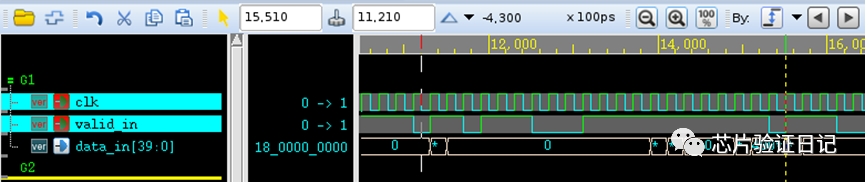

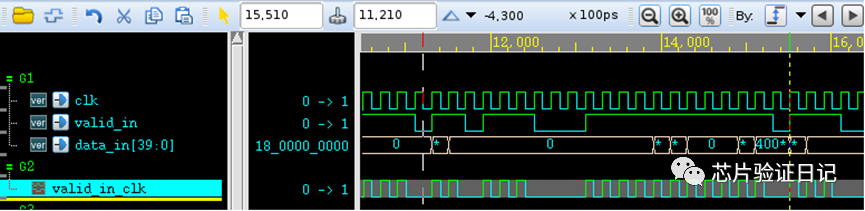

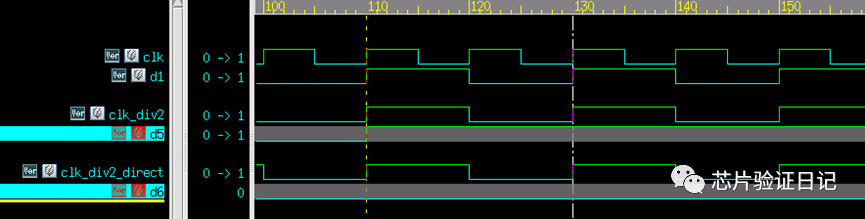

實際debug過程中,更常遇到的場景是 非連續(xù)有效的信號 ,如下圖所示:CLK并不是在每個時刻都是有效的,這時我們又該如何比較快速準(zhǔn)確的獲知某個時間段內(nèi)有效信號(CLK)個數(shù)呢?

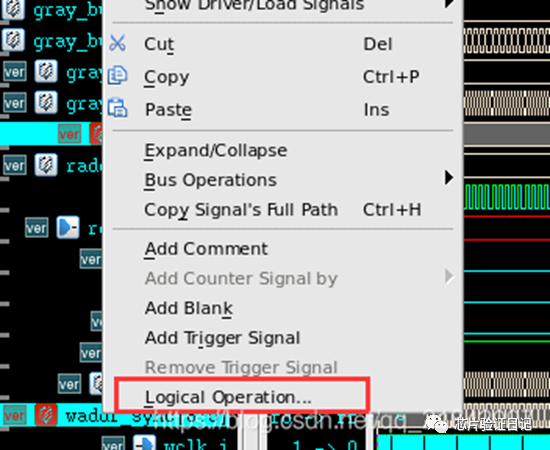

跟獲取連續(xù)有效信號個數(shù)一樣,如果某個時間段內(nèi)有效信號個數(shù)較少(比如少于10個),直接手動數(shù)就可以了。當(dāng)有效信號toggle次數(shù)比較多時,肉眼無法快速看出數(shù)量的時候,我們可以利用Verdi nWave里面的Logical operation 和Signal Event report 這兩個功能來實現(xiàn)。

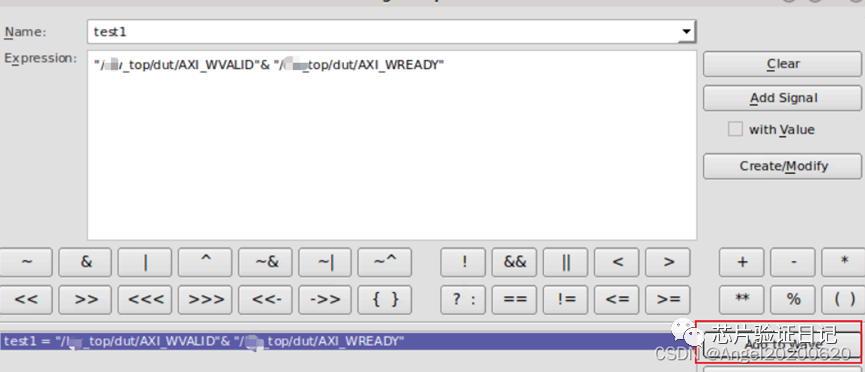

對于非連續(xù)有效數(shù)據(jù)傳輸,通常會有一個信號來標(biāo)志哪筆數(shù)據(jù)是有效的,如上圖中的valid_in信號為1時表示data_in數(shù)據(jù)有效。利用這個標(biāo)志信號跟時鐘進(jìn)行“與”操作,就得到一個新的時鐘。這個新的時鐘只有在數(shù)據(jù)有效時才有,在數(shù)據(jù)無效時被遮掉了。再通過Signal Event report獲知指定時間內(nèi)新的時鐘個數(shù),就可以知道有效數(shù)據(jù)的個數(shù)了。

具體操作步驟如下:

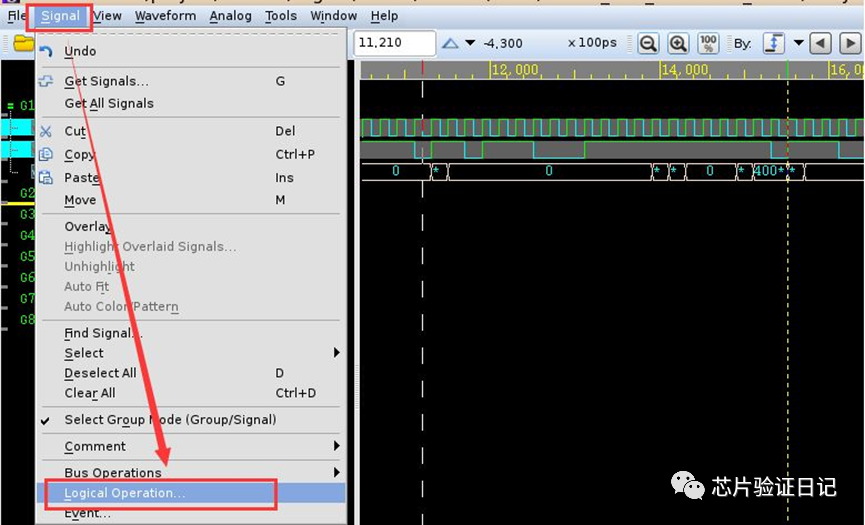

(1).鼠標(biāo)選中時鐘信號clk和數(shù)據(jù)有效標(biāo)志信號valid_in;(2).點開nWave 菜單里面的Signal,再選擇下拉菜單里的Logical Operation,如下圖:

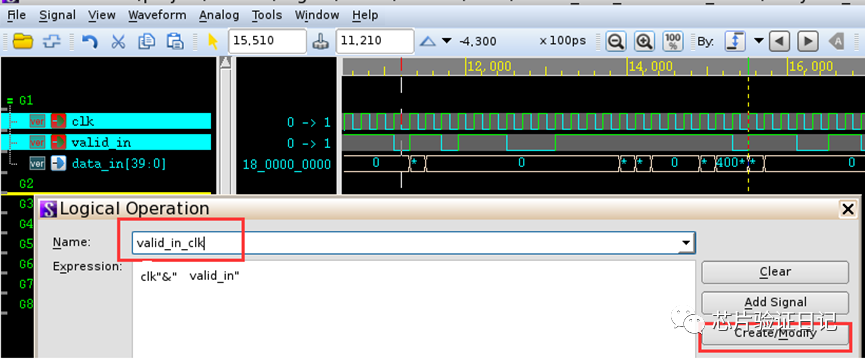

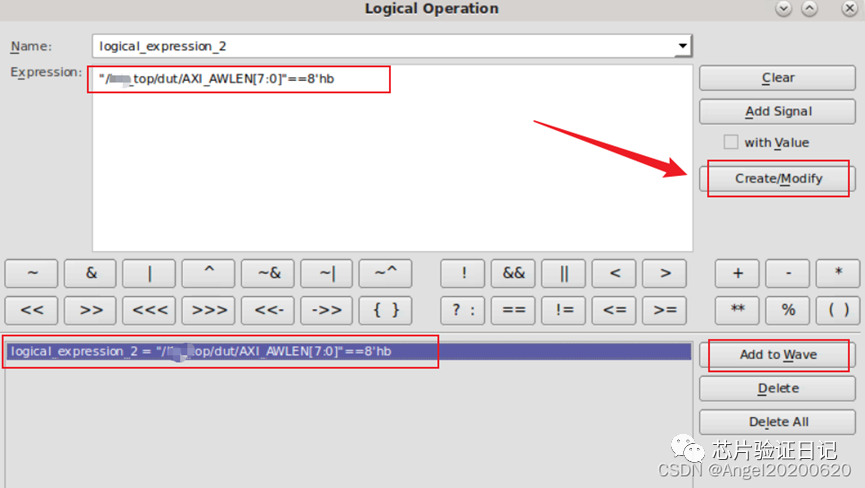

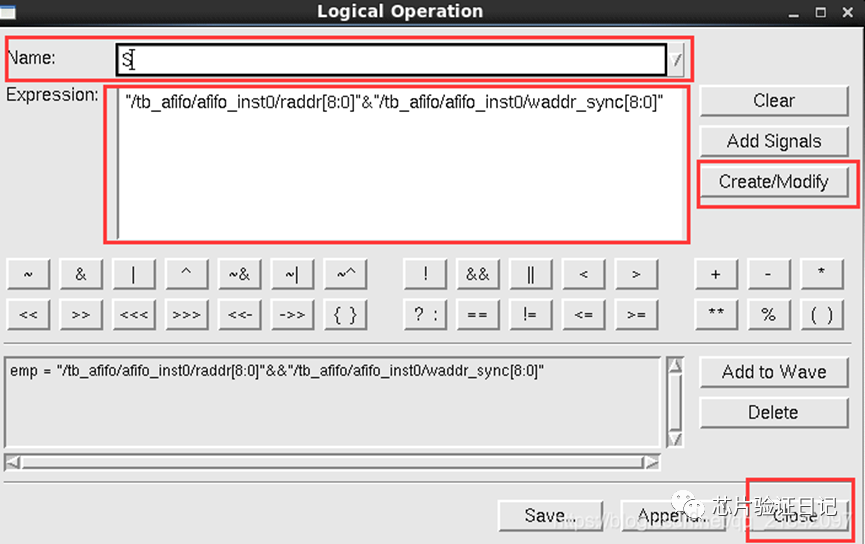

(3).在彈出的對話框里面,如下圖所示,確認(rèn)Expression里的信號操作是”&”;把Name 改成valid_in_clk;然后點擊Create/Modify按鈕;

再回來看波形,如下圖所示,就會發(fā)現(xiàn)多了一個信號valid_in_clk,這個信號就是我們需要的新時鐘信號。

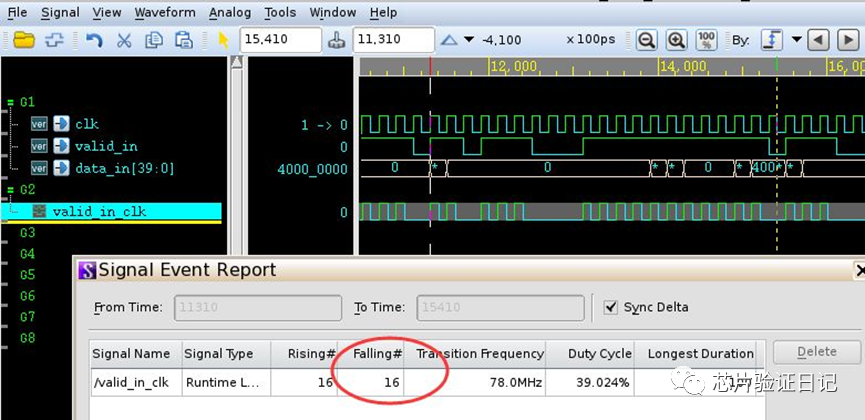

(4)接下來就是Signal Event Report閃亮登場了。選中valid_in_clk,然后在View下拉菜單里面選Signal Event Report。如下圖所示,在彈出的對話框里,找到Falling#這一列,里面列的數(shù)字16就是我們指定的時間段內(nèi)有效的數(shù)據(jù)個數(shù)了。

如果還是半信半疑的同學(xué),可以手動數(shù)一數(shù),看看Logical Operation加Signal Event Report這套組合拳的結(jié)果是否正確。

3、搜索查找

Verdi提供了很強大的搜索查找功能,充分利用好這些功能在IC設(shè)計/驗證過程中可以大大提高debug 效率。下面我們就結(jié)合實際應(yīng)用來介紹一下Verdi中常用的搜索查找功能以及一些使用技巧。

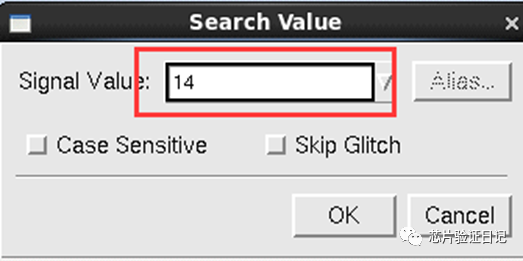

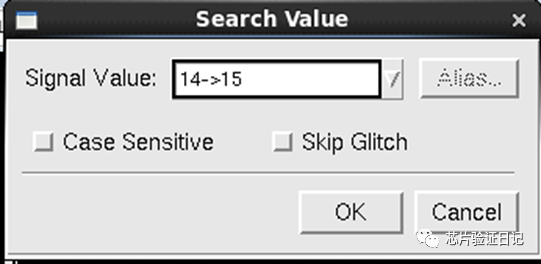

[1] 數(shù)值搜索、上升沿和下降沿搜索

進(jìn)行數(shù)值搜索、上升沿和下降沿搜索

選中信號,按n向后搜索,N向前搜索;或者按左右小箭頭進(jìn)行查找搜索。例如:

數(shù)值搜索:

上下沿搜索:

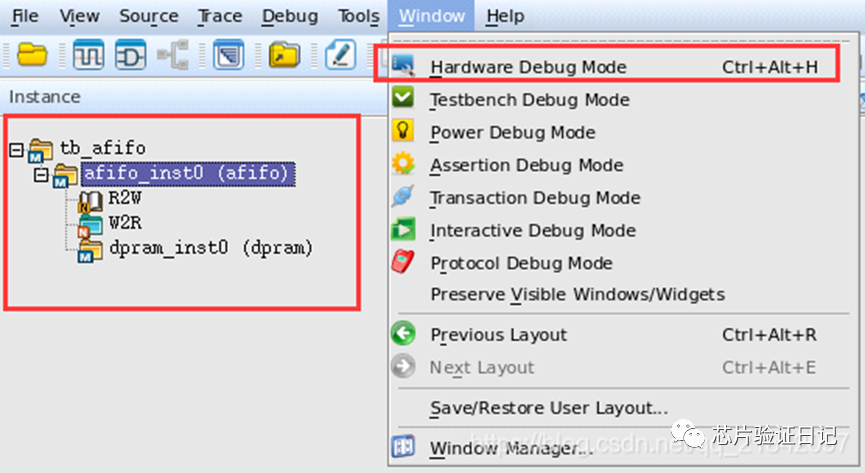

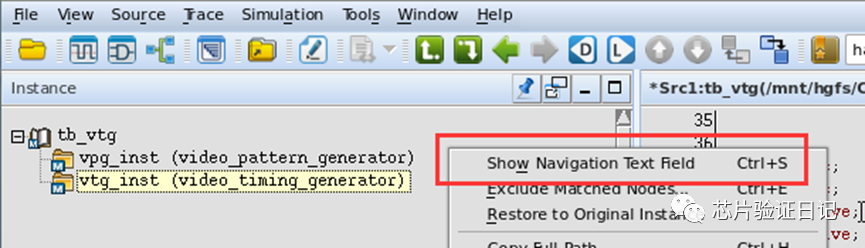

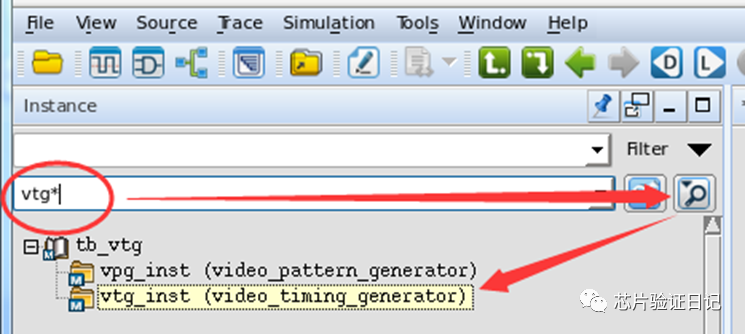

[2] 層次瀏覽器窗格中尋找實例(instance)

在利用 Verdi debug時,首先需要找到我們負(fù)責(zé)模塊的實例(instance),再選擇相應(yīng)的信號來觀察它們的行為來debug。當(dāng)設(shè)計很龐大時,要找到底層的一個小模塊,如果用鼠標(biāo)從 top一層一層的往下點,效率會比較低;又或者我們只負(fù)責(zé)了一個小模塊,對整個設(shè)計的層級關(guān)系并不清楚的時候,找到我們的底層設(shè)計會變得非常困難。

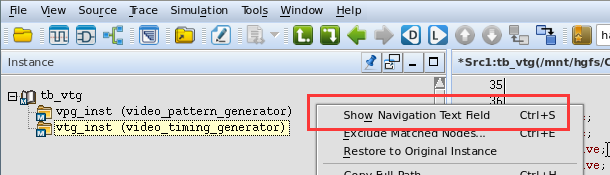

這時,只要我們知道底層模塊的實例名,就可以利用Verdi的“Show Navigation Text Field”功能快速查找了。操作方法如下圖,

a)在Verdi的層次瀏覽器窗格(Verdi界面的左部)點右鍵,彈出菜單里選“Show Navigation Text Field”或快捷鍵“Ctrl+S”

b) 在輸入對話框里輸入相應(yīng)的實例名,再點右邊的搜索按鈕就可以了。

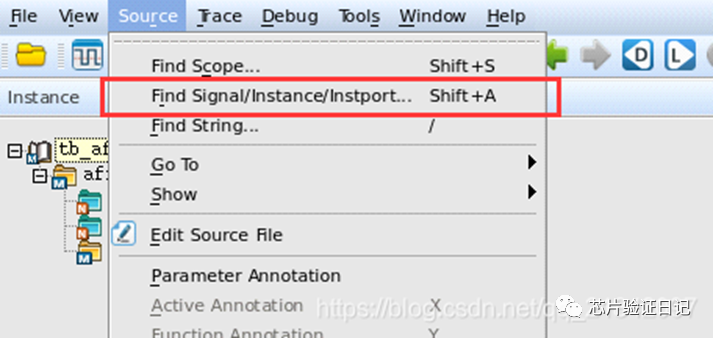

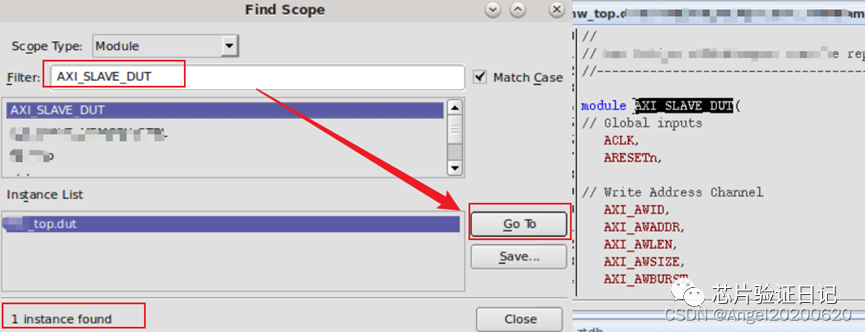

**[3] **搜索源代碼

源代碼窗格里提供了三種搜索指令,功能各不相同,用來應(yīng)付不同的使用場景。

1)Find scope

Find scope適用于整個chip里面的查找。前面提到的應(yīng)用場景如下:

A)Source –> find scope或者 按shift+S

B)在彈出對話框里Scope Type選module

Filter內(nèi)填要找module關(guān)鍵字;Instance list 里面選擇一個,點Go To,source code就會打開該module。

另外,對話框最下面列出了整個設(shè)計中找到的個數(shù),可以知道該module被instance次數(shù)。

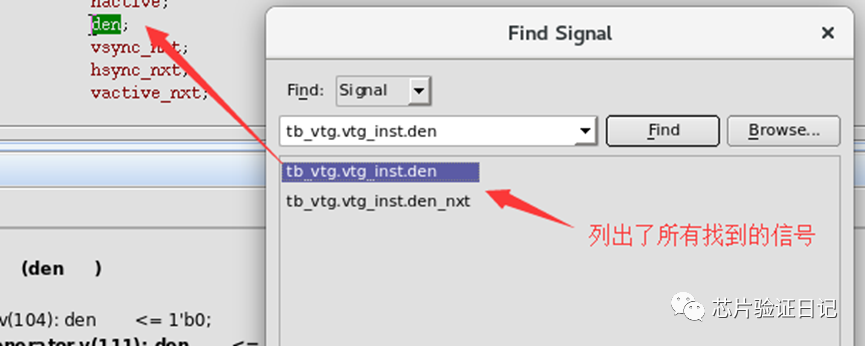

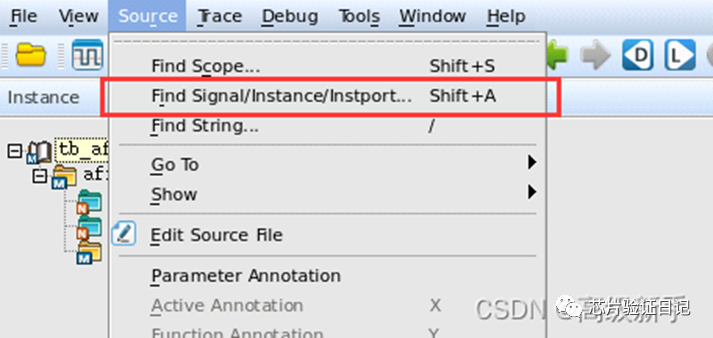

2) Find Signal/Instance/instport

這個指令可以查找指定模塊內(nèi)的信號、實例或輸入輸出端口。這個指令的好處是可以把要查找的內(nèi)容都列出來,想看哪一個就用鼠標(biāo)點一下,就會切換到源代碼窗格對應(yīng)位置。當(dāng)模塊內(nèi)要查找的signal(instance or input/output port)比較多時,可以快速的找到想看的signal。

操作方法如下:

source –> Find Signal/Instance/instport 或者shift+A

選擇要查找的類型:signal, instance or instport

輸入框里面輸入信號名,點Find按鈕,下面會列出所有找到的信號,點擊某個信號,就會到達(dá)source code 里面對應(yīng)的信號

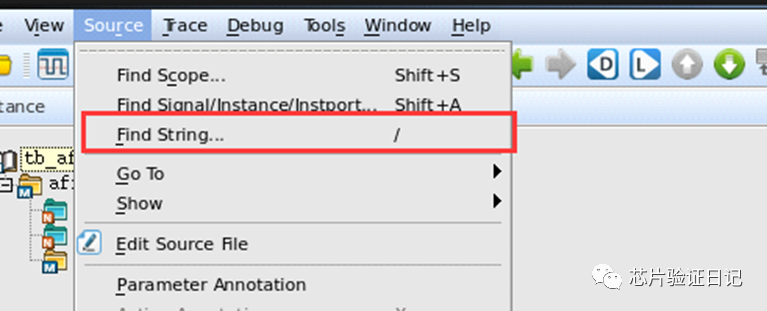

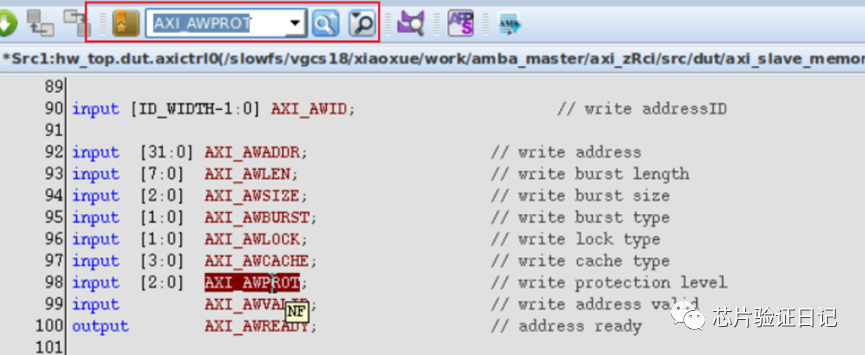

3) find string

Find string應(yīng)該是debug 過程中使用頻率最高的查找指令了。只要在輸入框里面輸入部分或全部要查找的字符串,再點一下find 按鈕就可以了。

這個指令可以在當(dāng)前文檔(current File)或者全部文檔(All file)里面查找,因為字符串查找匹配得比較多,要根據(jù)需要選擇在當(dāng)前文檔或全部文檔查找,以提高查找效率。

因為使用頻率高,Verdi也很貼心的在默認(rèn)工具欄里放置了Find string的輸入窗口,如下:

輸入欄輸入字符串有幾種方法

(1)手動輸入,好處是可以只輸入部分字符,不用全部輸入信號名(2)點擊信號,按中鍵拖入輸入欄,然后點向上或向下查找,找同名信號(3)點擊信號,按快捷鍵”Ctrl+F”,信號名就會自動輸入到輸入欄。這個快捷鍵很好用。

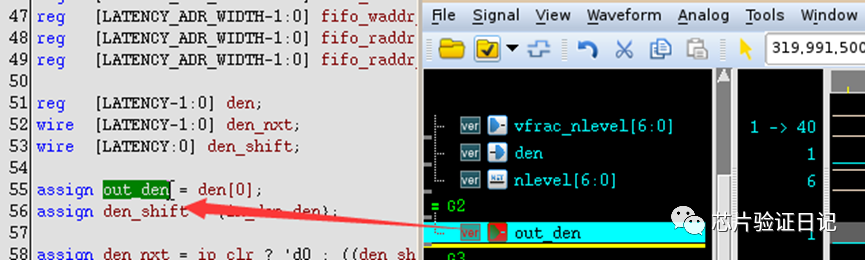

[4] nWave里面的信號追溯源代碼

Debug過程中,往nWave 里添加信號后,查看了信號波形,如果看到異常往往要回頭看一下源代碼。如果一時找不到了,find string當(dāng)然可以找得到,但是需要輸入一串字符,可能就不那么樂意了。

其實Verdi很貼心,可以直接把nwave里面的波形拖到nTrace里面,可以快速的找到要找的信號。

操作方法:nWave里面選擇信號,如out_den。按住中鍵,直接拖到source code plane,然后放開,就會顯示你要找的信號了

上述內(nèi)容介紹了Verdi常用的幾種搜索查找功能和技巧。希望對大家有幫助,debug效率更上一個檔次。如果你有什么好想法,也歡迎后臺留言一起討論。

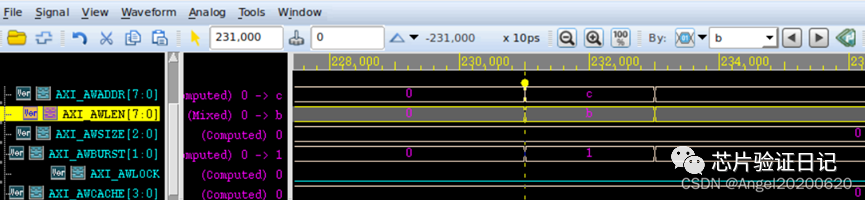

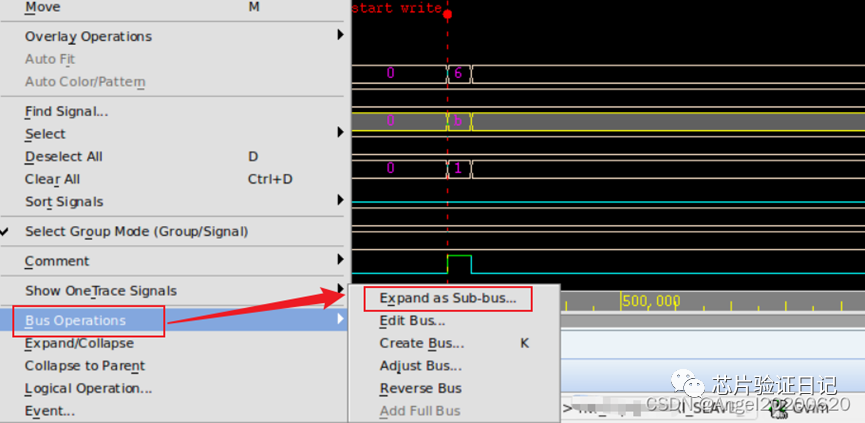

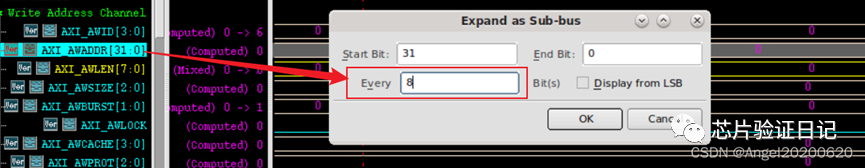

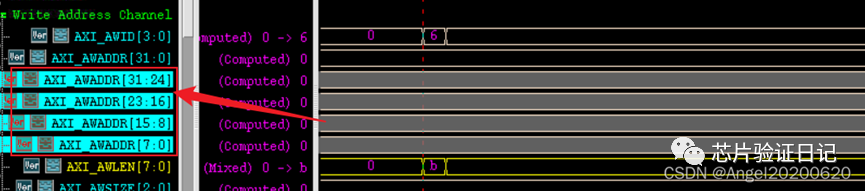

4、總線拆分

分析波形的時候有時候需要把一個多比特的bus拆分成幾個位寬較小的bus,以方便觀察數(shù)值。

右鍵/Signal -> Bus Operations -> Expand as Sub-bus

將32bit分割為4個8bit bus.

分割結(jié)果:

5、統(tǒng)計

統(tǒng)計出某個信號在特定時間段內(nèi)的跳變的次數(shù)。這個結(jié)合下一節(jié)的邏輯運算,可以把一些復(fù)雜的波形分析用直觀的形式表現(xiàn)出來。還是右鍵點擊波形窗口左邊的某個信號名字,在彈出菜單中選擇Signal Event Report。

在彈出的對話框中,可以關(guān)注感興趣的內(nèi)容,比如Rising#,指的是默認(rèn)Markers標(biāo)定的時間段內(nèi),該信號的上升沿次數(shù)。這樣就不用很辛苦的放大波形,用眼睛一個一個去數(shù)了。

6、邏輯運算

在一個頻繁變化的信號、尤其是多比特的bus信號中觀察是否出現(xiàn)了某個值,有時候可以通過搜索來追蹤。也可以通過對現(xiàn)有信號執(zhí)行的邏輯操作創(chuàng)建新信號,或者搜索信號值。但是如何一目了然地看到呢?右鍵/Signal -> Logical Operation,通過新建一個信號,該信號是待觀察信號的某種邏輯表達(dá)式。

數(shù)值搜索

邏輯操作

例如:兩信號進(jìn)行與運算,也可以進(jìn)行其他運算。

相與之后結(jié)果:

7、manage.rc

manage.rc可以管理多個rc文件,實現(xiàn)每次啟動Verdi都能載入預(yù)設(shè)的設(shè)置,同時不受上次啟動Verdi后保存的設(shè)置影響。還可以保存本次使用過程中更改過的設(shè)置,以便更新預(yù)設(shè)設(shè)置。這個略微有些復(fù)雜。在啟動Verdi時,需要加個參數(shù)。

-managercFile some_path/manage.rc

這個manage.rc的內(nèi)容大概是這樣的:

@Manage rc file Version 1.0

[File]

default_file = ~/load_only.rc

working_file = ./novas.rc

[Load]

default_file

[Save]

working_file = MODIFIED_KEY

例子中作為只讀的default_file文件,可以放一些自己習(xí)慣或者喜歡的設(shè)置。比如tab等于4還是8,各種界面的字體,以及其它一些每次啟動Verdi都希望生效的設(shè)置。working_file用來保存本次使用更改的設(shè)置,如果有想長期預(yù)設(shè)的,可以從中copy出來到default_file,這樣方便升級迭代。

通過如下常規(guī)的參數(shù)調(diào)用

-rcFile some_path/some.rc

也可以讀入一個rc文件實現(xiàn)類似預(yù)設(shè)功能,不過這種方法的缺點是這個rc文件會被當(dāng)前調(diào)用覆蓋。后果就是下次啟動的Verdi會帶有上次使用的痕跡,比如打開波形文件的目錄位置。用的次數(shù)多了,不勝其煩。干脆用manage.rc來徹底的解決。

另外,親測命令行鍵入 -managercFile 的方式也可以通過設(shè)置環(huán)境變量來替代,如在 .cshrc 中添加

setenv NOVAS_MANAGE_RC_FILE some_path/manage.rc

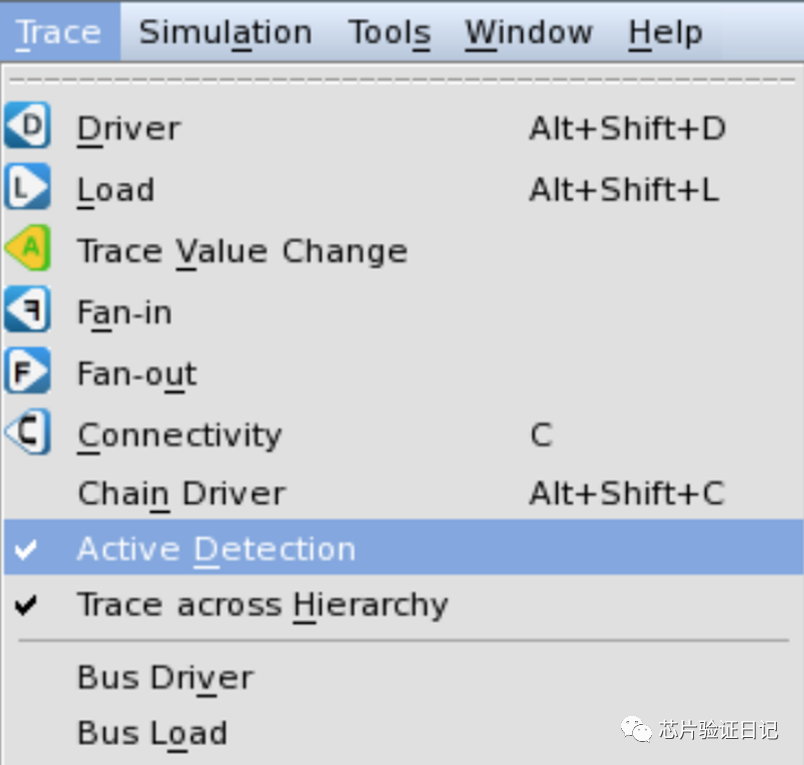

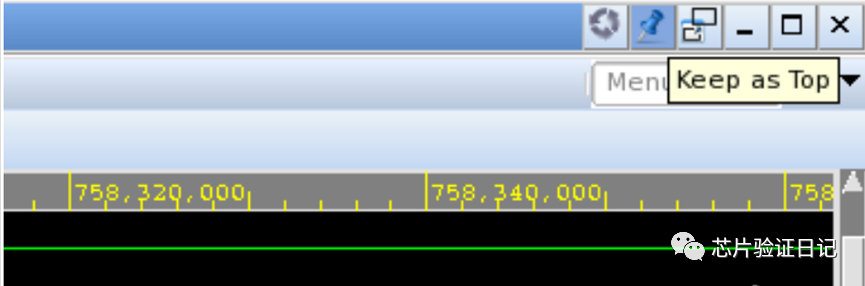

8、Trace代碼過程中波形窗口保持前置

不知道從哪個版本開始,Verdi默認(rèn)打開了Active Detection,Trace窗口在trace過程中會被激活前置,造成波形窗口被遮擋,也是不勝其煩。當(dāng)然這也屬于個人喜好問題。

那如何保持波形窗口始終在前呢?首先需要在Trace下拉菜單中取消Active Detection,然后點擊波形窗口右上角的Keep as Top。

這樣在代碼Trace時,波形始終可以看到,方便debug。Active Detection可以在rc文件中預(yù)設(shè)。Keep as Top還沒有找到預(yù)設(shè)的方法。

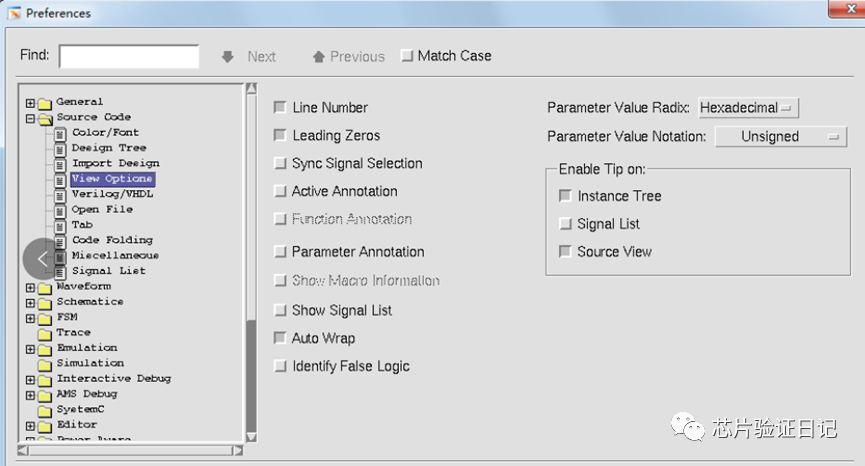

9、Parameter 提示的默認(rèn)進(jìn)制

在Verdi中,如果把鼠標(biāo)放到Verilog代碼中的parameter上,可以提示其值是多少。因為各種原因,有時候會以二進(jìn)制的形式提示,如果這個parameter是32比特,那把這個二進(jìn)制看明白也太費眼睛了。簡單的話還是16進(jìn)制比較易讀。這個可以在下圖中的Parameter Value Radix中設(shè)置。當(dāng)然也可以把它加入rc文件進(jìn)行預(yù)設(shè)。

-

VCS

+關(guān)注

關(guān)注

0文章

78瀏覽量

9590 -

Verdi

+關(guān)注

關(guān)注

0文章

22瀏覽量

8761 -

芯片驗證

+關(guān)注

關(guān)注

5文章

34瀏覽量

47200 -

DEBUG

+關(guān)注

關(guān)注

3文章

90瀏覽量

19886

發(fā)布評論請先 登錄

相關(guān)推薦

請教VCS和verdi怎么聯(lián)合使用

VCS仿真卡住,為什么無法生成verdi波形文件呢?

怎么修改verdi軟件波形背景顏色?

Verdi使用技巧 連續(xù)有效信號量測方法

如何通過自動化腳本實現(xiàn)Questasim和Verdi的聯(lián)合仿真

全網(wǎng)最實用的Verdi教程2

全網(wǎng)最實用的Verdi教程3

Verdi環(huán)境配置、生成波形的方法

Verdi連續(xù)波激光器-Coherent

全網(wǎng)最實用的Verdi教程1

全網(wǎng)最實用的Verdi教程1

評論