您的電子設計空間是否受限?需要進入一個小外殼,但仍然有很多功能?PCB技術是否值得關注成本?

是的?好。我們應該談談,所以請繼續閱讀。

故事始于擁有適合您設計的低功耗 FPGA。基于Microchip閃存的PolarFire? FPGA就是這種設備,它通常設計為在沒有任何散熱器的情況下工作,也可以在高環境溫度下工作。PolarFire還有一個較老的兄弟,Igloo2和SmartFusion2 FPGA和SoC,低功耗主題也適用。

在本文中,我不會詳細介紹FPGA本身,但會看一下封裝故事。

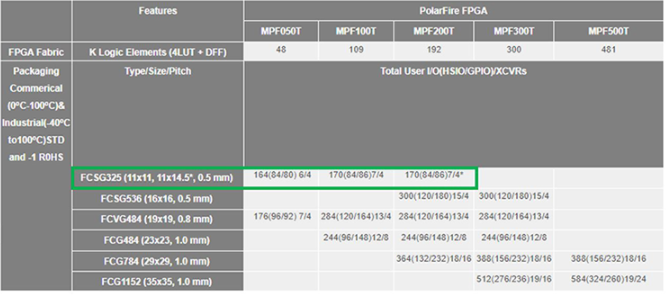

看看PolarFire的產品表,包裝故事看起來相當無害。一些讀者甚至因為0.5毫米的間距尺寸而害羞。

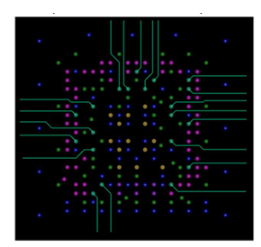

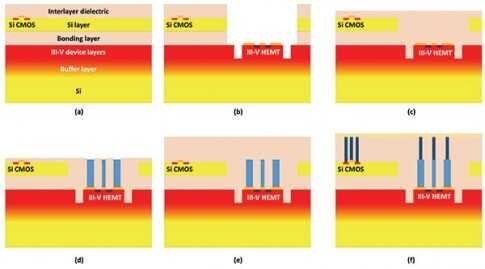

這就是美麗的開始。FCSG325封裝建立在0.5 mm間距上,是的,但是它在球柵陣列上也有幾個空白區域:

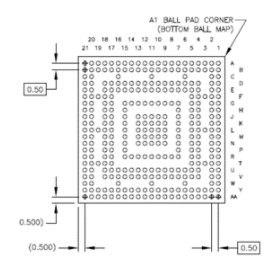

封裝的內部區域填充有用于電源和接地的引腳,外環是用戶IO和收發器引腳。這意味著,路由用戶信號僅通過包的一小部分。

放在這個包上并作為示例列出的幾個用例:

1) 所有引腳的通用布局

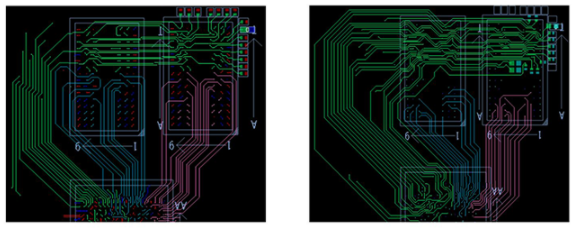

頂層用于從外環路由所有 IO,包括映像底部的收發器。這些信號根本不需要過孔。

底層從中間環接收信號。由于外圈的布線沒有過孔,因此不存在障礙物,并且可以輕松帶出信號。封裝中間顯示了用于電源的過孔,以及其獨立層的接地。

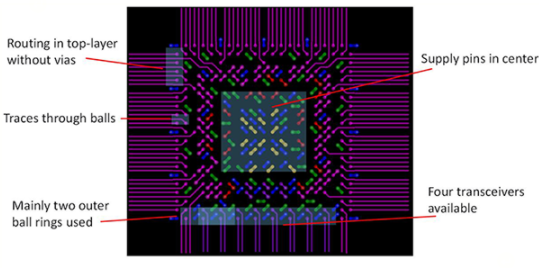

剩下幾個引腳,需要第三層,信號很少才能路由出去:

這里使用的過孔為0.1 mm,其余布局可以通過0.8 mm間距的典型規則來實現。不需要埋孔/盲孔。

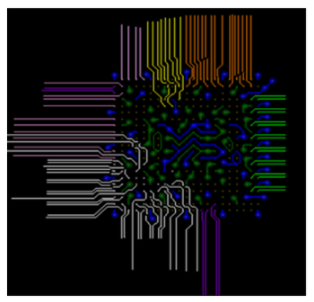

2) DDR4 帶 32 位數據路徑

FCSG325封裝具有兩個針對DDR4存儲器的預定義建議,允許在FPGA內部進行非常快速和簡單的引腳分配。這是靈活性較低的缺點還是好處?顯然是一個好處!為DDR4選擇優化的引腳排列而沒有任何擁塞是一個交互過程。使用預定義的布局將引腳變成SEP(其他人的問題),可以節省您的層數,并節省時間和白發。

DDR4 接口是根據此建議進行布局的,并且僅基于兩個信號層進行路由。這兩層包括所有 32 個數據和地址/命令行。同樣,這里不必使用埋孔/盲孔。

現在,在某些情況下,由于某些側面限制,此建議的布局可能不起作用。在您必須偏離建議布局的情況下,Microchip提供付費服務,以幫助您或通過設計服務檢查您的布局。有關此產品的詳細信息,請訪問我們的網站。

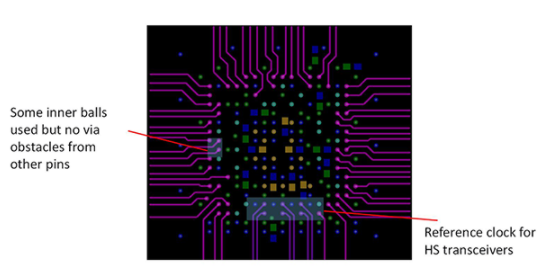

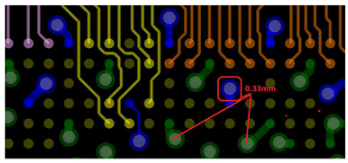

3) 成本優化布局

如果僅使用包外環中的 IO,則可以進行額外的成本優化。該圖顯示了在頂層向外路由的幾個獨立接口。這樣可以保持封裝下方的空白空間,并允許使用直徑為0.33 mm的過孔。

放大電源引腳可顯示空閑空白空間中較大的過孔。

在所有用例中,走線寬度為4 MIL / 0.1 mm,走線和焊盤之間的距離為3.1 MIL / 0.08 mm。

此包和其他包的布局建議也在此處和此處在線發布。

從本質上講,這些布局建議對您和您的設計有什么幫助?這些指針向您展示了如何結合兩個領域的優勢, 小封裝間距和經濟高效的 PCB 技術,并解決您的空間限制.

審核編輯:郭婷

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601843 -

soc

+關注

關注

38文章

4122瀏覽量

217938 -

PCB

+關注

關注

1文章

1777瀏覽量

13204

發布評論請先 登錄

相關推薦

雙無線電連接:在物聯網應用中實現兩全其美

tas5548的工作溫度在50到60度以上時有非常明顯的爆破雜音,怎么解決?

段碼式顯示屏和背光電路怎么設計?

MEMS慣性傳感器的優勢是什么?

動態Flash的可行性

nuc140 ISP下載波特率是否可以改變?

USB Type-C耳機的尷尬:三星不愛、蘋果不用

區塊鏈R3首次發布,區塊鏈應用防火墻

大朋E3-C體驗 功能全面性價比出眾

基于區塊鏈數字令牌技術的石油生產CryptoEnergy項目介紹

使用Google提供的平臺實用程序的iPhone的私密性?

兩全其美:真正的時間延遲和移相器

兩全其美:小尺寸FPGA和高性價比的PCB技術

兩全其美:小尺寸FPGA和高性價比的PCB技術

評論