晶圓生產(chǎn)的目標(biāo)

芯片的制造分為原料制作、單晶生長(zhǎng)和晶圓的制造、集成電路晶圓的生產(chǎn)和集成電路的封裝階段。本節(jié)主要講解集成電路封裝階段的部分。

集成電路晶圓生產(chǎn)是在晶圓表面上和表面內(nèi)制造出半導(dǎo)體器件的一系列生產(chǎn)過(guò)程。整個(gè)制造過(guò)程從硅單晶拋光片開始,到晶圓上包含了數(shù)以百計(jì)的集成電路戲芯片。

下面,為了更好的理解芯片的結(jié)構(gòu),小編將為大家介紹一些基本的晶圓術(shù)語(yǔ)。

晶圓術(shù)語(yǔ)

- 芯片、器件、電路、微芯片或條碼:所有這些名詞指的是在晶圓表面占大部分面積的微芯片圖形。

- 劃片線或街區(qū):這些區(qū)域是在晶圓上用來(lái)分隔不同芯片之間的間隔區(qū)。劃片線通常是空白的,但有些公司在間隔區(qū)內(nèi)放置對(duì)準(zhǔn)標(biāo)記,或測(cè)試的結(jié)構(gòu)。

- 工程試驗(yàn)芯片和測(cè)試芯片:這些芯片與正式器件芯片或電路芯片不同。它包含特殊的器件和電路模塊用于對(duì)晶圓生產(chǎn)工藝的電性測(cè)試。

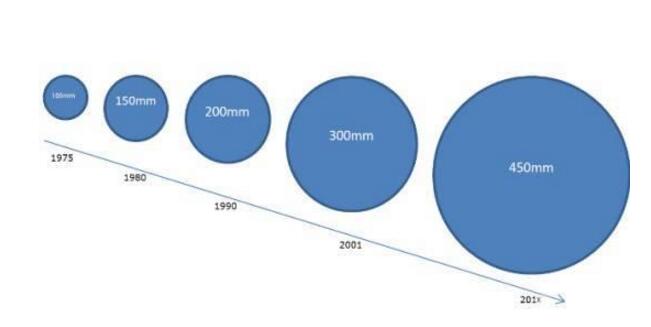

- 邊緣芯片:在晶圓的邊緣上的一些掩模殘缺不全的芯片而產(chǎn)生的面積損耗。由于單個(gè)芯片尺寸增大而造成的更多邊緣浪費(fèi)會(huì)由采用更大直徑晶圓所彌補(bǔ)。推動(dòng)半導(dǎo)體工業(yè)向更大直徑晶圓發(fā)展的動(dòng)力之一就是為了減少邊緣芯片所占的面積。

- 晶圓的晶面:圖中的剖面標(biāo)示了器件下面的晶格構(gòu)造。此圖中顯示的器件邊緣與晶格構(gòu)造的方向是確定的。

- 晶圓定位邊/凹槽:例如圖示的晶圓有主定位邊和副定位邊。300mm和450mm直徑的晶圓都是用凹槽作為晶格導(dǎo)向的標(biāo)識(shí)。這些定位邊和凹槽在一些晶圓生產(chǎn)工藝中還輔助晶圓的套準(zhǔn)。

芯片術(shù)語(yǔ)

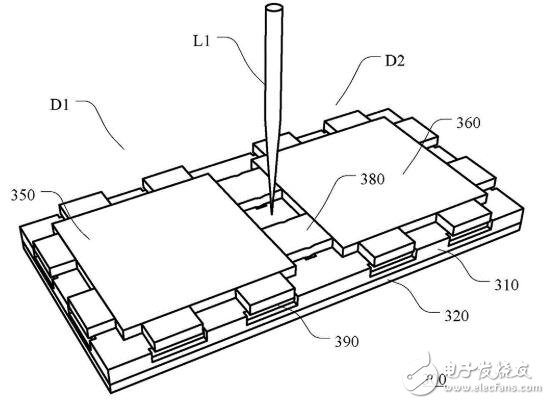

下圖是一個(gè)中規(guī)模(MSI)/雙極型集成電路的顯微照片。之所以選擇這個(gè)集成等級(jí),是為了照片上能顯示出電路的具體圖形。對(duì)于更高集成度的電路,它的元件非常小,以至于在整個(gè)芯片的顯微照片上無(wú)法辨認(rèn)。

圖中芯片的特性有:

- 雙極型晶體管

- 電路的特定編號(hào)

- 為連接芯片與管殼而備的壓焊點(diǎn)

- 壓焊點(diǎn)上的一小塊污染物

- 金屬表面導(dǎo)線

- 劃片線(芯片間的分割線)

- 獨(dú)立未連接的元件

- 掩模版對(duì)準(zhǔn)標(biāo)記

- 電阻

晶圓生產(chǎn)的基礎(chǔ)工藝

在很多混合和集成電路設(shè)計(jì)。集成電路是基于一個(gè)少數(shù)晶體管結(jié)構(gòu)和制造工藝。類似于車工業(yè),這個(gè)工業(yè)生產(chǎn)的產(chǎn)品范圍很廣,從轎車到推土機(jī)。然而,金屬成型、焊接、油漆等工藝對(duì)汽車廠都是通用的。在汽車廠內(nèi)部,這些基本的工藝以不同的方式被應(yīng)用,以制造出客戶希望的產(chǎn)品。

同樣,芯片制造也是同樣的。依此進(jìn)行4個(gè)基本操作,以產(chǎn)生特定的芯片。這些操作是薄膜、圖形化、摻雜和熱處理。下圖是一個(gè)硅柵晶體管的橫截面。它說(shuō)明了如何使用這些基本的操作并依此制造一個(gè)實(shí)際的半導(dǎo)體器件。

薄膜工藝

薄膜工藝是在晶圓表面形成薄膜的加工工藝。

各種技術(shù)用于二氧化硅層生長(zhǎng)和各種材料的沉積。

通用的淀積技術(shù)是物理氣相淀積、化學(xué)氣相淀積、蒸發(fā)和濺射、分子束、外延生長(zhǎng)、分子束外延和原子層淀積。使用電鍍?cè)诟呙芏燃呻娐飞系矸e金屬化層。

圖形化工藝

圖形化工藝是通過(guò)一系列生產(chǎn)步驟將晶圓表面薄膜的特定部分除去工藝。從此之后,晶圓表面會(huì)留下帶有微圖形結(jié)構(gòu)的薄膜。被除去部分的可能形狀是薄膜內(nèi)的空或是殘留的島狀部分。

圖形化工藝也被未大家熟知的廣掩模、掩模、光刻或微光刻。在晶圓制造過(guò)程中,晶體三極管、二極管、電容器和金屬層的各種物理部件在晶圓表面或表層內(nèi)構(gòu)成。

這些部件是每次在一個(gè)掩模版上生成的,并且結(jié)合生成薄膜及去除特定部分,通過(guò)圖形化工藝過(guò)程,最終在晶圓上保留特征圖形的部分。光刻生產(chǎn)的目標(biāo)是根據(jù)電路設(shè)計(jì)的要求,生成尺寸精確的特征圖形,且在晶圓表面的位置要正確,而且與其他層的關(guān)聯(lián)也要正確。

圖形化工藝是所有四個(gè)基本工藝中最關(guān)鍵的。圖形化工藝確定了器件的關(guān)鍵尺寸。圖形化工藝過(guò)程中的錯(cuò)誤可能造成圖形歪曲或套準(zhǔn)不好,最終可轉(zhuǎn)化為對(duì)器件的電特性產(chǎn)生影響。

圖形的錯(cuò)位也會(huì)導(dǎo)致類似的不良結(jié)果。圖形化工藝中的另一個(gè)問(wèn)題是缺陷。圖形化工藝是高科技版本的照相術(shù),只不過(guò)是在難以置信的微小尺寸小完成的。在制程中的污染物會(huì)造成缺陷。事實(shí)上由于圖形化工藝在現(xiàn)代晶圓生產(chǎn)過(guò)程中要完成30層或更多,所以污染問(wèn)題將會(huì)放大。

-

芯片

+關(guān)注

關(guān)注

453文章

50407瀏覽量

421848 -

集成電路

+關(guān)注

關(guān)注

5381文章

11385瀏覽量

360876 -

晶圓

+關(guān)注

關(guān)注

52文章

4842瀏覽量

127803

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

晶圓的基本原料是什么?

什么是晶圓測(cè)試?怎樣進(jìn)行晶圓測(cè)試?

史上最全晶圓專業(yè)術(shù)語(yǔ)

晶圓處理工程常用術(shù)語(yǔ)

硅晶圓是什么?硅晶圓和晶圓有區(qū)別嗎?

晶圓針測(cè)制程介紹

為晶圓級(jí)CSP生產(chǎn)設(shè)定掩模標(biāo)準(zhǔn)

晶圓制造相關(guān)術(shù)語(yǔ)及工藝介紹

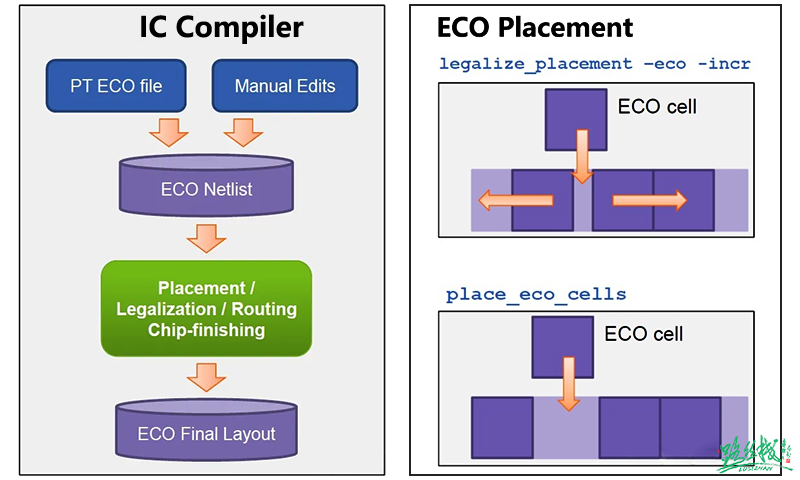

晶圓術(shù)語(yǔ) 芯片ECO流程

晶圓表面特性和質(zhì)量測(cè)量的幾個(gè)重要特性

晶圓生產(chǎn)的目標(biāo)及術(shù)語(yǔ)介紹

晶圓生產(chǎn)的目標(biāo)及術(shù)語(yǔ)介紹

評(píng)論