隨著科技的發(fā)展,我們傳輸?shù)臄?shù)據(jù)變大,傳輸?shù)木嚯x變長,對頻率穩(wěn)定度的要求變高。[差分輸出(例如PECL, LVDS, HCSL) ]可以滿足高速數(shù)據(jù)傳輸。

信號完整性(SI)

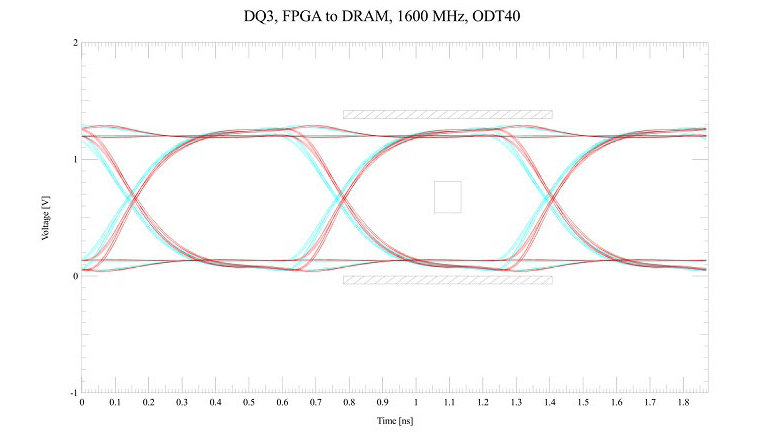

信號完整性包括由于互連結(jié)構(gòu)、電源系統(tǒng)、電子器件等引起的所有 信號質(zhì)量及延時等問題 。高比特率和更長的傳輸距離會讓信號受到噪聲,失真,損耗等影響。

信號波形畸變導(dǎo)致電路無法正確的接收信號,從而導(dǎo)致電路不正常工作。在接收信號中,可能錯誤判斷發(fā)送器輸出的“0”、“1“。

晶振的抖動和相噪

晶振作為核心的電子器件。選擇KOAN低相噪晶振,即KJ系列可以滿足在精密電子儀器,無線電定位,高速目標(biāo)跟蹤和宇航通信等領(lǐng)域的需求。更多內(nèi)容:《[晶振參數(shù):相位噪聲&抖動]》

抖動是信號偏離理想位置的程度,表示的是時域特征。從頻域來看,對應(yīng)的參數(shù)是相位噪聲。時間和頻域之間的關(guān)系互為倒數(shù)Time=1/Frequency.

相位噪聲的形成因素主要三方面:

- A區(qū)主要是晶體Q值來決定;

- B區(qū)主要是晶體外圍電路(包括IC)來決定;

- C區(qū)主要是信號輸出(白噪聲)來決定.

電源完整性(PI)

除了選擇低抖動的元器件以外,穩(wěn)定的電源輸出也是一個重要因素。電源完整性是電源波形的質(zhì)量。

在充放電過程中,電池的電壓也會發(fā)生變化。電源噪聲控制在合理的范圍內(nèi),為芯片提供穩(wěn)定的電壓,實時響應(yīng)負載對電流的快速變化,并能夠為其他信號提供低阻抗的回流路徑。

以[KOAN溫補晶振]為例,電壓變化會產(chǎn)生±0.3ppm的頻率變化。

電路設(shè)計中,PMIC電源管理芯片可以根據(jù)需要提高、降低或者調(diào)節(jié)電壓,然后把調(diào)整后的電壓提供給系統(tǒng)子組件使用。

-

電子器件

+關(guān)注

關(guān)注

2文章

583瀏覽量

32060 -

信號完整性

+關(guān)注

關(guān)注

68文章

1397瀏覽量

95385 -

電源系統(tǒng)

+關(guān)注

關(guān)注

3文章

612瀏覽量

37754

發(fā)布評論請先 登錄

相關(guān)推薦

基于信號完整性分析的高速數(shù)字PCB的設(shè)計方法

高速電路設(shè)計中信號完整性分析

高速電路信號完整性設(shè)計培訓(xùn)

基于信號完整性分析的高速數(shù)字PCB板的設(shè)計開發(fā)

高速電路設(shè)計中信號完整性面臨的挑戰(zhàn)有哪些?怎么處理?

什么是電源和信號完整性?

高速電路信號完整性分析與設(shè)計二

高速電路設(shè)計之信號完整性及低抖動元器件

高速電路設(shè)計之信號完整性及低抖動元器件

評論