討論μP監控器復位電路在基于微處理器的系統中的價值。解釋與監控電路相關的術語以及如何實現這些術語。討論的主題包括上電復位(POR)、掉電條件和低功耗故障。討論的特性包括欠壓/過壓檢測、手動復位輸入、電源故障比較器和看門狗定時器。

還探討了具有芯片使能門控功能的電池備份電路。此外,本文檔還討論了多電壓系統等未來需求。

世界給微處理器系統設計人員帶來了各種各樣的問題。電源以錯誤的順序啟動,上升速度太慢,穩定速度太慢。電源電壓會因外部元件負載而上下毛刺,或者隨著總線電壓波動或系統電池開始失效而漂移進出容差。外圍組件和主板無法通電,也無法與處理器的需求同步通信。盡管進行了冗長的引入前軟件分析,但錯誤還是潛入系統代碼并被運送到現場。

系統設計人員盡其所能在固定成本預算內最大限度地減少這些事件,但細心的工程師希望他們的系統即使在出現問題時也能安全運行。他們希望確保基于微處理器的系統每次都能正常啟動;它檢測到系統錯誤何時發生或即將發生;它最大限度地減少了這些錯誤的影響;并且它從錯誤中安全返回,很少或沒有用戶干預。

現代微處理器-監控電路是監控和維護此類系統活動的低成本和有效方法。應用過去幾年開發的技術,今天的主管提供微處理器系統所需的保險。它們具有低功耗、低成本和廣泛的集成功能,采用非常小的封裝。

上電復位

微處理器系統的第一個也是最常用的保護措施是上電復位(POR)功能。幾乎每臺計算機和嵌入式處理器都包含一種在首次通電時以正確配置冷啟動系統的方法。大多數處理器數據手冊都提供了最短復位周期,在此期間,器件應保持不工作狀態,直到本地電源穩定指定的時間間隔(典型值為 200ms)。如果處理器太快退出復位,則不能保證正常運行。在此復位間隔期間,允許處理器的時鐘穩定,內部寄存器有時間正確加載。大多數處理器數據手冊都規定了最短復位時間,但它們幾乎沒有提供實現此延遲的指南。

一種價格低廉但有風險的常用方法是在微處理器的復位輸入引腳上使用電阻電容(RC)低通濾波器延遲復位信號(圖1)。您可以選擇組件值,以根據緩慢的指數RC上升時間提供廣泛的復位延遲。當電容器從地充電至 V 時抄送,電壓超過微處理器識別為有效(高)輸入電壓(VIH).此操作使處理器脫離重置,并且它應該(理想情況下)開始正常運行。不幸的是,這種方法有幾個缺點。

圖1.電阻-電容復位延遲電路

第一個上電問題出現在電源電壓相對于處理器的復位時間段緩慢上升時。電容電壓緊隨V抄送用于低壓擺率。因此,處理器的復位輸入電壓可以達到有效的VIHV之前的級別抄送到達為設備指定的容差范圍內。例如,對于容差為±3%的3.10V電源,復位在V之前不應取消置位抄送> 2.97V.但是,該系統可以達到最小VIH2.31V 電平(大多數處理器為 0.7Vcc),早在電源準備好用于處理器運行之前。也就是說,當電源仍比其標稱工作電平低 20% 或更多時,處理器可以從復位中釋放。

RC電路的第二個缺點是大多數處理器需要較長的復位延遲間隔(典型值為200ms),這迫使處理器復位輸入端的壓擺率較低。復位邏輯輸入通常設計用于識別從V快速轉換的數字信號伊利諾伊州到 VIH.濾波至慢μV/μs壓擺率的延遲復位電壓不會為處理器的數字輸入提供足夠的過驅,這種情況會導致復位亞穩態。RC濾波器和處理器輸入之間的施密特觸發器可以提高表觀壓擺率,但它本身也會引起上電問題(除了額外的成本和元件面積)。

掉電和毛刺檢測

掉電檢測是第二常見的復位要求,與POR密切相關,突出了低成本RC延遲電路的第三個問題。假設RC延遲為處理器在釋放復位之前正確初始化提供了一個合理的間隔,那么如果電源電壓在任何重要的時間間隔內毛刺或下降低于其工作容差,系統將面臨風險。

由于選擇RC電路是為了在復位信號上產生較長的上升時間延遲,因此它會在濾波后的復位信號降至V之前濾除相對較快的欠壓毛刺伊利諾伊州.快速的負毛刺(相對于復位延遲時間)會對處理器的內部寄存器造成嚴重破壞,迫使其執行錯誤的指令、處理不正確的數據或發出危險的系統信號。一個可以長期維持的供應下降,可以帶來 V抄送低于處理器的工作容差,同時保持復位電壓高于其復位開關閾值。

改進但仍然有風險的解決方案在RC電路中增加了一個二極管,從而為大的負向V創建快速濾波器響應抄送信號(圖2)。作為 V抄送降至充電電容電壓以下時,二極管導通并向下拉復位信號。這種方法對于 V 的硬降是令人滿意的抄送,但較小的壓降(掉電)可能無法打開二極管。例如,對于2.5V處理器,在二極管開始對電容電壓放電之前,電源必須下降20%以上。如果毛刺或壓降大于處理器容差,但小于二極管的正向導通電壓,則即使電源恢復到其全部V,處理器的內部寄存器也可能損壞。抄送不觸發處理器重置的規范。

圖2.改進的RC延遲電路。

集成復位發生器

與RC延遲電路相關的問題可通過IC復位發生器(如SOT23 MAX6332×MAX6334和SC70 MAX809/MAX810/MAX803)輕松解決。通過將精確的電壓監視器與精確的定時電路集成在一起,這些現代復位發生器可檢測電源電壓何時在處理器的容差范圍內,并提供有保證的復位延遲。

典型的復位器件(圖3)包含一個基準電壓源、一個電壓比較器、一個電源電壓分壓器網絡、一個固定延遲時間電路和一個輸出驅動器級。電阻網絡可在工廠針對寬范圍的電源電壓容差進行調整,允許用戶為每個處理器應用選擇特定的復位閾值。復位發生器的精確電壓檢測器與其邏輯輸出級無關,不依賴于處理器的高電平和低邏輯輸入電平來確定電源何時在其允許的工作容差范圍內。

圖3.集成復位電路。

對于POR,內部電壓比較器僅在電源電壓超過所選閾值足夠長時間時打開延遲電路。延遲發生器提供處理器兼容的復位時間范圍為 1ms 至 1s,使輸出級保持復位狀態,直到最小指定周期到期。然后,發生器輸出(提供多個邏輯選項)被取消置位,以快速驅動處理器從復位狀態并進入正常工作狀態。

大多數復位發生器中的電壓比較器還可以檢測電源電壓何時降至處理器容差以下。如果它下降到所選閾值以下足夠長的時間,復位輸出會快速置位其活動驅動器邏輯,以掛起并重新初始化所有處理器活動。復位可以隨時激活:電源的鋸齒狀啟動,大V抄送系統出現故障、掉電或關機。

重置閾值

寬范圍 V抄送復位閾值在當今的行業中可用。許多供應商為標稱電源電壓 5、3.3、2.5、1.8 和 1.2V 提供標準復位選項。客戶可以選擇一個標準的固定復位門限,以匹配給定的標稱處理器電源電壓及其最小容差。或者選擇可調復位門限,以監視低至0.5V的更寬電壓范圍(MAX16052/MAX16053)。復位容差通常在-5%和-10%的處理器兼容選項中提供。對于非標準固定復位電壓,一些供應商在寬V電壓上提供100mV擊穿抄送范圍為 1.2V 至 5V。這種靈活的范圍允許用戶針對元件容差和電源電壓的特定組合優化閾值。

更嚴格的復位門限精度通常有助于支持更寬松、成本更低的電源規格。例如,保證其5V±10%處理器工作的系統需要在電源降至4.5V之前初始化復位。如果監控設備的精度為 ±2.5%,則在整個溫度范圍內相對于標稱 V 保證抄送,典型復位門限為4.625V,最大復位門限為4.75V。由于監控器的精度規格為 ±2.5%,處理器可以重置為任何 V抄送低于4.75V,保證在V之前復位抄送降至4.5V以下。

為了支持監控器精度開銷并避免出現未知復位條件的區域,應將最終電源指定為更嚴格的最小限值 (4.75V)。由此產生的 5V、-5%/+10% V抄送規格可能會大大增加電源成本。因此,更精確的±1%或±1.5%的監控器雖然比±2.5%的設備更昂貴,但實際上可以降低系統成本。

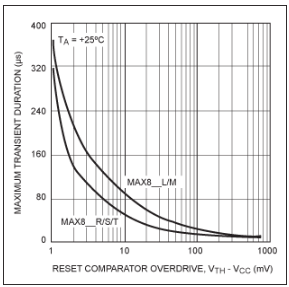

現代復位發生器的一個重要功能是最大限度地減少令人討厭的復位:當短時間的小幅度尖峰將電源電壓壓低到其允許的最小水平以下時,就會發生不希望的系統重新啟動。為了確定是否需要系統復位,電壓檢測器集成了毛刺持續時間和強度。最大電源瞬態持續時間與過驅的關系圖可以說明復位發生器如何響應系統電源中的噪聲(圖 4)。

圖4.最大瞬態持續時間與過載。

欠壓/過壓檢測電路

必須監視某些電源的欠壓和過壓情況。在許多系統中,過壓監控已成為必要的,以防止損壞昂貴的處理器和ASIC。監控過壓和欠壓條件的窗口檢測器可以用兩個電壓檢測器和一個基準電壓源構成。或者,也可以使用專用的窗口檢測器IC,例如MAX6754系列(圖5)。

圖5.窗戶檢測電路。

手動復位

用于手動(按鈕)復位的輸入是簡單復位生成器的有用補充。手動復位允許用戶或外部系統組件在電源電壓保持在容差范圍內時觸發微處理器復位。如果處理器由于某種未知原因鎖定,手動重置可讓您在不關閉系統電源的情況下重新啟動。此功能對于從不關閉控制處理器電源的產品尤其重要,即使在“關閉”模式下也是如此。它對于調試和最終系統測試也很有用。在所有情況下,手動復位都可以保證處理器在復位期間收到必要的超時期限。

手動復位通常由低成本按鈕開關啟動,MAX6335–MAX6337系列等復位器件通常包括輸入去抖動電路,以屏蔽接地開關觸點閉合引發的振鈴效應。由于開關可以遠離處理器(通常位于背板上或隱藏在電池或電源倉中),因此最好的手動復位電路通過抑制短(典型值為100ns)噪聲引起的脈沖來適應長電路板運行。為了保證有效的復位輸入(典型值為1μs),它們還需要一個最小輸入脈沖寬度。手動復位可以作為監控器的獨立輸入實現,也可以作為雙功能引腳實現,既用作復位輸出,又用作手動復位輸入。

一些微處理器現在將上電復位電路與其電源管理功能集成在一起。雖然這些嵌入式復位電路通常優于RC延遲方法,但μP IC工藝針對高速或低功耗數字性能進行了優化,而不是精確可靠的模擬測量和定時。因此,內部復位可以在正常工作條件下提供合理的上電時序,但它們很難處理可能導致處理器錯誤的電源瞬變和掉電。為了實現穩健運行,大多數處理器提供額外的復位輸入,可由外部專用復位監控器驅動。

電源故障和低電量指示燈

許多系統即使電源完全斷電且微處理器發生故障,也無法承受數據丟失。電源電壓損失導致的硬復位會導致處理器轉儲其內部寄存器中保存的任何信息。系統可以通過將數據連續保存在非易失性存儲器中來最大程度地減少這種潛在的數據丟失,但這種方法會降低處理器效率,并強調閃存或EEPROM存儲器的寫入耐久性。

由SOT23封裝的MAX6342–MAX6345監控器實現的一種改進方法采用電源故障或電池電量不足指示器,使處理器能夠預測電源電壓損失。通過預先警告,處理器可以在系統啟動復位之前將信息存儲在非易失性存儲器中(圖 6)。

圖6.電源故障/電池電量不足指示燈。

典型系統通過調節來自主電源或電池的電壓為處理器供電。該處理器電源電壓由標準上電/掉電復位監控,但獨立的低壓指示器也監視主電源。該指示器的閾值設置為高于穩壓壓差,其輸出驅動不可屏蔽中斷(NMI)。此 NMI 指示處理器開始將數據保存到非易失性存儲器中。如果實施得當,低壓指示器將提供足夠的時間在穩壓電壓降至處理器的最低工作規格以下之前存儲所有數據。

備用電池和芯片使能門控

當系統沒有時間將大量數據傳輸到非易失性存儲器時,備用電池是一個有吸引力的替代方案。為了適應雙電源供電,SOT23 MAX6361/MAX6363/MAX6364等器件為初級V提供一條輸入抄送一個用于板載電池(圖 7)。

圖7.備用電池。

當電源電平足以維持易失性RAM活動時,內部開關將監控器的電壓輸出連接到V抄送.當 V抄送低于指定閾值時,管理引擎通過向微處理器發出復位來禁用進一步的內存寫入。如果 V抄送下降太低以保持 RAM 內容,管理引擎從 V 切換 RAM 電源抄送到備用電池。具有低掛起電流的存儲設備可以長時間保存數據,直到系統V抄送可以恢復到適當的操作水平。如果需要,相同的備用電池過程也可以維持實時時鐘和某些處理器活動。

看門狗定時器

即使是設計最好的系統也會受到電源波動以外的誤差的影響。錯誤的程序代碼、不正確的時鐘信號或響應不良的外設都可能迫使處理器退出其正常運行代碼或進入死胡同循環。當處理器離開預期的指令路徑時,它可能無法知道它是否運行不正確并需要重新啟動。

為了解決這個問題,許多監控IC(如工業標準的MAX823和更新的MAX6316–MAX6318器件)都包含一個看門狗定時器,作為確保處理器在適當的代碼邊界內執行的低成本手段。此方案要求處理器在指定的最短時間段內不斷更新看門狗邏輯輸入。否則,管理引擎會發出系統警報(圖8)。

圖8.看門狗定時器選項。

看門狗常見的行業標準超時時間為 1.6 秒,但供應商提供從 1 毫秒到 1 分鐘的選項。由于監視器更新會消耗處理器周期開銷,因此應通過詢問“在啟動重置之前允許系統錯誤運行多長時間?某些設備允許更長的啟動超時(例如 1 分鐘),然后再回落到正常的 1.6 秒短超時操作模式。這種雙超時功能允許系統在啟動期間執行冗長的啟動過程,然后負責更快的常規看門狗更新。

看門狗輸出有時可以綁定到不可屏蔽的處理器輸入,這允許管理引擎嘗試使處理器恢復正常運行,而不會丟失易失性內存數據。為了在檢測到任何錯誤時完全重新初始化系統,看門狗可以與 POR/掉電檢測輸出共同綁定。

許多微處理器現在都提供內部看門狗定時器來監控自己的內部狀態。由于看門狗只是處理器的支持功能,因此它通常提供一系列可編程超時周期和禁用選項。處理器還可以通過軟件控制修改其看門狗監視器功能。然而,由于可編程看門狗采用與處理器相同的電源電壓和時鐘輸入工作,因此它經常受到與處理器本身相同的瞬態誤差的影響。因此,最強大的系統包括一個獨立的看門狗,它保證每次都向處理器正確輸入。

多電源應用

較新的處理器和許多其他系統需要多電源電壓。多電源器件的趨勢在高速小尺寸數字信號處理器中尤為明顯,它可以與3.3V的標準系統I/O電壓通信,但內核邏輯為2.5V或更低。這些器件通常要求在釋放 POR 之前,兩個電源都在處理器的容差范圍內。同樣,復雜的接收器系統可以保持四個或五個電源電壓(例如12V、5V、-5V、3.3V和2.5V),支持各種模擬和數字組件。任何這些電壓的欠壓情況都可能導致系統故障。

盡管成本低廉,但簡單的RC網絡無法同時監視多個電源,同時為系統復位提供單個有效邏輯電平。從歷史上看,制造商已經創建了具有多個電源故障/復位檢測器的多電源監控電路,或者通過連接多個單電源復位器件的輸出來共同創建。然后,任何低于其指定容差的電源電壓都會阻止處理器復位的釋放。

一些較新的監控器支持單封裝設計中的多電壓監控(圖 9)。MAX6351–MAX6360系列設計用于雙電源和三電源應用,為工廠調整的標準復位門限(例如,與3.3V和2.5V電源電壓相關的復位門限)提供了多種選擇。可調檢測器允許用戶監視第三個電源電壓(如 5V 模擬外設)并推遲處理器啟動,直到所有電壓都在容差范圍內。現代封裝和工藝允許Maxim將額外的功能壓縮到多電壓SOT23復位監控器中,以及延長啟動周期的看門狗定時器和手動復位輸入。

圖9.多電源復位監控。

未來

隨著處理器要求從穩步縮小的集成過程中獲得更高的性能,我們應該看到更低的工作電壓。如果±5%和±10%的當前處理器電源容差保持不變,設計人員將需要更精確的模擬電壓檢測器來取代其分立元件替代品。成功監測-5mV最大電源偏差的舊250V復位架構可能無法支持具有-1mV欠壓限值的新2.60V監視器。由于許多低壓系統需要支持一系列雙電源設備和變化較慢的傳統電源設備,因此對多電壓監控以確保正常運行的需求應該變得更加重要。

我們還應該見證新的集成的引入,它將監控器與現在圍繞微處理器的其他組件相結合。如果外部芯片為處理器提供電源或通信,則其集成提供了縮小電路板面積、降低功耗和降低成本的機會。目前與監控器結合使用的一些功能包括低壓差穩壓器、DC-DC轉換器、非易失性存儲器和實時時鐘。

結論

最好的微處理器監控器是如此的設計和應用,以至于客戶永遠不會知道他們在系統中。此類系統始終正常通電,不會丟失或破壞數據,也不會 意外鎖定。

系統設計人員將現代主管視為一種低成本的保險單,可以使產品始終保持工作。主管還可以縮短制造商的上市時間,同時最大限度地減少現場問題、客戶服務和故障退貨。由于現在提供的產品種類繁多,采用非常小的 SOT23、SC70 和 TDFN 封裝,因此您可以優化需要低功耗、低電壓、多電源電壓和低成本的應用,而不會犧牲其功能。

審核編輯:郭婷

-

穩壓器

+關注

關注

24文章

4218瀏覽量

93619 -

微處理器

+關注

關注

11文章

2247瀏覽量

82320 -

定時器

+關注

關注

23文章

3237瀏覽量

114473

發布評論請先 登錄

相關推薦

保持產品正常工作—微處理器監控器以小封裝提供大保險

保持產品正常工作—微處理器監控器以小封裝提供大保險

評論