蔣修國 /文

編者注:對于PCB layout工程師而言,絕大數的時候都局限于長度限制,等長,包地,過孔數量等等,其實,很多時候這些都不是一成不變的,換個角度,會有不一樣的結果。

有一位微信好友問我:他們的PCB板上的USB3.0布線長度超標了200mil,在他們的產品上有沒有風險?對于這類反手就給了一個回復:你猜!!!當然,這不太符合一位SI工程師的作風,一般要回復他一句至理名言:It depends!

當然,話是這么說,其實這個問題的根源在于很多工程師并沒有特別理解“傳輸線長度標準范圍”的這一概念。

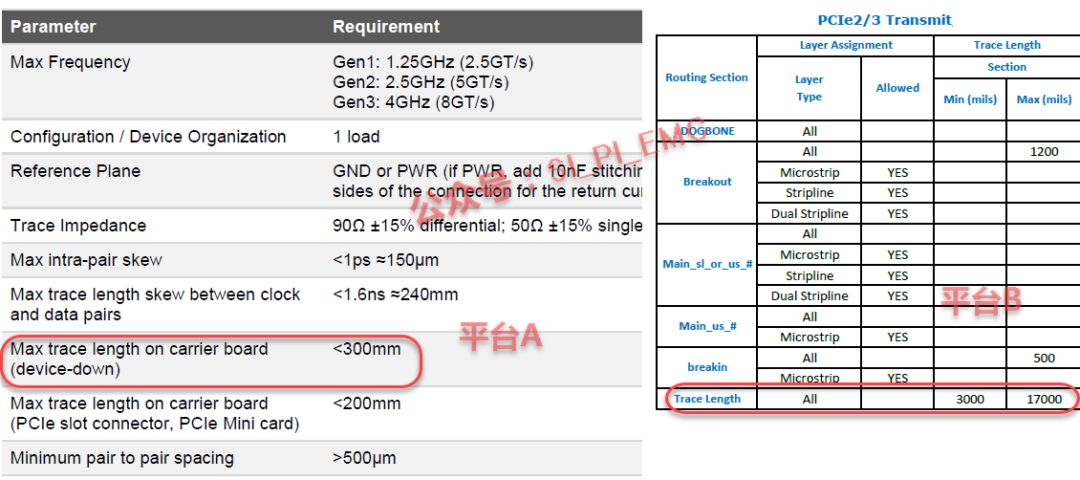

翻遍各類總線規范,基本找不出總線對長度的定義,那么這些長度的標準又來自于哪里呢?當然,大概歸納起來就兩個來源,一個是芯片設計手冊,所謂的designguide;另一個來源就是本公司(或者個人)的經驗。但是,不管是哪一種,都會在一些不相同的應用場景時,存在一些偏差。比如如下是兩個不同平臺的設計手冊針對PCIE3.0的要求:

顯然,平臺A最長只能12inch,而平臺B的可以達到17inch。所以如果工程師把B平臺的規則放到A平臺上,這就會導致長度超標,最終有可能導致產品設計失敗。而如果把A平臺的規則放置到B平臺上進行設置,雖然功能可能可以調試出來,但是如果非得要設計到17inch的長度,就會導致成本增加。

回到開始的那個問題,之所以會那樣回答,就是因為在什么都不清楚的情況下,只能像算八字一樣掰著手指算一算就猜。

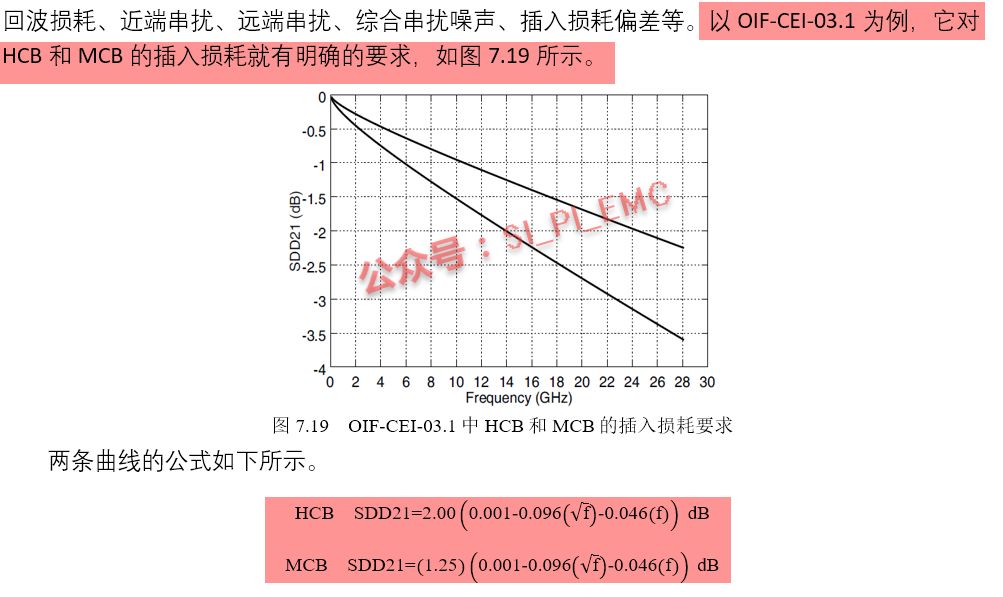

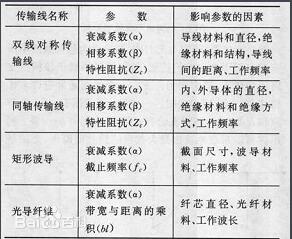

那規范中這些長度是如何給出來的呢?為什么每一個芯片平臺又不一樣呢?這其實就與每一顆芯片的驅動能力有關。所以我們在一些總線規范中會看到有對總線的損耗有一個要求,在《ADS信號完整性仿真與實戰》一書中也有給大家介紹到這個問題。如下圖所示:

規范中定義了這個損耗,在設計的時候產品的時候,就按照這規范以及實際電路的設計來確定PCB設計的長度等,這里要補充說明下,損耗不僅僅與長度有關系。這時就通過仿真能快速地獲得這個設計的長度要求,從而得出設計的規則。

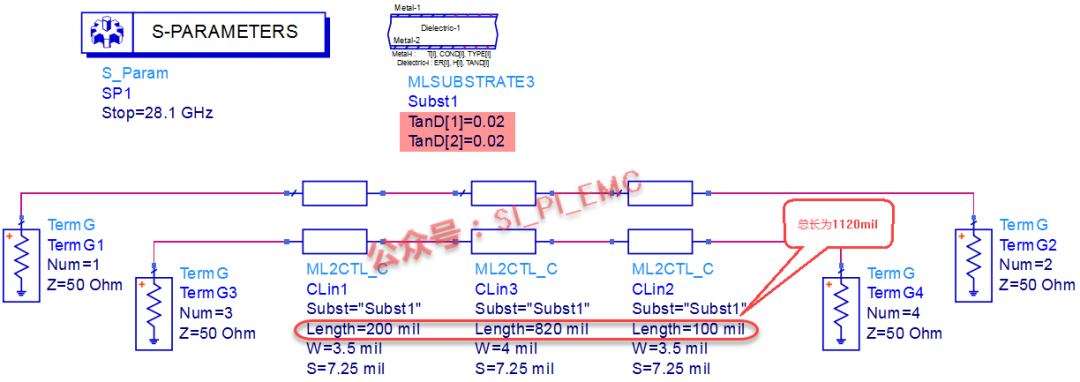

下面以HCB的要求為例,通過仿真來簡單介紹下。在仿真工具(ADS)中建立一個仿真模型,如下圖所示,傳輸線的總長度為1120mil,PCB材料的介質損耗角為0.02:

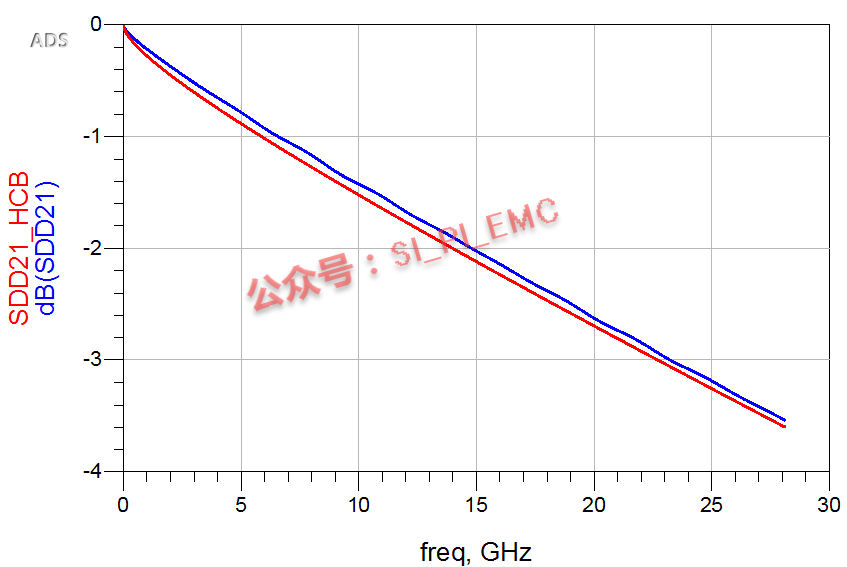

仿真得到的結果如下圖所示,紅色的曲線為規范要求,藍色的曲線為傳輸仿真獲得的結果。

顯然,這時傳輸線的總長度為1120mil是符合要求的。那當長度變為1750mil時,我們看看結果會變成什么樣呢?

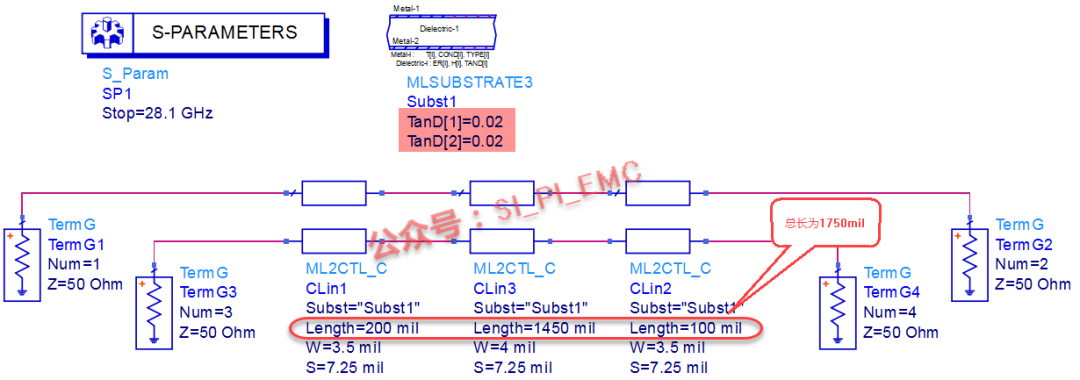

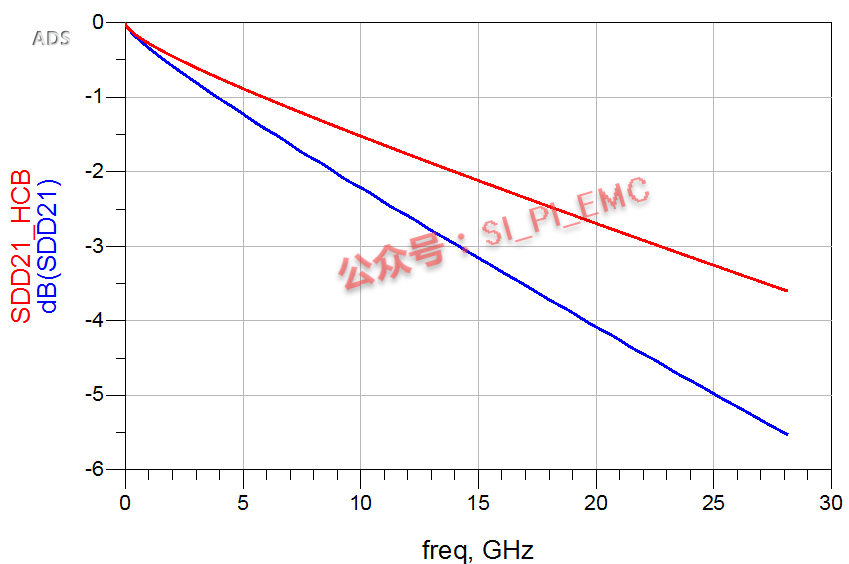

仿真得到的結果如下圖所示,紅色的曲線為規范要求,藍色的曲線為傳輸仿真獲得的結果。

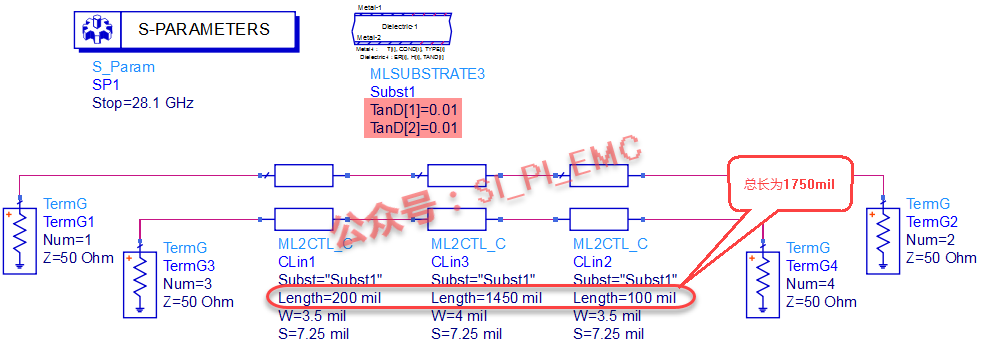

從上面這個結果可以看到,這個長度的損耗遠遠超過了規范要求的數值。這樣設計出來的產品肯定是不符合設計要求的。所以到這里,可能很多工程師就會說這個長度太長了,顯然不能滿足設計要求。結果真是這樣的嗎?如果把PCB材料的介質損耗角變為0.01時,長度還是為1750mil,如下圖所示:

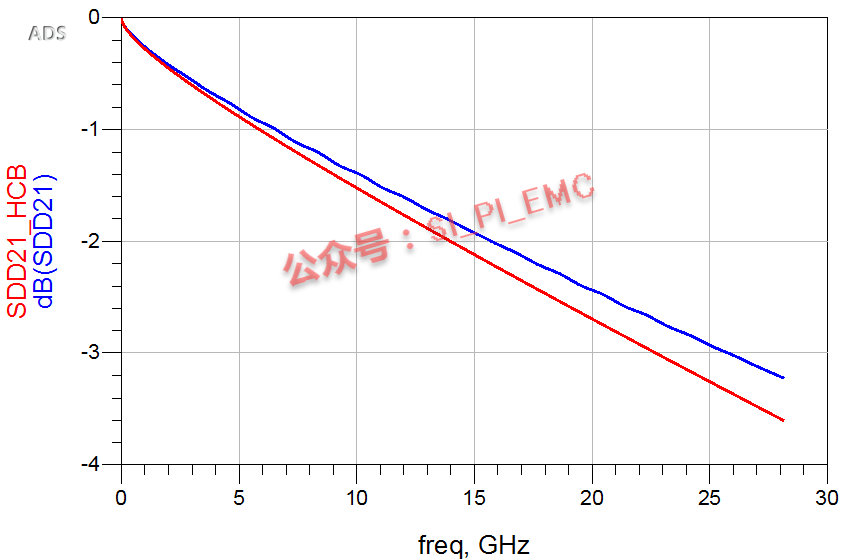

仿真得到的結果如下圖所示,紅色的曲線為規范要求,藍色的曲線為傳輸仿真獲得的結果。

從以上結果我們可以看到顯然,即使長度變長了,只要改變PCB材料參數,結果同樣也是符合規范要求的。

綜上所述,在不同的條件下,不管傳輸線的長度是1120mil還是1750mil,它們都有可能滿足規范或者設計系統的要求。所以我們不能單一地以某一長度來作為設計的準則,而是要根據實際設計的情況來確定。通過對實際情況的了解,通過建模仿真,就可以打破一些設計規則的約束,從而獲得符合自己特定場景的應用。

當然,并不是所有的規范都有一個非常明確的損耗要求,如果沒有這個損耗要求的時候怎么辦呢?大家可以在留言區說說你們的看法,后續我會再與大家分享。

審核編輯:湯梓紅

-

pcb

+關注

關注

4317文章

23014瀏覽量

396380 -

PCB設計

+關注

關注

394文章

4671瀏覽量

85301 -

總線

+關注

關注

10文章

2868瀏覽量

87995 -

Layout

+關注

關注

14文章

402瀏覽量

61661 -

傳輸線

+關注

關注

0文章

375瀏覽量

24000

原文標題:傳輸線長度長了一點行不行呢?

文章出處:【微信號:SI_PI_EMC,微信公眾號:信號完整性】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB傳輸線參數

傳輸線阻抗匹配有了一點經驗總結

差分線傳輸線長度差有關的問題

如何用LOTO示波器TDR方法測試電線長度?

工程師頭疼的差分線傳輸線長度差問題資料下載

PCB傳輸線參數

傳輸線長度長了一點行不行呢?

傳輸線長度長了一點行不行呢?

評論