5.1模式自適應

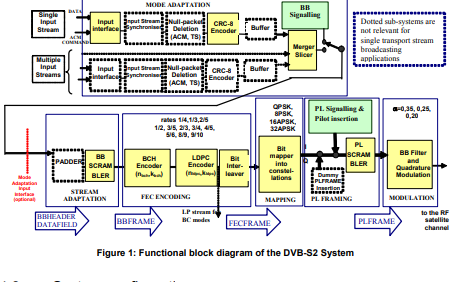

該子系統應在DATAFIELD中執行輸入接口、輸入流同步(可選)、空包刪除(僅針對TS輸入流和ACM)、用于錯誤檢測的CRC-8編碼(僅針對分組的輸入流)、輸入流合并(僅針對多個輸入流)和輸入流切片。最后,插入基帶信令,通知接收方所采用的模式自適應格式。

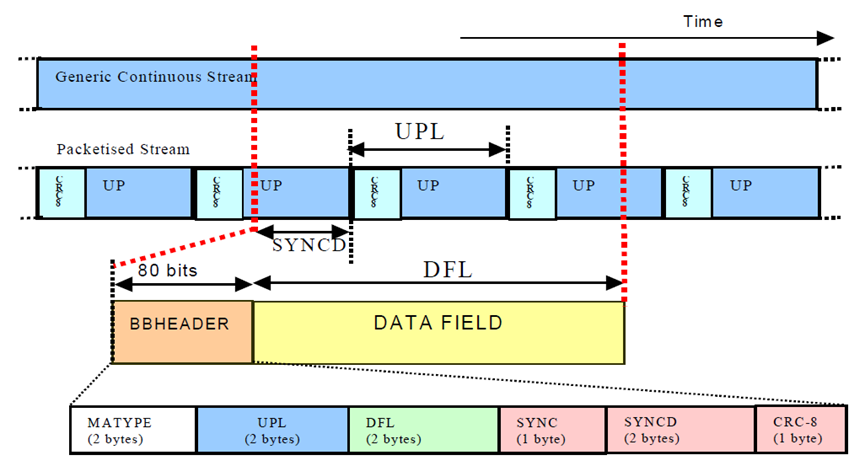

由圖3可知,輸入序列為:

單個或多個傳輸流(TS)。

單個或多個通用流(分組或連續)。

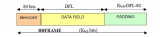

輸出序列是一個BBHEADER(80bit),后面跟著一個DATA FIELD。

5.1.1輸入接口

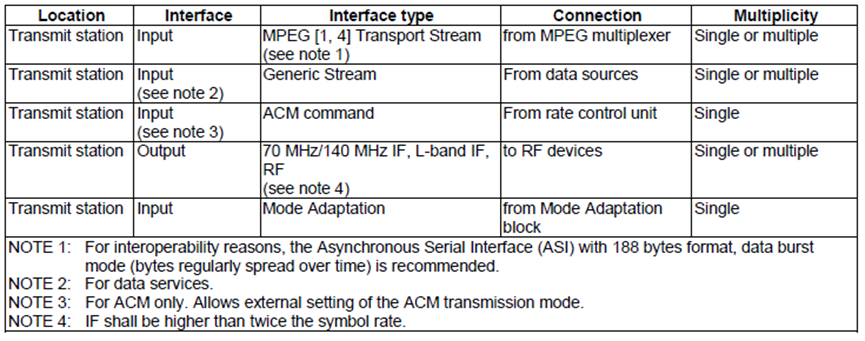

本文件所定義的系統應以表2所示的接口為界。

表2:系統接口

輸入接口子系統應將輸入電氣格式映射為內部邏輯比特格式。第一個接收到的比特將被表示為最高有效位(MSB)。

傳輸流應由恒定長度UPL =188 × 8比特(一個MPEG包)的用戶包(UP)來表征,第一個字節是同步字節(47HEX)。

通用流的特征是連續的比特流或長度為UPL比特(UPL最大值為64k, UPL = 0D表示連續流,參見5.1.5)的定長用戶包(UP)流。變長包流或超過64k bit的定長包應被視為連續流。

對于一般的分組流,如果一個同步字節是UP的第一個字節,則保持不變,否則在每個包之前插入一個同步字節= 0D, UPL增加8。UPL信息可以通過靜態調制器設置得到。

“ACM命令”信令輸入應允許通過外部“傳輸模式控制單元”設置DVB-S2調制器將采用的傳輸參數,用于輸入數據的特定部分。ACM命令應根據第D.1條。

模式自適應(可選輸入)應是一系列數據字段(根據第5.1.5條),其中每個單獨的數據字段之前都有一個BBHEADER(根據第5.1.6條和圖3)和流適應命令(根據第I.1條),允許通過外部“3模式適應單元”設置DVB-S2調制器對每個特定MA包采用的傳輸參數。模式自適應應根據第I.1條(獨立信令電路)或I.2條(帶內信令)。

5.1.2 輸入流同步器(可選,與單個TS - BS無關)

DVB-S2調制器中的數據處理可能會對用戶信息產生可變的傳輸延遲。輸入流同步器子系統(可選)應提供適當的方法來保證對分組輸入流(例如傳輸流)的恒定比特率(CBR)和恒定的端到端傳輸延遲。此過程應遵循附件D中給出的規范。TR 102 376 [i.5]給出了接收機實現的示例。

5.1.3 空包刪除(僅限ACM和傳輸流)

對于ACM模式和傳輸流輸入數據格式,必須識別MPEG空包(PID = 8191D)并刪除。這樣可以降低信息速率并增加調制器中的錯誤保護。該過程的執行方式是將被刪除的空包重新插入到接收器中,在它們最初所在的確切位置。這一過程應遵循附件D中規定的規范。

5.1.4 CRC-8編碼器(僅用于分組流)

如果UPL = 0D(連續通用流),該子系統將不加修改地傳遞輸入流。

如果UPL≠0D,則輸入流是一個長度為UPL位的用戶數據包序列,前面有一個同步字節(當原始流不包含同步字節時,同步字節= 0D)。

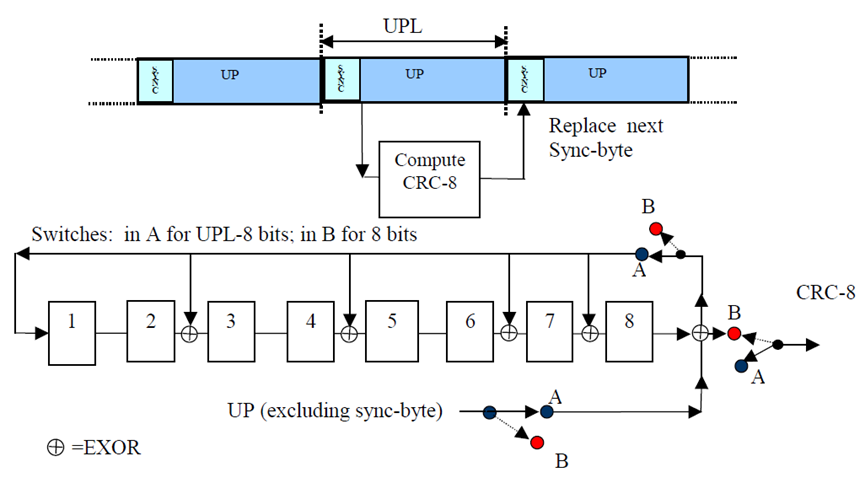

UP的有用部分(不包括同步字節)應由系統的8位CRC編碼器處理。生成器多項式應為:

CRC編碼器輸出應計算為:

CRC = remainder [u(X) : g(X)]

其中u(X)為系統編碼的輸入序列(UPL - 8位)。圖2給出了通過移位寄存器實現CRC生成器的可能方法。

在每個序列的第一個比特進入電路之前,寄存器應被初始化為全零。

計算出的CRC-8將取代后續UP的同步字節。如第5.1.6節所述,同步字節被復制到BBHEADER的SYNC字段中進行傳輸。

圖2:CRC-8編碼器的實現

5.1.5 合并/切片

根據圖3,合并/切片器輸入流被組織為通用連續流或分組輸入流。UP長度為UPL位(其中UPL = 0表示連續序列)。輸入流應被緩沖,直到合并/切片器讀取它們。

切片器應從其輸入(單個輸入流)或其中一個輸入(多個輸入流)中讀取(即切片)一個由DFL位(數據字段長度)組成的數據字段,其中:

Kbch-(10 × 8)≥DFL≥0(根據表5的Kbch, 80 bit專用于BBHEADER,見第5.1.6條)。

合并應在單個輸出中連接從其中一個輸入讀取和切片的不同數據字段。對于單個流,只應用切片功能。

數據字段(DATA FIELD)應由來自單個輸入端口的位組成,并應以同質傳輸模式(FEC代碼和調制)傳輸。合并/切片器優先級策略依賴于應用,應遵循表4(單一傳輸流廣播服務)和表D.2(用于其他應用領域)中描述的策略。

根據應用的不同,合并/切片器應該分配一個等于最大DATA FIELD容量的輸入位(DFL = Kbch -80),從而在后續的DATA FIELD中分解UP,或者應該在DATA FIELD中分配一個整數個UP,使DFL變量在上述指定的邊界內。

當在合并/切片器請求的任何輸入端口上沒有數據字段時,物理層幀子系統應生成并傳輸一個DUMMY PLFRAME(見第5.5.1條和表12)。

當同步字節被CRC-8替換后(見5.1.4),有必要為接收端提供一個恢復UP同步的方法(當接收端已經同步到DATA FIELD時)。因此,從DATA FIELD開始和第一個完整UP (CRC-8的第一個比特)開始的比特數(見圖3)將被合并/切片器檢測并存儲在基帶標頭的SYNCD字段(即SYNC Distance)中(見第5.1.6條)。例如,SYNCD = 0D意味著第一個USER PACKET與DATA FIELD對齊。

圖3:MODE ADAPTER輸出端的流格式

5.1.6 基帶頭(Base-Band Header)插入

在DATA FIELD前面插入一個10字節的固定長度基帶報頭(BBHEADER),描述其格式(假設內部碼率為1/2,由BBHEADER引入的最大效率損失為0.25 % nldpc =64 800, 1% nldpc = 16 200)。

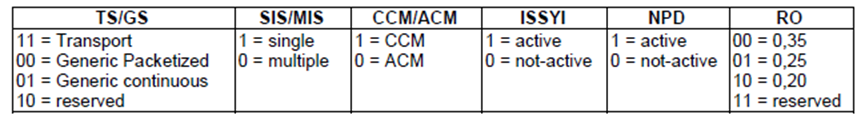

MATYPE(2 byte):描述輸入流格式、模式自適應類型和傳輸滾降因子,如表3所示。

第一個字節(MATYPE-1):

TS/GS字段(2 bit):傳輸流輸入或通用流輸入(分組或連續)。

SIS/MIS字段(1 bit):單輸入流或多輸入流。

CCM/ACM字段(1 bit):固定編碼和調制或自適應編碼和調制(VCM信號為ACM)。

ISSYI(1 bit),(Input Stream SynchronizationIndicator):如果ISSYI = 1 = active,則ISSY字段在UP之后插入(見附件D)。

NPD(1 bit):空包刪除激活/不激活。

RO(2 bit):傳輸滾降系數(α)。

第二字節(MATYPE-2):

如果SIS/MIS =多個輸入流,則第二個字節=輸入流標識符(ISI);否則保留第二個字節。

UPL(2字節):用戶數據包長度,單位為比特,取值范圍為0 ~ 65535。

例1:0000HEX=連續流。

例2:000AHEX= UP長度為10bit。

例3:MPEG傳輸流數據包的UPL = 188x8D。

DFL(2字節):數據字段長度,單位為bit,取值范圍0 ~ 58112。

例4:000AHEX=數據字段長度為10bit。

SYNC(1字節):用戶數據包同步字節的副本

對于分組傳輸或通用流:用戶包同步字節的副本;

對于連續通用流:SYNC= 00 - B8保留傳輸層協議信令根據參考ETR 162 [i.4];SYNC=B9-FF用戶私有)。

例5: SYNC = 47HEX,MPEG傳輸流數據包。

例6: SYNC = 00HEX,當輸入的通用分組流不包含同步字節時, (因此接收端在CRC-8解碼后,應該刪除CRC-8字段而不重新插入同步字節)。

SYNCD (2 bytes):

對于分組傳輸或通用流:從數據字段的開始到該幀的第一個UP (CRC-8的第一個比特)的距離,單位為比特。SYNCD = 65535D表示DATA FIELD中沒有UP啟動;

對于連續通用流:SYNCD= 0000 - FFFF保留供將來使用。

CRC-8(1字節):應用于BBHEADER前9個字節的錯誤檢測碼。

CRC-8采用圖2的編碼電路計算(開關A為72位,開關B為8位)。

BBHEADER的傳輸順序來自TS/GS字段的MSB。

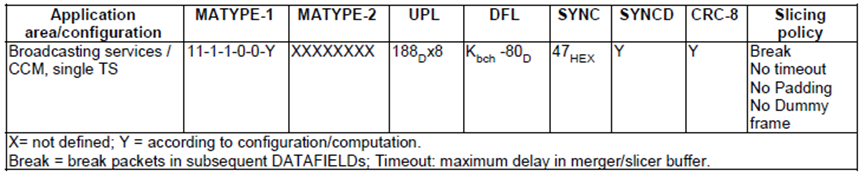

表4顯示了單個傳輸流廣播服務的BBHEADER和切片策略。對于其他應用領域,BBHEADER和合并/切片策略定義如表D.2所示。

表3:MATTYPE-1字段映射

表4:單傳輸流廣播服務的BBHeader(模式適應特征)和切片策略

審核編輯:劉清

-

DVB

+關注

關注

1文章

90瀏覽量

34689 -

調制器

+關注

關注

3文章

834瀏覽量

45109 -

同步器

+關注

關注

1文章

95瀏覽量

14617 -

ACM

+關注

關注

0文章

32瀏覽量

10318 -

CRC效驗

+關注

關注

0文章

30瀏覽量

1093

原文標題:DVB-S2標準協議:模式自適應(中文版)

文章出處:【微信號:FPGA算法工程師,微信公眾號:FPGA算法工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

國內外主流DVB-S ,DVB-S2及ISDBT 方案,功能

N5182A信號發生器能生成dvb-s2信號嗎?

采用MSD7S45的海外DVB-S2高清機頂盒方案

基于MSD7S01的DVB-S2機頂盒方案

DVB-S/DVB-S2信號發生器 (DVB-S/S2 Si

基于人工神經網絡的DVB-S2數字信號調制模式識別

基于PXA270 和STi710x 的雙CPU DVB-S2

基于PXA270和STi710x的雙CPU DVB-S2標準

國際市場大豐收 從直播星到DVB-S2

瀾起科技發布DVB-S2解調芯片M88DS3103

SUNNISKY TS2000-S2 DVB-S2衛星數字信號處理器

瀾起科技推出DVB-S2/S衛星數字電視接收前端單芯片M88RS6000

DVB-S2新一代數字衛星廣播標準資料免費下載

DVB-S2標準協議:模式自適應

DVB-S2標準協議:模式自適應

評論