一、軟件與硬件平臺

軟件平臺:

操作系統:Windows 8.1

開發套件:ISE14.7

硬件平臺:

FPGA型號:XC6SLX45-CSG324

二、ChipScope介紹

ChipScope是Xilinx提供的一個校驗FPGA設計的工具。它的本質是一個虛擬的邏輯分析儀,能調用FPGA內部的邏輯資源對代碼中的各個變量進行抓取分析。與ModelSim等一些其他的FPGA仿真工具不同的是,ChipScope可以直接反映代碼在實際硬件上的執行情況,從而能夠更加有效的定位設計中的問題。

三、目標任務

本文會以一個4-bit的計數器為例來給大家演示如何使用ChipScope來校驗這個計數器的功能。對于一個4-bit的計數器來說,計數器的最低位bit0是時鐘信號的2分頻,bit1是時鐘信號的4分頻,bit2是時鐘信號的8分頻,最高位bit3是時鐘信號的16分頻。接下來,我們就利用ChipScope來驗證這個邏輯的正確性。

我的開發板上有四個LED燈和四個按鍵,所以我會把計數器的4-bit分別綁定到四個LED燈上面,然后在邏輯里面設計一個異步復位按鈕用來復位這個計數器,同時設計這個異步復位還有一個目的就是用來設置初始的觸發條件,這一點后面會詳細介紹。

四、待測代碼

module led_top ( input I_clk , input I_rst_n , output reg [3:0] O_led_out ); always @(posedge I_clk or negedge I_rst_n) begin if(!I_rst_n) O_led_out <= 4'd0 ; else O_led_out <= O_led_out + 1'b1 ; end endmodule

寫好待測代碼,并添加物理約束文件綁定好管腳,我的開發板上的約束文件如下

NET I_clk LOC = V10 | TNM_NET = sys_clk_pin | IOSTANDARD = "LVCMOS33"; TIMESPEC TS_sys_clk_pin = PERIOD sys_clk_pin 50000 kHz; NET I_rst_n LOC = N4 | IOSTANDARD = "LVCMOS15"; ## SW2 pushbutton NET O_led_out<0> LOC = V5 | IOSTANDARD = "LVCMOS33"; ## LED1 NET O_led_out<1> LOC = R3 | IOSTANDARD = "LVCMOS33"; ## LED2 NET O_led_out<2> LOC = T3 | IOSTANDARD = "LVCMOS33"; ## LED3 NET O_led_out<3> LOC = T4 | IOSTANDARD = "LVCMOS33"; ## LED4

五、ChipScope使用完整流程

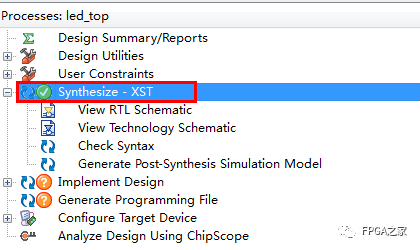

1、利用上面的待測代碼和約束文件在ISE14.7中建立一個新工程。然后點擊Synthesize-XST把整個工程綜合一遍。

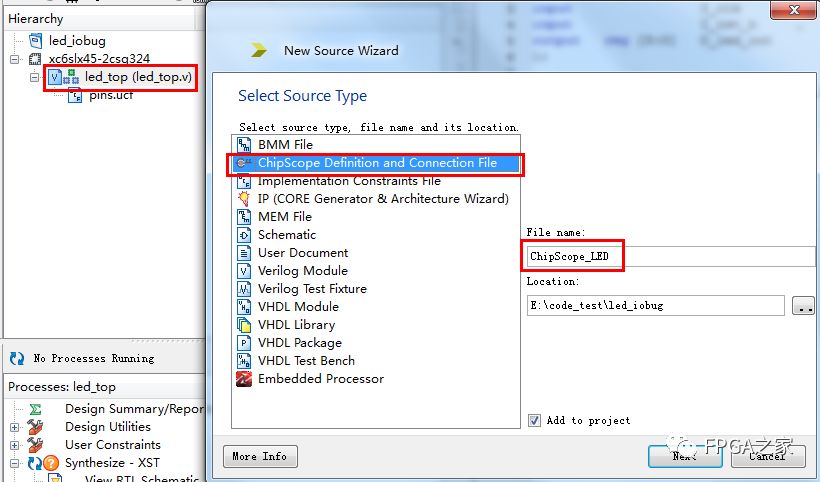

2、選中頂層模塊名led_top,然后鼠標右鍵選擇New Source選項,在彈出的New Source Wizard界面中選擇第二個ChipScope Definition and Connection File選項,并取名字ChipScope_LED(名字可以隨便取),然后點擊Next

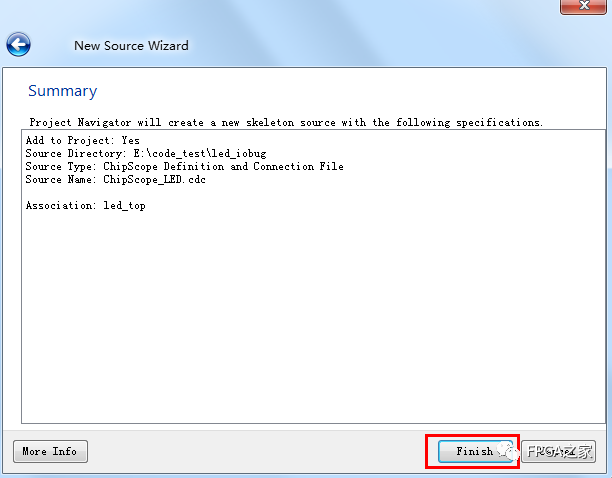

3、點擊Next以后在彈出的一下對話框中點擊Finish

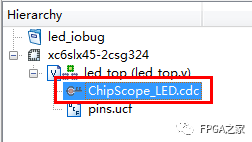

4、Finish點擊完畢以后,等一段時間,工程的層次目錄就多出來了一個后綴為.cdc的ChipScope文件

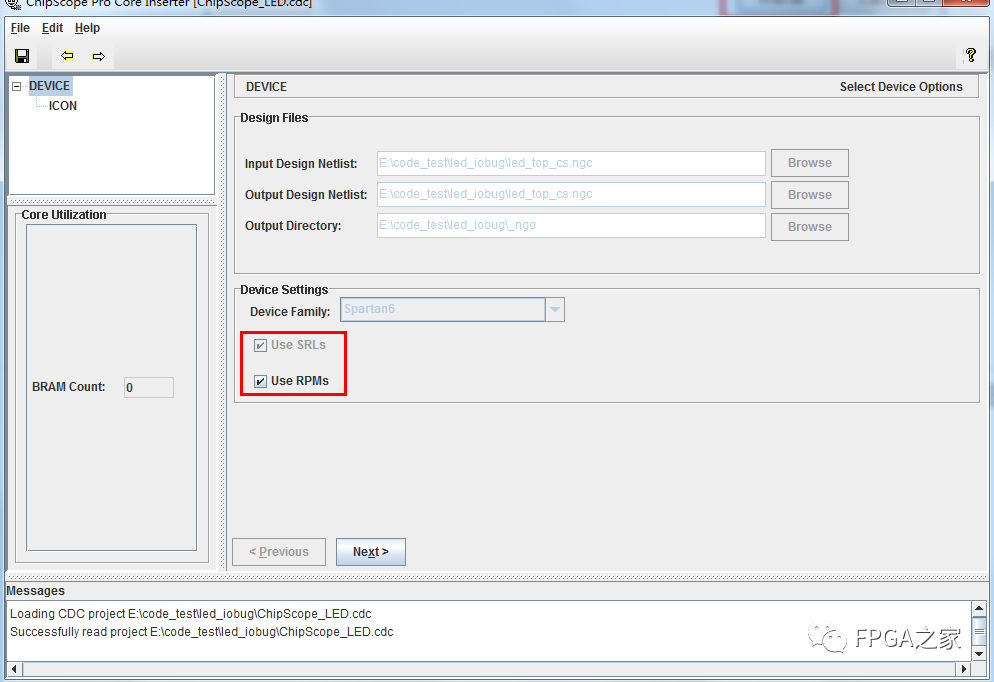

5、雙擊ChipScope_LED.cdc文件,會彈出下面的界面,使用默認的設置保證Use SRLs和Use RPMs處于選中狀態

Use SRLs(SRL = Shift Register LUT)選項使編譯器用移位寄存器的查找表(Shift Register LUTs)代替觸發器(flip flops)和乘法器,因此它能有效的減少FPGA內部資源,提高ChipScope性能

Use RPMs(RPM = Relationally Placed Macros)包含RLOC約束,RLOC定義了潛在設計原語的順序與結構。Use RPMs讓編譯器用FMAP,HMAP,ROM,RAM等相關聯的宏模塊,使邏輯塊布局的更加合理,可以有效的提高速度與性能,并節省FPGA資源

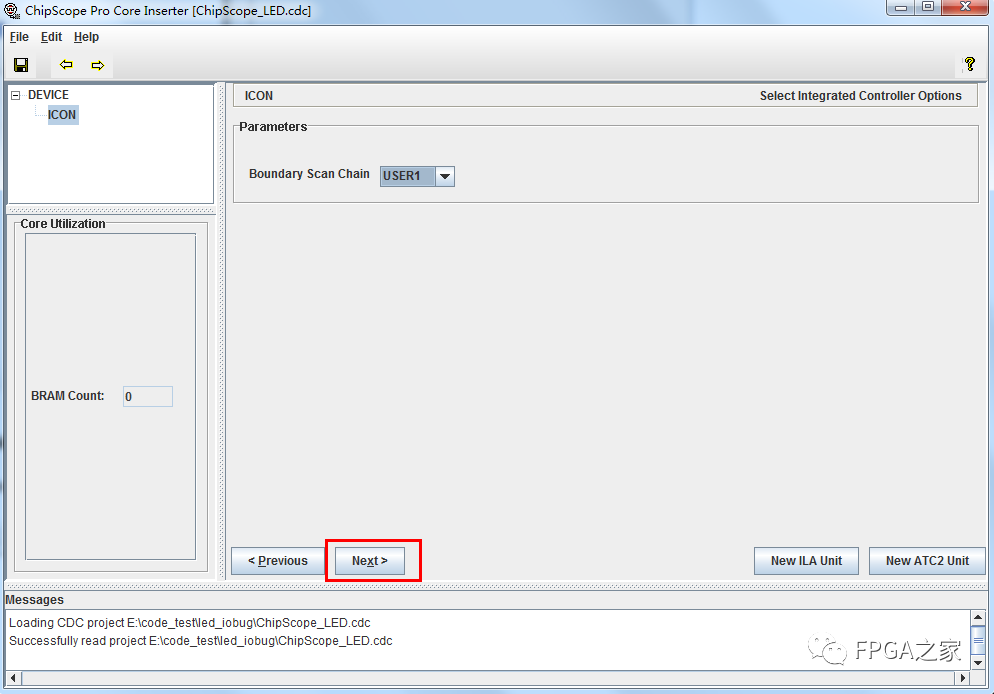

6、上一步選擇完并點擊Next后彈出如下界面,這個界面保持默認設置

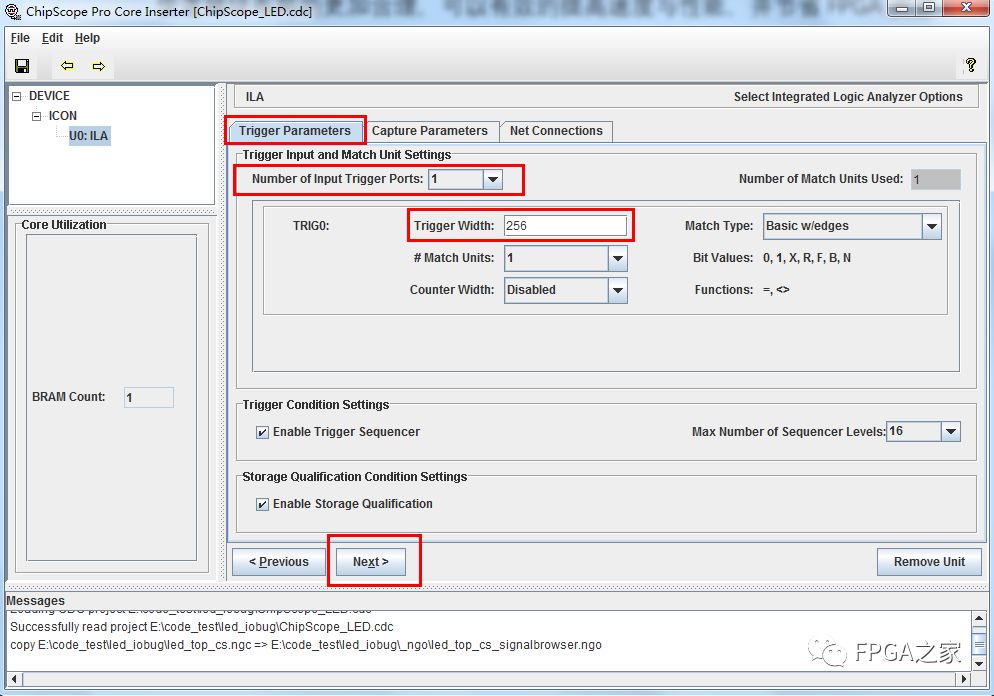

7、繼續點擊Next彈出如下界面。在這個界面中選擇觸發端口(Trigger Ports)的數目和它們各自的寬度(Trigger Width),

說明:

a、這里建議先把觸發寬度(Trigger Width)選擇為最大值256,后面等信號添加完畢以后在回來修改為信號的總寬度。這么做是因為在一個比較復雜的設計中,你事先根本不知道自己要抓多少信號,所以等你把要抓的信號都設置好了以后在回來修改這個參數是比較好的選擇。

b、Match Type的類型一共有6種,每種支持的值類型與功能見下表

| Match Type | Bit Values | Functions |

| Basic | 0,1,X | =,<> |

| Basic w/edges | 0,1,X,R,F,B,N | =,<> |

| Extended | 0,1,X | =,<>,>,>=,<,<= |

| Extended w/edges | 0,1,X,R,F,B,N | =,<>,>,>=,<,<= |

| Range | 0,1,X | =,<>,>,>=,<,<=,in range,not in range |

| Range w/edges | 0,1,X,R,F,B,N | =,<>,>,>=,<,<=,in range,not in range |

表中各參數的含義如下:

| 參數 | 含義 |

| 0 | 低電平 |

| 1 | 高電平 |

| X | 不定值 |

| R | 上升沿(Rising) |

| F | 下降沿(Falling) |

| B | 雙邊沿(Both Edge) |

| N | 非邊沿(No Edge) |

| = | 等于 |

| <> | 不等于 |

| 小于 | |

| <= | 小于等于 |

| > | 大于 |

| >= | 大于等于 |

| in range | 在某個范圍內 |

| not in range | 不在某個范圍內 |

由于本例比較簡單,所以Match Type選擇為Basic就可以了

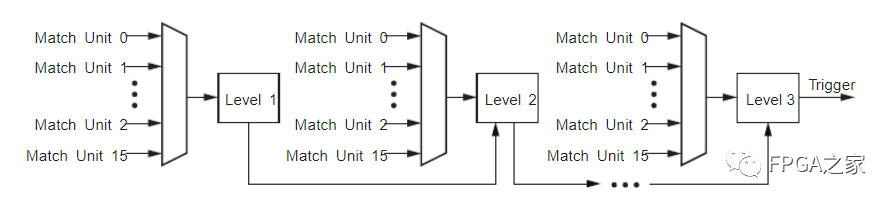

c、Enable Trigger Sequencer選項指定了觸發隊列的級數,這個值保持默認即可。觸發隊列的結構圖如下圖所示

d、Enable Storage Qualification選項可以通過用戶自定義的條件去過濾捕獲的數據,這個選項一般讓它默認選上

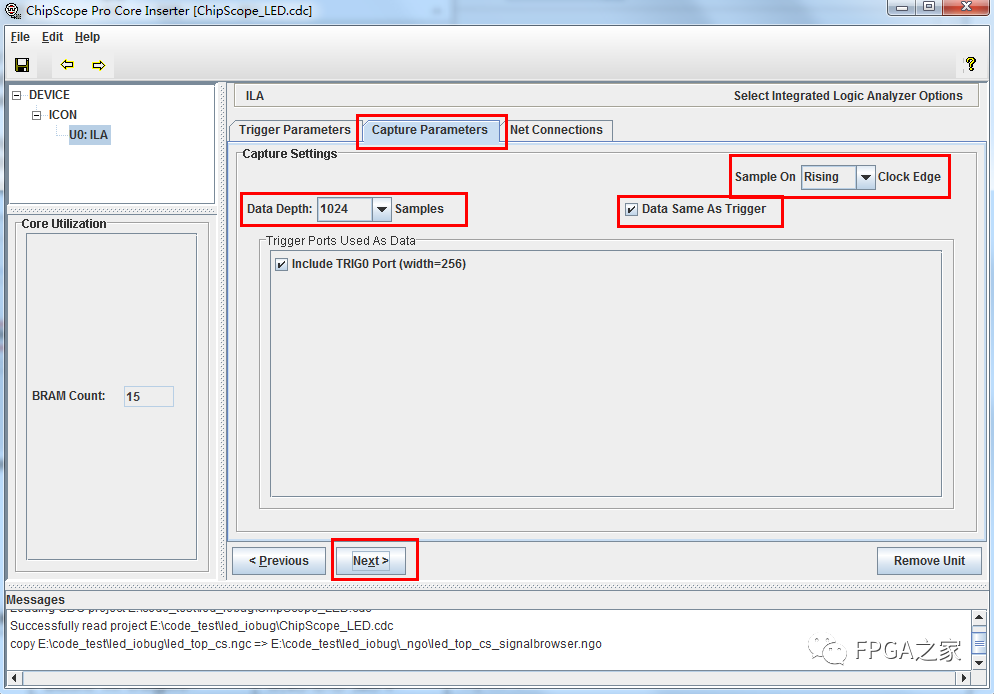

8、點擊Next進入Capture Parameter選項卡,這一頁在這個例子中保持默認參數即可

說明:

a、Data Depth指的是當觸發條件滿足以后,采樣的數據的個數。這個值設置的越大,那么你得到的信息就越多,但相應的占用的FPGA內部的資源也越多。如果你想抓取UART和IIC的數據,由于UART和IIC協議的傳輸速度較慢,所以這個值必須設置大一點才能看到比較多的信息,而對于SPI這種傳輸速度比較快的協議,這個值可以設置的小一些。

b、Data Same As Trigger選項的意思是你抓取的信號既可以觸發信號,也可以作為數據信號。這里給大家一個建議,對于inout信號(雙向信號),最好選擇只作為數據信號,不作為觸發信號。

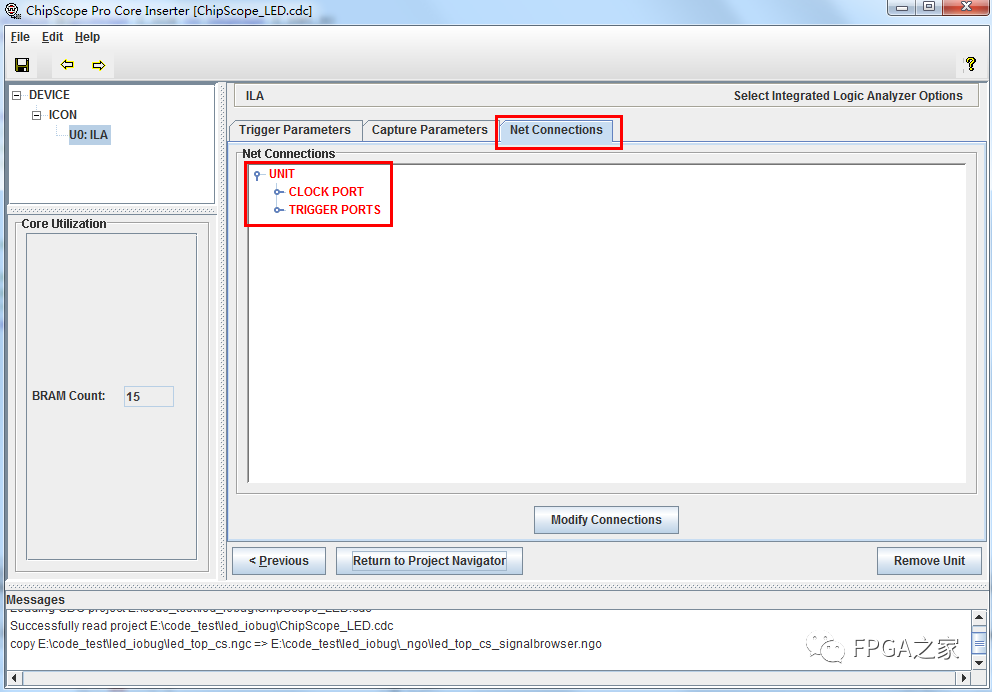

9、點擊Next,進入Net Connections選項頁

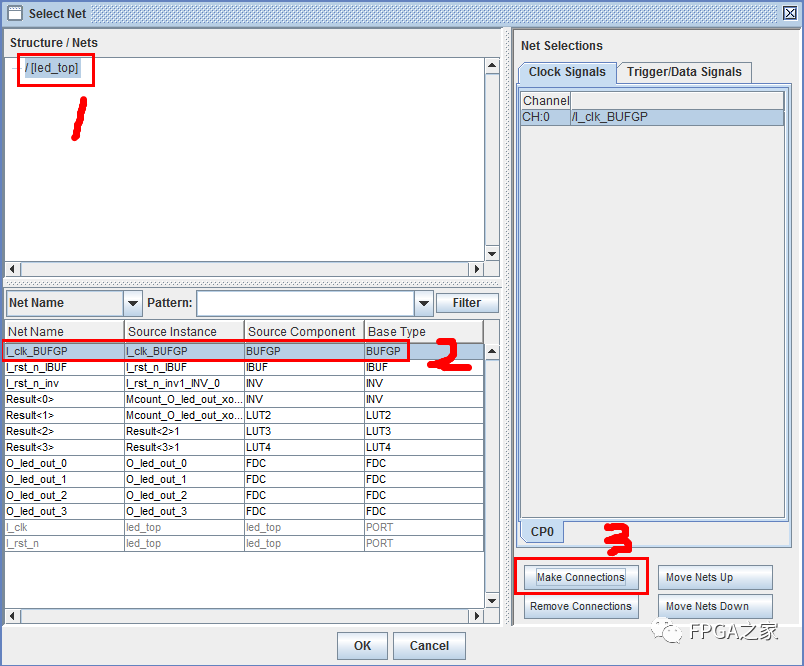

10、雙擊紅色的CLOCK PORT選項,在彈出的界面中按照下圖1、2、3的順序把時鐘信號連上

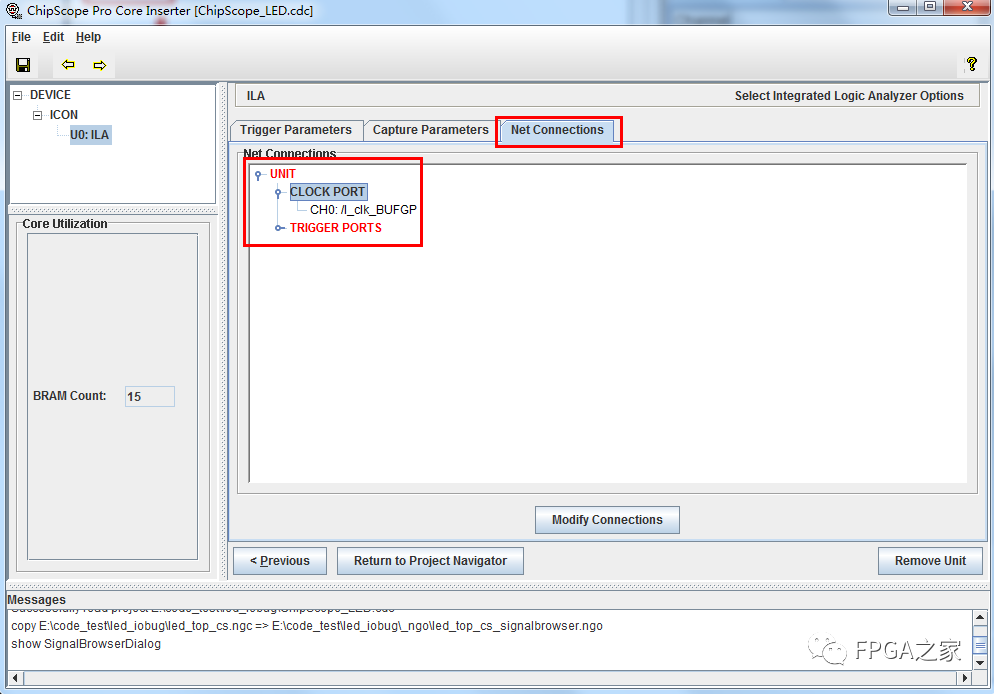

11、連好時鐘信號以后點擊OK,返回到Net Connections界面,發現CLOCK PORT已經由紅色變成了黑色,說明時鐘設置成功

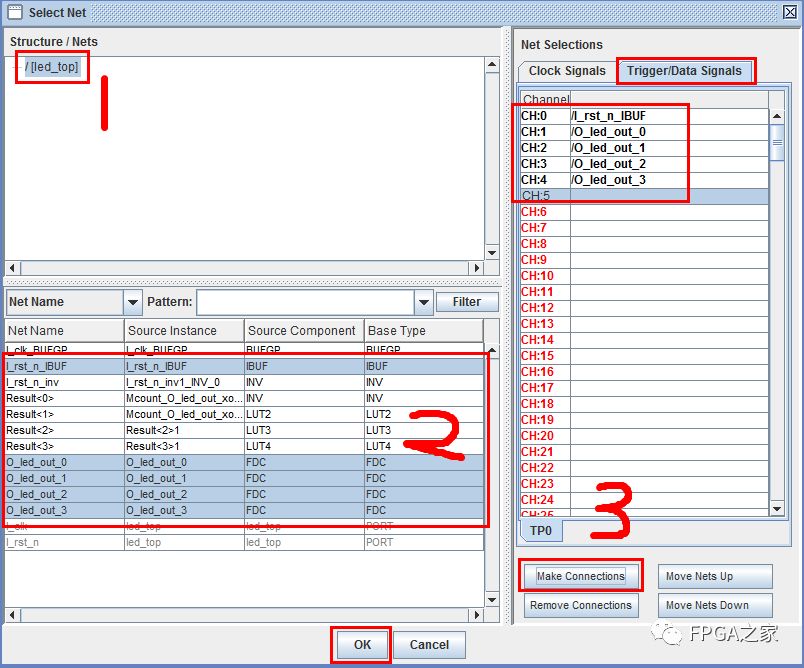

12、接著雙擊紅色的TRIGGER PORTS,在彈出的界面中按照下圖1、2、3的順序設置要抓取的信號

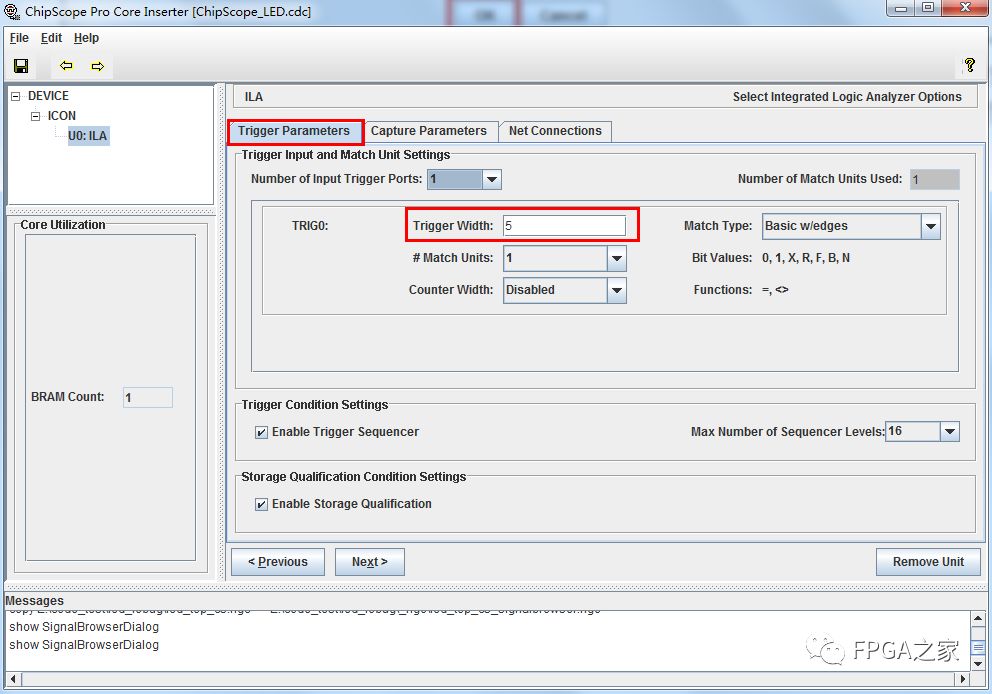

13、要抓取的信號設置完畢以后點擊OK返回Net Connections選項頁,發現TRIGGER PORTS還是紅色的,這是因為我們先前設置的要抓取信號的總寬度是256,而這里我們只抓了5個信號,所以需要返回Trigger Parameter頁把Trigger Width設置為5

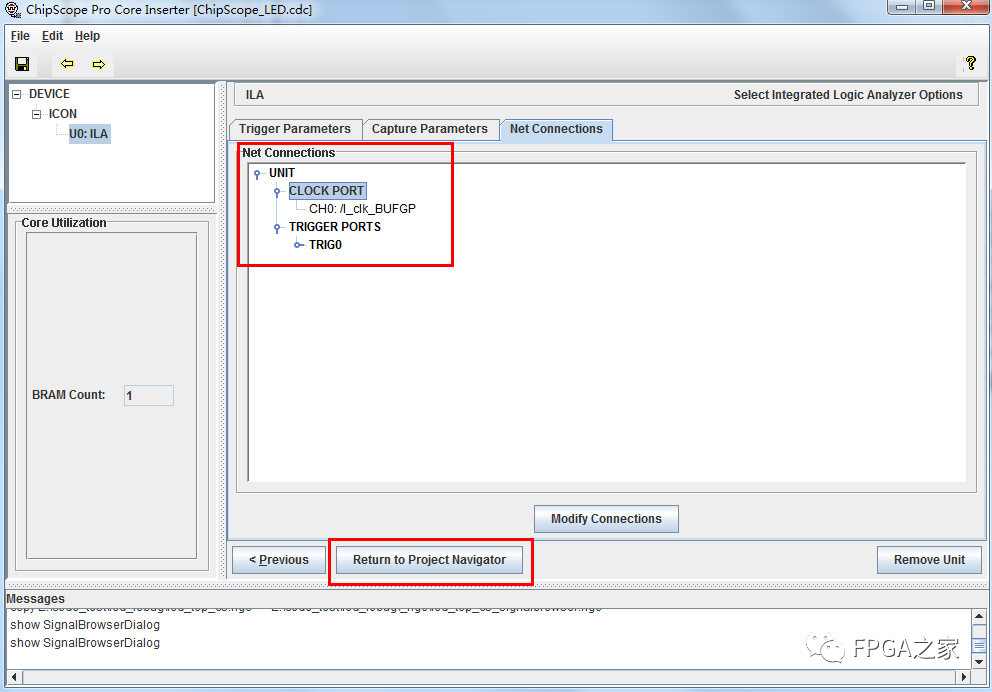

14、設置正確的Trigger Width以后,在回到Net Connections選項頁可以發現TRIGGER PORTS已經變成黑色的了,說明信號連接全部設置正確。然后點擊Return To Project Navigator

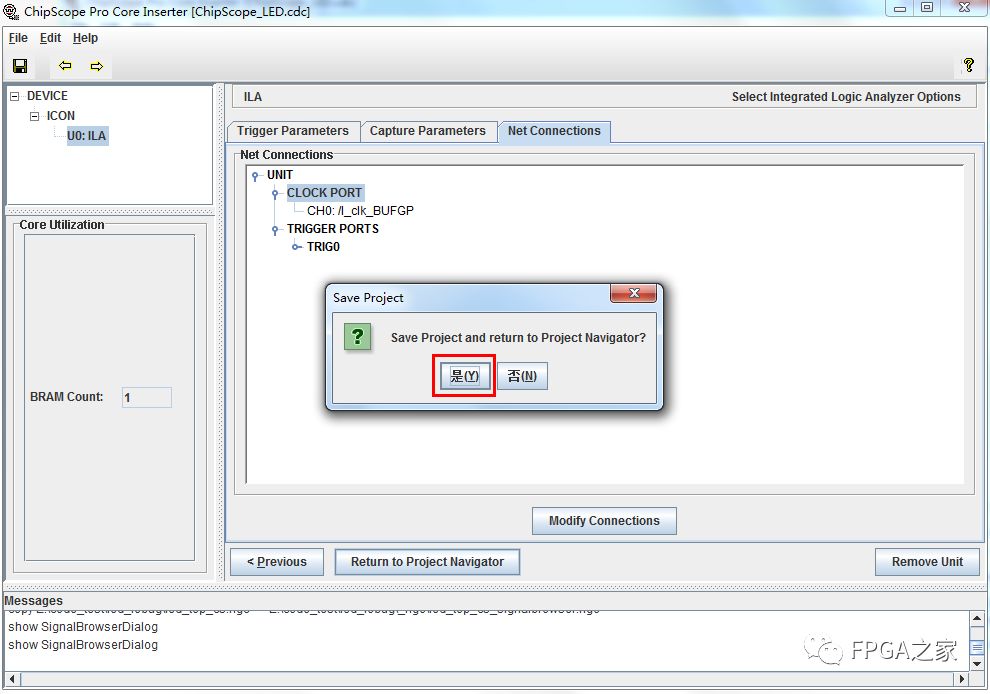

15、在彈出的Save Project對話框中選擇“是”

至此,整個.cdc文件的設置過程全部設置完畢。

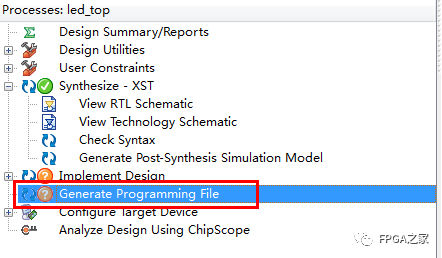

16、接著雙擊Generate Programming File生成bit文件

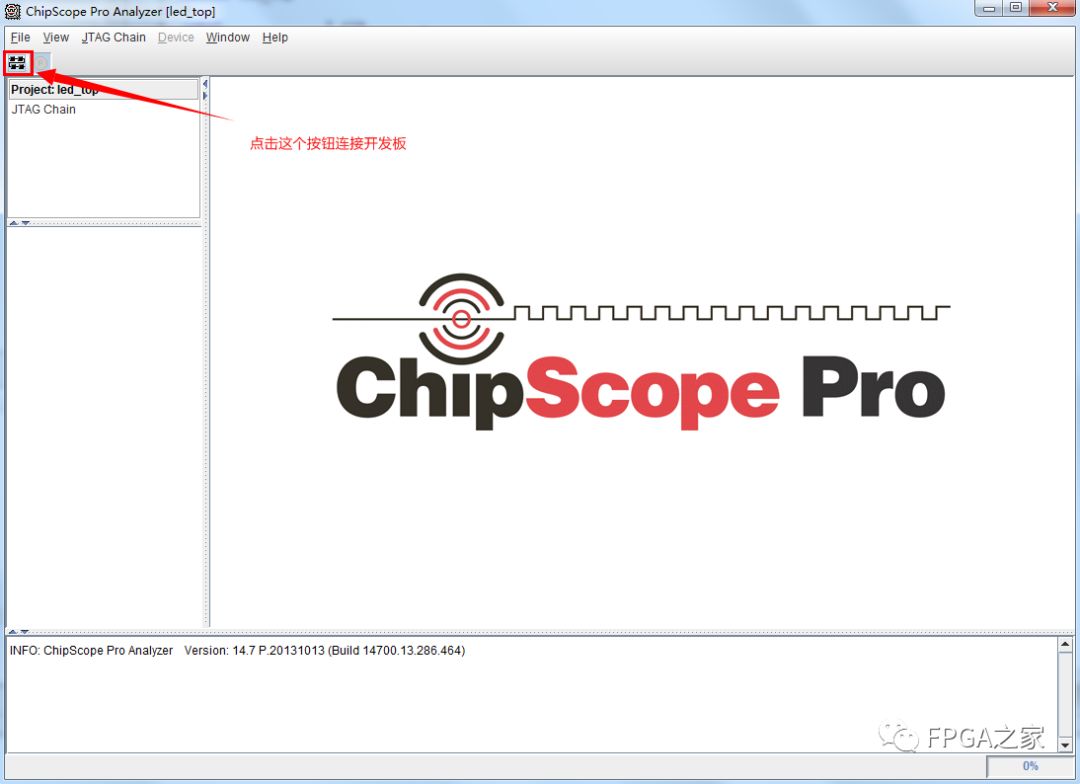

17、連接好開發板的Jtag線并上電。雙擊上張圖片最后一個選項Analyze Design Using ChipScope打開ChipScope界面如下所示

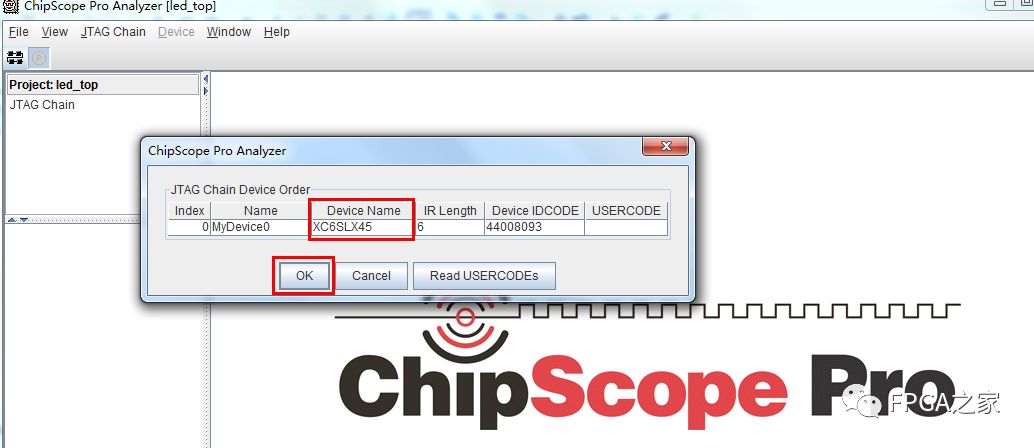

18、如果Jtag連接正常的話,會彈出下面的窗口,這個窗口表示找到了開發板使用的FPGA型號為XC6SLX45

19、點擊OK,左上角的P標簽變成了綠色,Jtag Chain多出了FPGA型號這個標簽

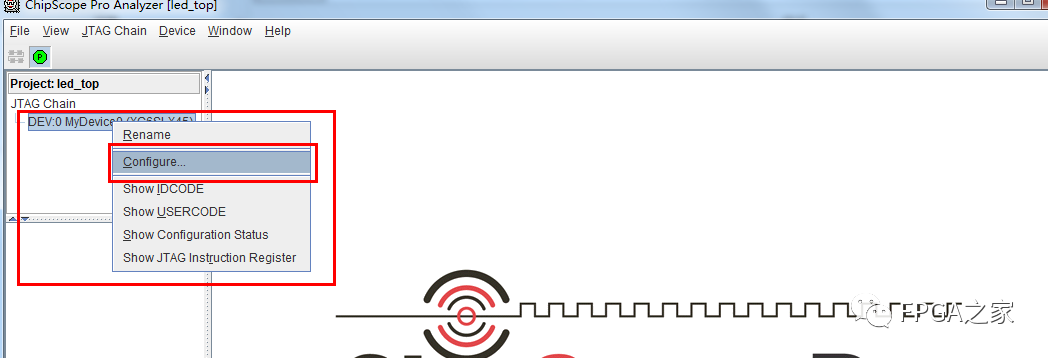

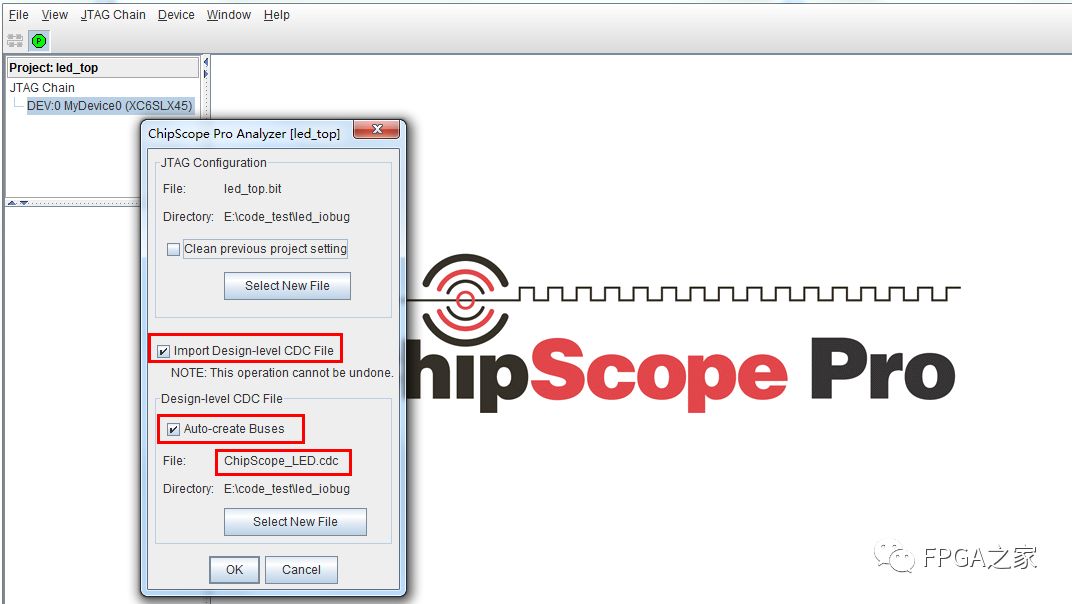

20、左鍵單擊選中DEV:0 MyDevice0 (XC6SLX45),然后右鍵彈出菜單欄,在菜單欄中選擇Configure..

21、在彈出的界面中勾選Import Design-level CDC File和Auto-create Buses兩個選項

22、點擊OK,bit文件就被下載到了開發板中,然后進入以下界面

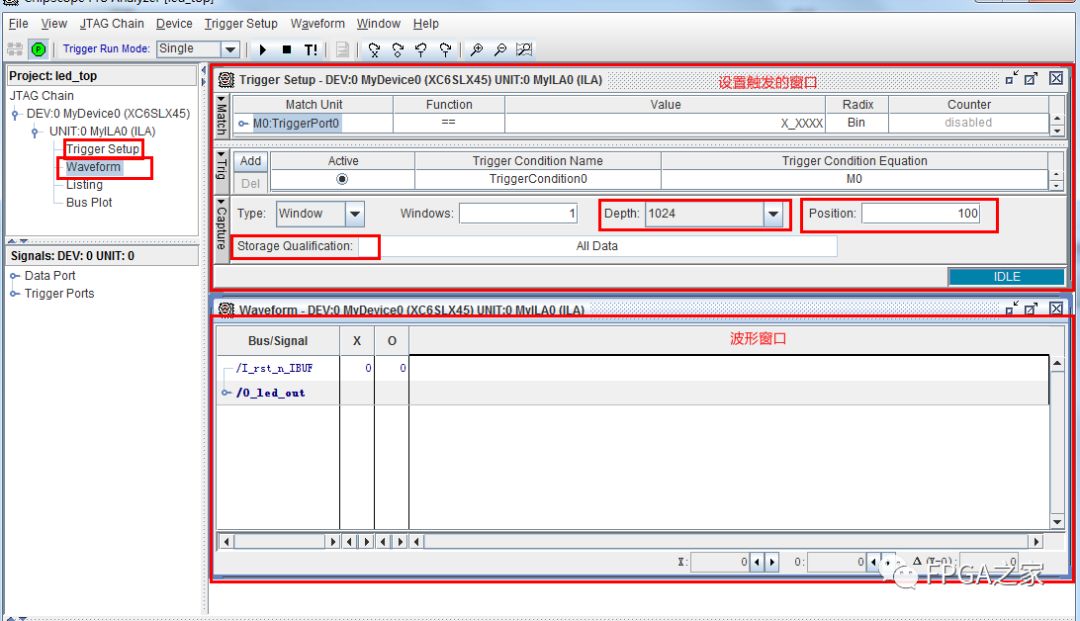

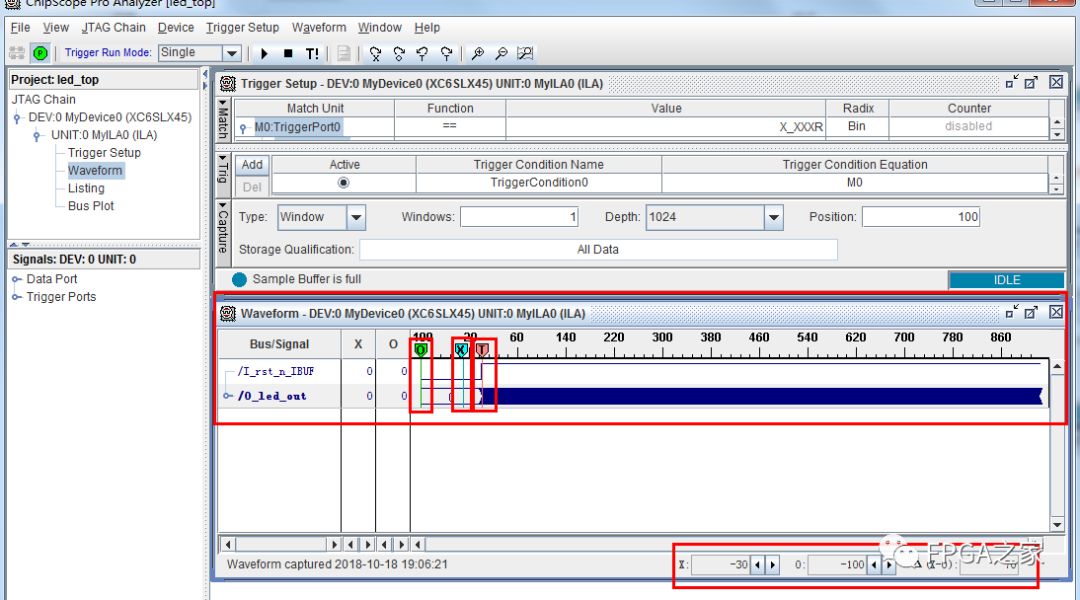

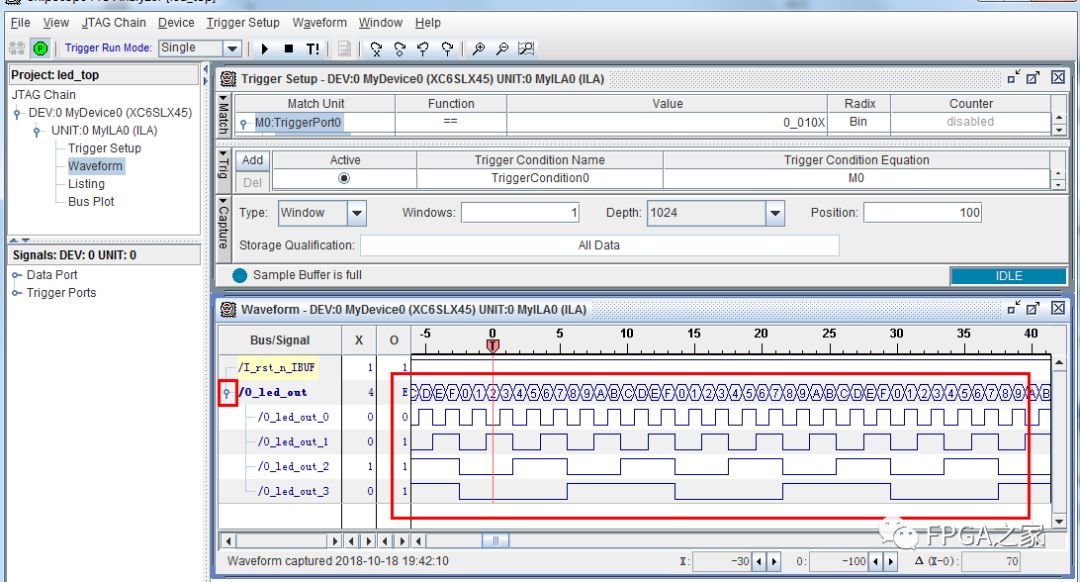

23、雙擊Trigger Setup和Waveform分別打開設置觸發的窗口和波形窗口

觸發窗口中的Depth就是我們之前在.cdc文件中設置要抓取的數據深度,Position這個參數默認情況是0,但是建議最好設置一個偏移量,這里我設置的是100,它表示的是把觸發條件滿足之前的100個數據和觸發條件滿足之后的924(1024-100)個數據顯示到波形窗口中,這樣我們就可以捕捉到在觸發之前的一部分信息,更有助于問題的定位。Storage Qualification這個參數就是之前在.cdc文件勾選了Enable Storage Qualification這個選項后才有的,一般選擇默認的All Data。

波形窗口是顯示要抓取的波形的窗口,這里還沒開始抓取,所以顯示為空。

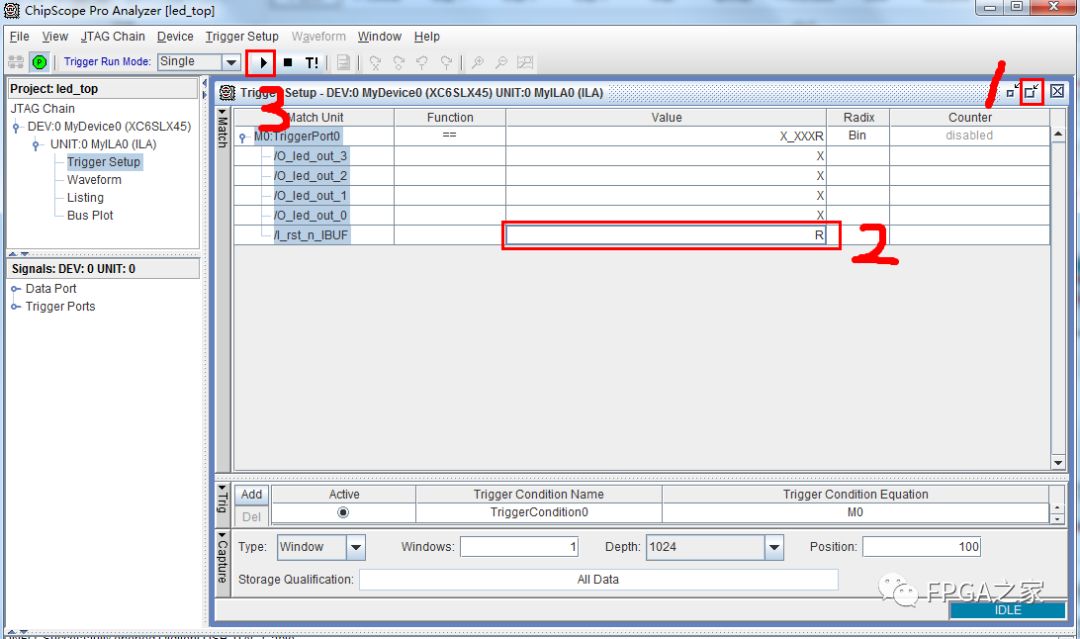

24、點擊右上角的1號圖標,把Trigger Setup窗口放大,然后設置觸發條件為I_rst_n為R(R表示上升沿觸發),接著點擊3號圖標進入等待觸發狀態

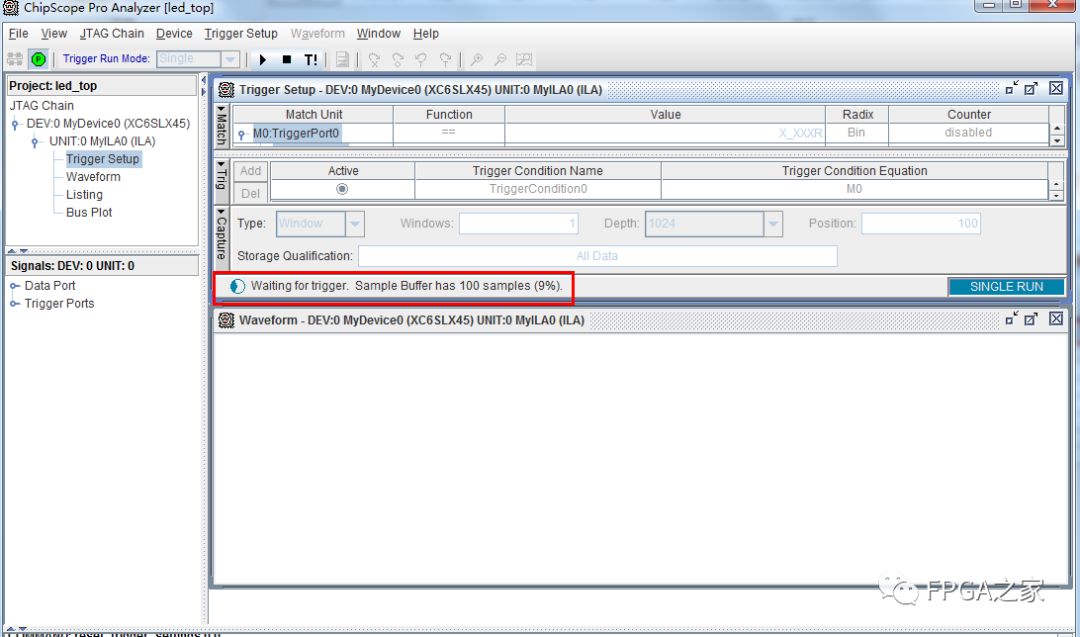

25、等待觸發狀態

26、按一下開發板上I_rst_n信號綁定的按鈕,使觸發條件滿足,波形窗口出現了抓到的波形

上圖中紅色的T標尺代表的觸發的起始位置,它的位置不能移動;綠色的O和藍色的X是兩個可移動標尺,他們兩個的絕對位置以及差值均顯示在波形窗口的右下角,有時候需要測量兩個關鍵點的差值就可以拖動這兩個標尺來直接得出結果

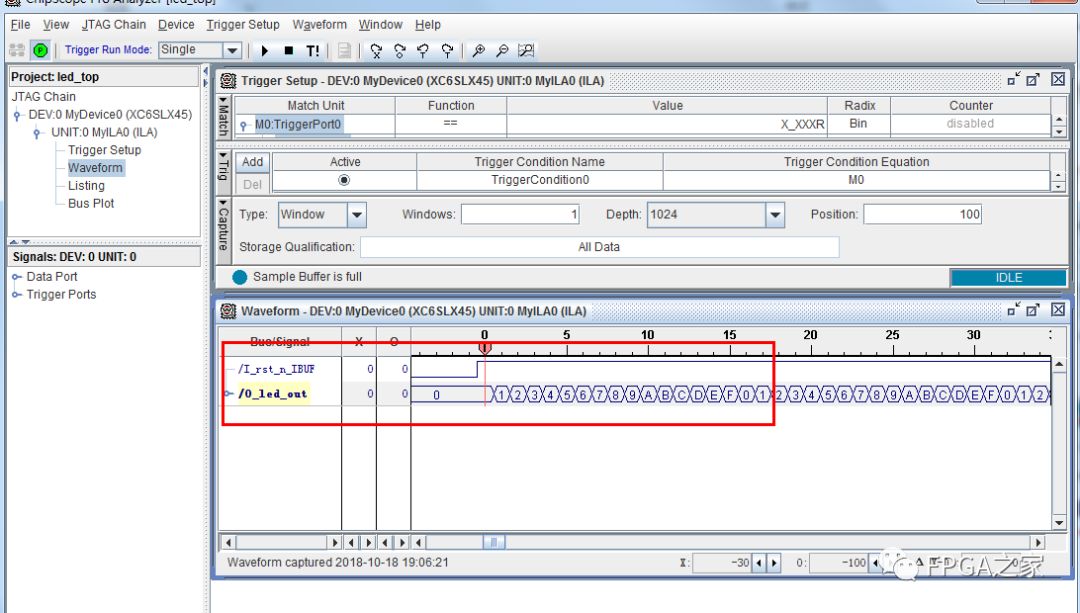

27、按住鼠標左鍵在波形窗口中畫一個矩形框可以把波形窗口放大,可以看到更多的波形細節

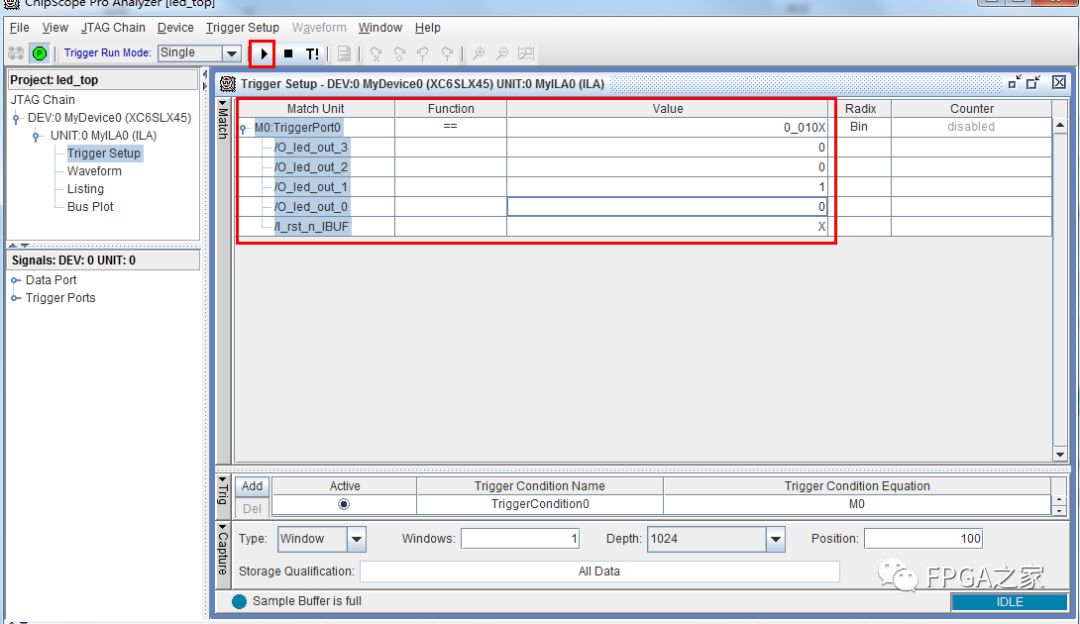

28、如果我想讓O_led_out為4’b0010的時候觸發,那么修改觸發條件為如下圖所示,然后點擊觸發按鈕

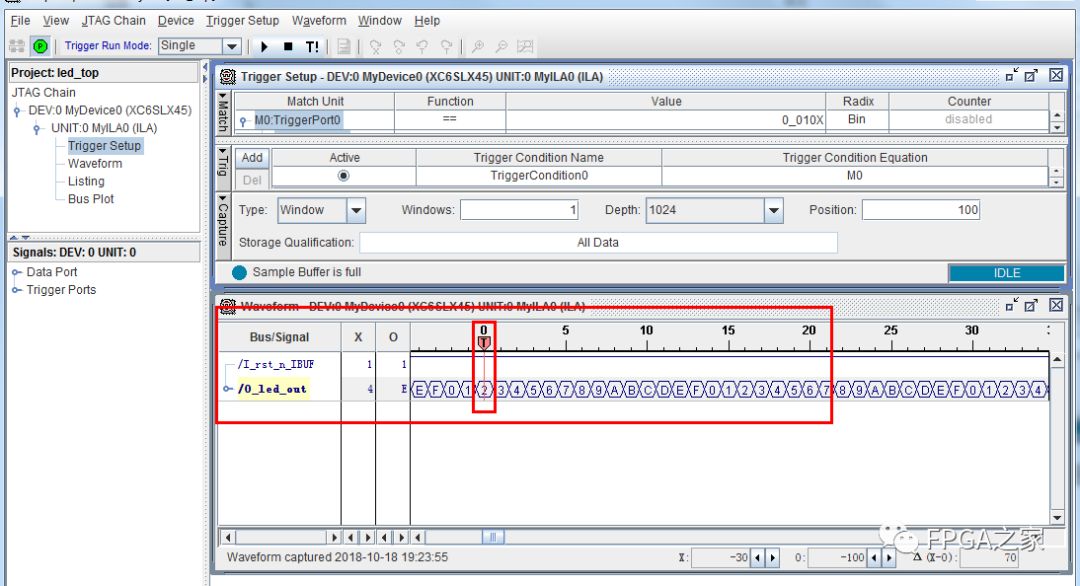

29、由于我們設置的O_led_out一直在自增,所以不需要按按鍵,等O_led_out為4’b0010觸發條件滿足就可以觸發了,觸發以后的波形如下圖所示

顯然觸發位置在O_led_out為4’b0010的位置,和之前設置的相同。

30、如果你想查看O_led_out總線每一個bit的波形情況,可以點擊一下信號名前面的小圖標展開

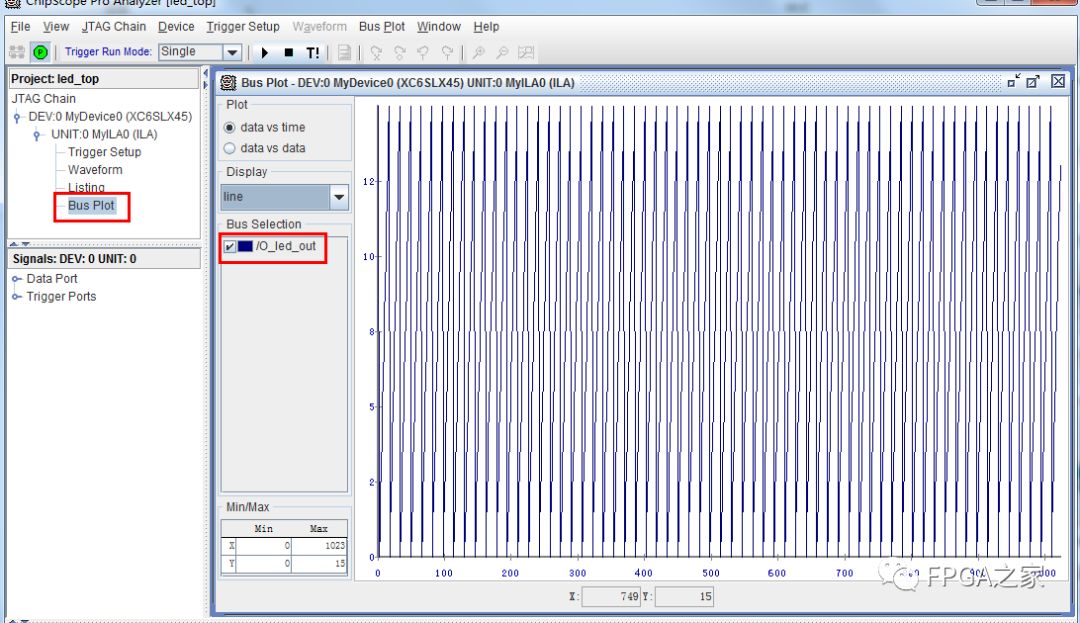

31、如果你想看O_led_out總線的模擬波形,那么你可以雙擊Bus Plot標簽,在彈出的界面中選中O_led_out總線就可以了

32、更多的功能大家有空可以多多嘗試。至此ChipScope的教程就完畢了。

六、如何防止信號被優化

在一個復雜的設計中,我們往往會抓大量的信號,而ISE14.7編譯代碼的時候會把一些有相同邏輯的信號給優化掉,這會導致我們在選擇信號的時候找不到想要抓取的信號,針對這種情況給大家提供兩個解決辦法。

方法一:

1、在你想要抓取的所有信號前面加上(*KEEP = “TRUE”*)

(*KEEP = "TRUE"*)reg [3:0] R_cnt;

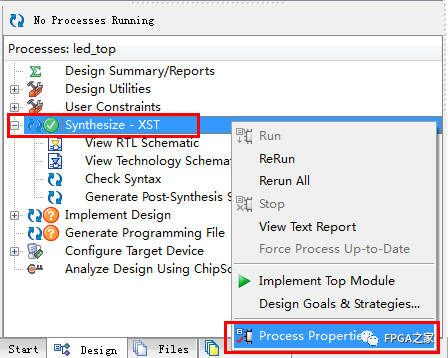

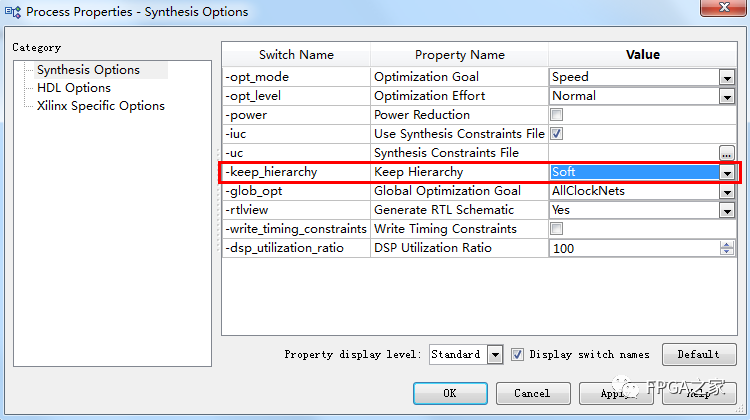

2、選中Synthesize-XST,鼠標右鍵在彈出的菜單欄中選擇Process Properties...

3、在彈出的窗口中選擇-keep_hierarchy為Soft,(Yes和Soft的區別我暫時不清楚,但是我習慣于選擇Soft,希望有網友能提供答案以及來源,謝謝)

4、設置完畢以后重新綜合,然后重新在.cdc選擇要抓取的信號

方法二:

上面一種方法根據我的經驗并不能100%的保證信號不被綜合掉,所以還有另外一種方法是寫一段冗余邏輯把信號進行運算然后賦值給一個輸出,并把輸出引到頂層綁定一個空閑的管腳,這種情況我的處理方法是:

假設要抓取的信號是(*KEEP = "TRUE"*)reg [3:0] R_cnt;

1、定義1個輸出信號O_test;

Output O_test;

2、把要抓取的信號各位相或然后賦值給O_test

assign O_test = | R_cnt ;

R_cnt前面的“|”表示把R_cnt的每一bit按位相或,這行代碼和

assign O_test = R_cnt[0] | R_cnt[1] | R_cnt[2] ;

綜合出來的邏輯是一模一樣的

3、把O_test引到頂層并在約束文件中分配一個空余管腳

通過這種增加冗余邏輯的方式,R_cnt信號一般不會被綜合掉,我自己在平時的使用中會先使用第一種方法,如果發現第一種方法還是把我想看的關鍵信號綜合掉了的話就采用第二種方法。

七、采用例化ILA核的方式抓信號

除了采用.cdc文件抓取信號以外,還有一種方式是采用例化ILA核的方式抓信號的時序。這種方式的詳細操作流程如下:

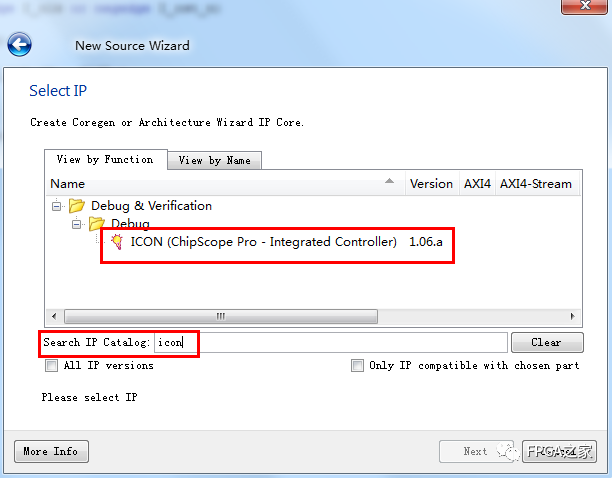

1、添加一個新的ICON IP核

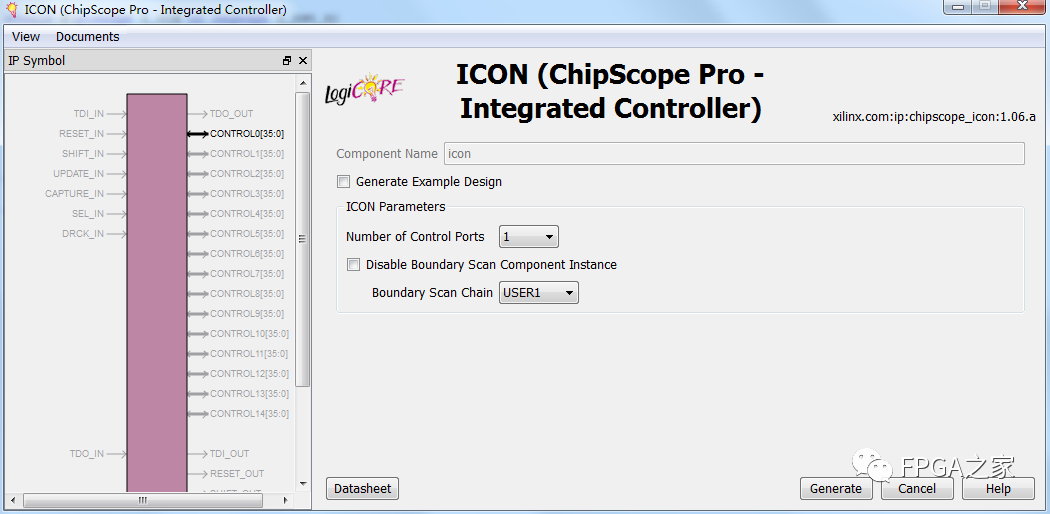

2、一般情況下保持所有的參數默認就可以了

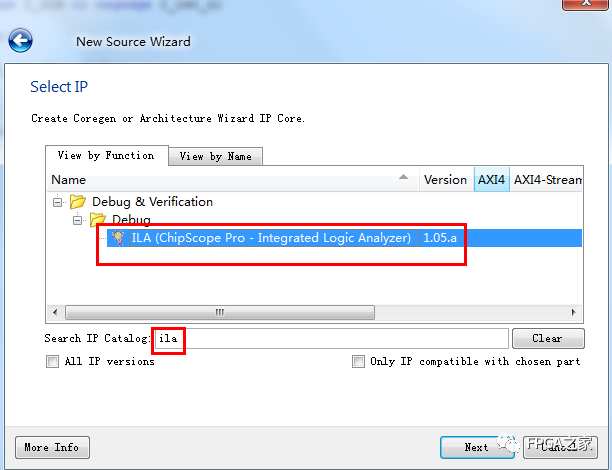

3、再添加一個ILA 的IP核

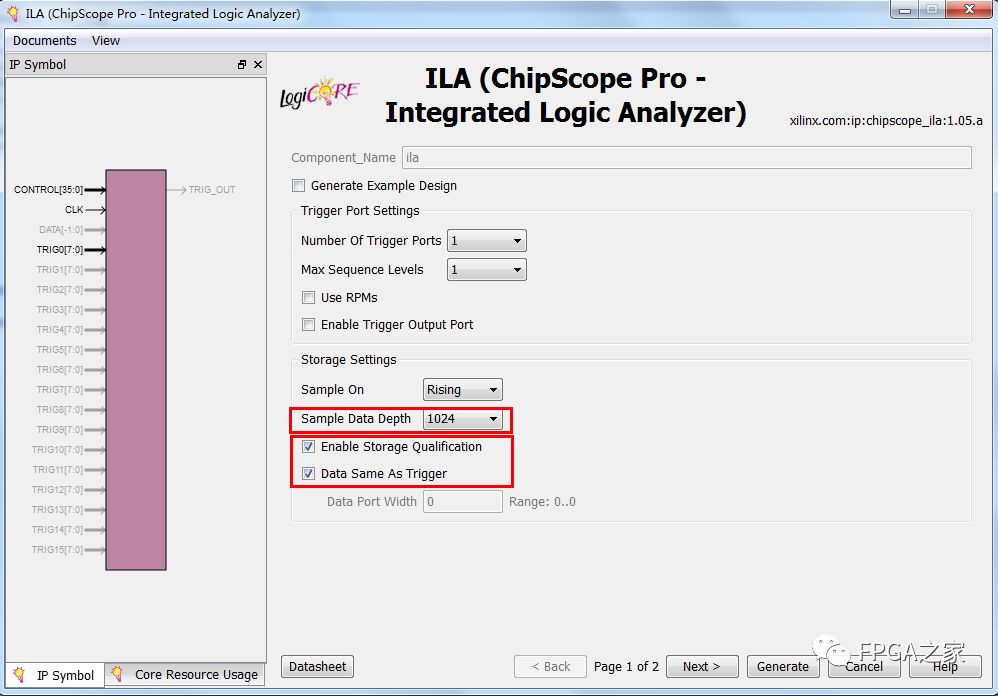

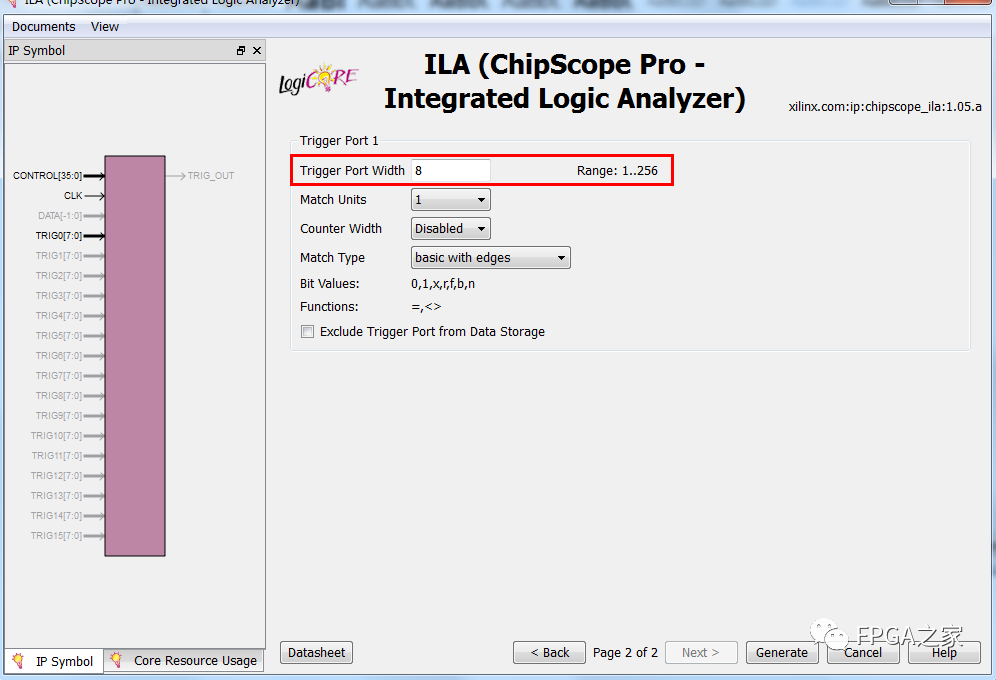

4、在第一頁設置好相關的參數,這些參數的含義核.cdc文件中參數的含義一模一樣,這里不再過多解釋

5、第二頁主要是設置要抓取的信號寬度,值得注意的是這里可以設置大一點沒關系,因為這種方法不要求信號寬度和要抓的信號數目完全相同

6、生成這個兩個IP核以后,把這兩個IP核例化到代碼中

module led_top

(

input I_clk ,

input I_rst_n ,

output reg [3:0] O_led_out

);

always @(posedge I_clk or negedge I_rst_n)

begin

if(!I_rst_n)

O_led_out <= 4'd0 ;

else

O_led_out <= O_led_out + 1'b1 ;

end

wire [35:0] CONTROL0;

wire [7:0] TRIG;

icon icon_debug (

.CONTROL0(CONTROL0) // INOUT BUS [35:0]

);

ila ila_debug (

.CONTROL(CONTROL0), // INOUT BUS [35:0]

.CLK(I_clk), // IN

.TRIG0(TRIG) // IN BUS [7:0]

);

assign TRIG[0]=I_rst_n;

assign TRIG[4:1]=O_led_out;

endmodule

接下來就是生成bit文件并用ChipScope抓取信號了,和前一種方法一樣。

這種方法和前一種方法的區別在于這種方法只能抓取一個.v文件中的信號,而且速度生成IP核的比較慢,進入ChipScope中以后還需要自己修改端口的名字,比較浪費時間;好處就是可以100%保證抓到想抓的信號,所以對于邏輯不太復雜的單文件代碼可以采用這種方式。不過我個人還是比較喜歡用.cdc文件的方式來抓信號。

八、總結

1、用ILA邏輯分析儀抓信號有兩種方式:.cdc文件方式(推薦)和例化ILA核方式

2、在cdc文件中防止信號被優化有兩種方式:keep_hierarchy選為Soft,增加冗余邏輯

審核編輯:劉清

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26489 -

led燈

+關注

關注

22文章

1592瀏覽量

107851 -

ROM

+關注

關注

4文章

562瀏覽量

85679 -

計數器

+關注

關注

32文章

2254瀏覽量

94372

原文標題:【設計經驗】2、ISE中ChipScope使用教程

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

求助:ISE10.1中新建文件的時候選擇目錄中沒有Chipscope的格式

使用Chipscope運行ISE時出現許可錯誤

加載ChipScope 64位Pro Analyzer時出現問題

chipscope13.1錯誤

可以在ISE webPACK中使用ChipScope Pro和串行I/O工具包嗎

如何解決使用ChipScope Analyzer時遇到的麻煩?

使用ChipScope分析設計,cpj文件沒有制作

請問具有完整的ISE14.7是否還需要Chipscope許可證?

無法啟動ISE 14.4 Chipscope怎么辦?

如何使用Xilinx ISE和Chipscope使用Vitex 5板進行測試和驗證?

Chipscope學習教程

Date功能:ISE中如何在未綜合實現的前提下打開ChipScope ?

ISE中ChipScope使用教程

ISE中ChipScope使用教程

評論