CPU、ASIC、FPGA 和存儲(chǔ)器等復(fù)雜器件通常需要電源排序。MAX16046為排序、監(jiān)視和電源裕量調(diào)節(jié)提供高度集成的方案。本應(yīng)用筆記給出了使用具有特定時(shí)序要求的多個(gè)器件的示例系統(tǒng),并提供了使用MAX16046的分步實(shí)現(xiàn)。

介紹

現(xiàn)代電子設(shè)備具有復(fù)雜的電源要求,涉及多個(gè)電壓軌。必須為 I/O 電壓供電;CPU、ASIC 和 FPGA 內(nèi)核電壓;鎖相環(huán)電壓;和存儲(chǔ)器終止電壓。其他設(shè)備需要高電壓、高電流或低噪聲電源,用于無(wú)線電收發(fā)器、超聲波換能器以及LCD或等離子顯示器等應(yīng)用。

使用多個(gè)電源的設(shè)計(jì)要求設(shè)計(jì)人員密切關(guān)注電源排序。每個(gè)電源軌必須按特定順序?qū)ǎ员苊鈴?fù)雜多電壓IC中的正向偏置保護(hù)二極管。如果只是同時(shí)打開電源,IC可能會(huì)遇到可靠性問(wèn)題甚至閂鎖。

除了電源排序之外,一些系統(tǒng)還實(shí)現(xiàn)了裕量調(diào)節(jié)。電壓裕度是一種控制電源電壓的方法,以充分利用所有容差的角度并確保系統(tǒng)可靠性。

Maxim提供多種電源管理解決方案。本應(yīng)用筆記重點(diǎn)介紹MAX16046,它可對(duì)多達(dá)12個(gè)電源軌進(jìn)行排序、監(jiān)視和裕量調(diào)節(jié)。

假設(shè)示例系統(tǒng)

以下假設(shè)系統(tǒng)將作為整個(gè)應(yīng)用筆記的示例。該系統(tǒng)是帶有MPC8548處理器和Virtex? 5 FPGA的通用板。表1顯示了為設(shè)計(jì)選擇的復(fù)雜IC所需的各種電壓。

表 1.電源電壓要求

| 名字 | 描述 | 規(guī)范 | 當(dāng)前 |

| VDD | Core supply | 1.1V ±55mV | 8A |

| AVDD | PLL supply | 1.1V ±55mV | |

| SVDD | SerDes core supply | 1.1V ±55mV | |

| XVDD | SerDes pad supply | 1.1V ±55mV | |

| GVDD | DDR2 I/O supply | 1.8V ±90mV | 0.5A |

| VTT | DDR2 termination | 0.49 × GVDD to 0.51 × GVDD | 0.5A |

| LVDD | Ethernet supply | 2.5V ±125mV | 0.1A |

| TVDD | Ethernet supply | 2.5V ±125mV | |

| OVDD | I/O supply | 3.3V ±165mV | 0.1A |

| BVDD | Local bus I/O supply | 3.3V ±165mV | |

| Virtex 5 Voltages | |||

| VCCINT | Internal supply | 0.95V to 1.05V | ~10A |

| VCCAUX | Auxiliary supply | 2.375V to 2.625V | 1A |

| VCCO | I/O supply | 1.14V to 3.45V | 1A |

| VDD | 1.8V ±100mV | 2.5A | |

| VDD | Core supply | 1.1V ±55mV | 8A |

| VDDL | 1.8V ±100mV | ||

| VDDQ | 1.8V ±100mV | ||

處理器和FPGA指定特定的時(shí)序順序,以防止內(nèi)部ESD二極管長(zhǎng)時(shí)間正向偏置。大型多電壓IC的順序通常是靈活的,但最好遵循制造商的首選順序。

MPC8548使用以下順序:

VDD

AVDD_n, BVDD, LVDD, OVDD, SVDD, TVDD, XVDD

GVDD

Virtex 5 使用以下序列順序:

VCCAUX

VCCO

每個(gè)器件為每個(gè)電源軌指定 50ms 的最大上電時(shí)間。Virtex 5還要求電源軌的啟動(dòng)速度不超過(guò)0.2ms。

圖1中的框圖有效地實(shí)現(xiàn)了電路的發(fā)電需求。

圖1.電源框圖。

由于 3.3V DC-DC 轉(zhuǎn)換器為所有下游負(fù)載點(diǎn) DC-DC 轉(zhuǎn)換器供電,因此需要在 10.3V 時(shí)提供至少 3A 的電流。n溝道MOSFET保持用于IO電壓的3.3V電源軌。0.9V LDO 提供 V電傳用于 1.8V DDR2-SDRAM 內(nèi)存。

現(xiàn)在實(shí)驗(yàn)系統(tǒng)的時(shí)序和監(jiān)測(cè)要求已經(jīng)確定,MAX16046可以用來(lái)實(shí)現(xiàn)這些要求。

利用MAX16046實(shí)現(xiàn)監(jiān)視、排序和裕量調(diào)節(jié)

硬件配置

如上所述,MAX16046可監(jiān)視多達(dá)12個(gè)電源軌、時(shí)序和裕量。監(jiān)控閾值、序列順序、裕量參數(shù)和其他配置值存儲(chǔ)在器件的內(nèi)部EEPROM中。實(shí)時(shí)監(jiān)控?cái)?shù)據(jù)可以通過(guò)SMBus?或JTAG接口讀取,這有助于在開發(fā)過(guò)程中檢查排序順序。

如果在工作期間發(fā)生電源故障,MAX16046可以自動(dòng)關(guān)斷電源并置位可配置故障輸出。該器件還可以配置為在內(nèi)部EEPROM中存儲(chǔ)有關(guān)故障的信息,包括電源軌電壓和通道狀態(tài),以供以后分析。此功能為分析在現(xiàn)場(chǎng)出現(xiàn)故障但在故障實(shí)驗(yàn)室中似乎正常工作的電路板提供了一個(gè)有用的工具。一旦發(fā)生故障,EEPROM將被鎖定,因此后續(xù)故障不會(huì)覆蓋存儲(chǔ)的故障數(shù)據(jù)。

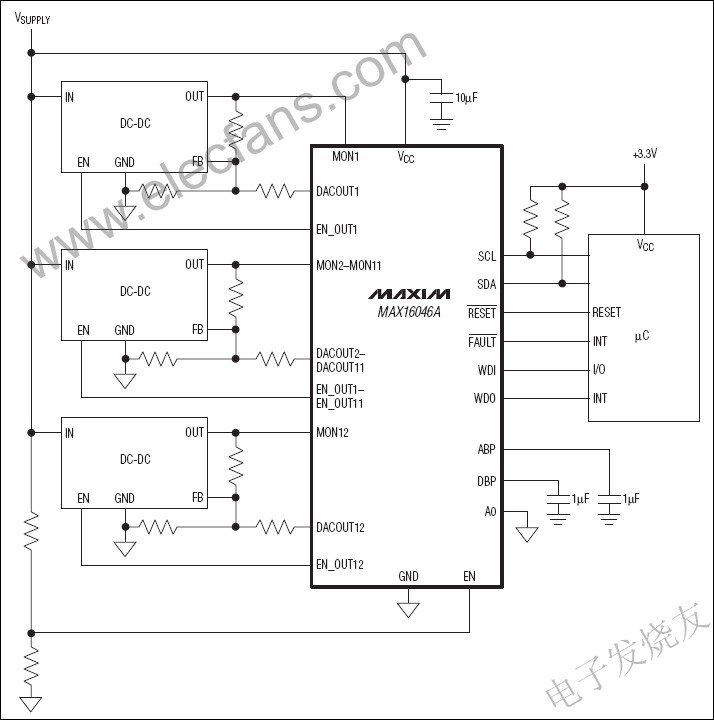

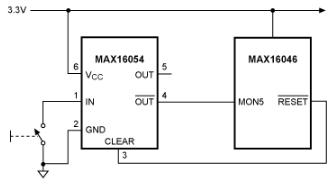

圖2中的部分原理圖顯示了MAX16046在圖1所示電源架構(gòu)中的連接。MAX16046控制每個(gè)電源的使能輸入并監(jiān)視輸出。該器件還控制串聯(lián)調(diào)整 MOSFET,用于保持 3.3V I/O 電源軌。MAX16046的DAC輸出連接到多個(gè)電源的反饋節(jié)點(diǎn),以實(shí)現(xiàn)裕量調(diào)節(jié)功能。

圖2.MAX16046的部分原理圖

圖3給出了MAX16046周圍電路的更詳細(xì)原理圖,包括電源連接和在線編程連接。/SYSTEM_RESET信號(hào)運(yùn)行至MPC8548和Virtex 5的復(fù)位輸入。預(yù)警信號(hào)可以警告MPC8548開始干凈關(guān)斷和軟關(guān)機(jī);關(guān)鍵故障信號(hào)可以運(yùn)行到控制3.3V電源的鎖存器,在關(guān)鍵過(guò)壓事件時(shí)將其關(guān)閉。(FAULT2是完全可編程的,但在此應(yīng)用中設(shè)置為過(guò)壓)。看門狗定時(shí)器輸入WDI連接到MPC8548,以便在MPC16046無(wú)法切換WDI時(shí),MAX8548可以SYSTEM_RESET置位。在制造或原型評(píng)估期間,/MARGINUP# 和/MARGINDN# 運(yùn)行到測(cè)試點(diǎn) TP1 和 TP2,以進(jìn)行裕量調(diào)節(jié)。

圖3.詳細(xì)的MAX16046原理圖

在本例中,在線編程是通過(guò)JTAG連接完成的。SDA和SCL運(yùn)行至MPC8548,因此它可以查詢MAX16046以獲取故障信息或?qū)崟r(shí)電壓測(cè)量。應(yīng)用筆記4285“MAX16046–MAX16049 EEPROM可編程系統(tǒng)管理器的在線編程”詳細(xì)介紹了在線編程。

當(dāng)EN電壓超過(guò)16046.0V (典型值)時(shí),MAX525開始對(duì)電源進(jìn)行排序;當(dāng)電壓降至0.5V (典型值)以下時(shí),它將對(duì)電源進(jìn)行反向排序。至關(guān)重要的是,12V電源的輸出端必須有足夠的大容量電容,以確保反向排序成功完成。門限設(shè)置為11.7V,以提供足夠的儲(chǔ)能電容電壓來(lái)實(shí)現(xiàn)此電壓。也可以通過(guò)SMBus或JTAG控制電源,以實(shí)現(xiàn)軟關(guān)斷應(yīng)用。

與V串聯(lián)的二極管抄送允許電容器在 V抄送在故障條件下為MAX16046供電。故障保存操作需要長(zhǎng)達(dá)204ms的時(shí)間,將故障數(shù)據(jù)寫入MAX16046的非易失性EEPROM。MAX16046數(shù)據(jù)資料中的公式(如下所示)得出的最小電容值為157μF:

上電排序完成后,MAX16046解除SYSTEM_RESET,從而允許處理器和FPGA初始化并開始正常工作。

軟件配置

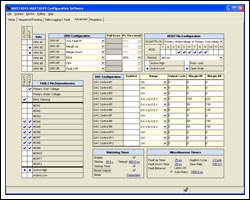

MAX16046組態(tài)軟件提供了一種方便的配置參數(shù)輸入方式,無(wú)需研究寄存器映射或進(jìn)行無(wú)休止的計(jì)算。在我們的電路板中配置MAX16046分幾個(gè)步驟完成。

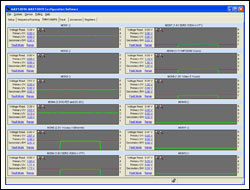

步驟 1 在配置軟件設(shè)置選項(xiàng)卡中輸入電源信息。(請(qǐng)參閱圖 4。)

圖 4.MAX16046配置軟件設(shè)置卡舌,輸入?yún)?shù)。

每個(gè)電源在電子表格樣式的數(shù)據(jù)表中由一行表示。1.8V DDR2 電源是雙輸出電源,因此在該行中添加了一個(gè)“子項(xiàng)”來(lái)表示第二個(gè)監(jiān)控輸入。單擊該行,然后單擊“添加子項(xiàng)”以添加該電源的額外監(jiān)視通道。

欠壓和過(guò)壓直接以百分比形式輸入。點(diǎn)擊寫入寄存器后,軟件自動(dòng)計(jì)算要加載到MAX16046中的寄存器值。

裕量參數(shù)是使用余量計(jì)算器輸入的,如圖 5 所示。裕量計(jì)算器將自動(dòng)計(jì)算電壓范圍,給定電源的參考電壓和三個(gè)電阻值;它將確定裕量增大電壓和裕量減小電壓所需的寄存器值。

圖5.帶3.3V電源軌參數(shù)的裕量計(jì)算器。

步驟 2

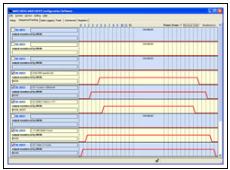

啟動(dòng)排序選項(xiàng)卡,以便確定序列順序。圖6顯示了我們電路的序列順序。使用鼠標(biāo)光標(biāo)將電壓軌拖動(dòng)到適當(dāng)?shù)捻樞颉C總€(gè)邊欄之間的延遲是通過(guò)單擊頂行帶下劃線的藍(lán)色鏈接來(lái)設(shè)置的。延遲根據(jù)表2設(shè)定。

表 2.插槽延遲

| 槽 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 延遲 | 12.5毫秒 | 25毫秒 | 25毫秒 | 25毫秒 | 12.5毫秒 | 12.5毫秒 | 20微秒 | 20微秒 | 20微秒 | 20微秒 | 20微秒 | 20微秒 |

圖 6.序列配置。

步驟 3

啟動(dòng)雜項(xiàng)選項(xiàng)卡以設(shè)置可編程故障輸出、看門狗定時(shí)器和各種其他參數(shù)。圖 7 顯示了雜項(xiàng)參數(shù)的選項(xiàng)卡。

圖 7.其他配置參數(shù)。

GPIO1 的任何故障 PP 配置將導(dǎo)致它在發(fā)生排序錯(cuò)誤或 FAULT1 或 FAULT2 條件為真時(shí)斷言(推送拉取)。該信號(hào)被發(fā)送到MPC8548輸入,該輸入表示發(fā)生了故障情況。MPC8548可以通過(guò)SMBus查詢MAX16046以確定故障原因。

GPIO2 的故障 6 PP 配置將導(dǎo)致它在發(fā)生嚴(yán)重過(guò)壓故障時(shí)置位(推挽)。GPIO6可以連接到切斷電路板電源以防止損壞的電路。GPIO6 將根據(jù) FAULT2 列中的復(fù)選框進(jìn)行斷言。

GPIO4配置為閉環(huán)跟蹤(INS4),因?yàn)樵撏ǖ烙糜谧钄?.3V IO軌。95% 的電源良好閾值意味著當(dāng)串聯(lián)調(diào)整 MOSFET 源上的電壓超過(guò)漏極電壓的 95% 時(shí),該電源軌將變?yōu)殡娫淳途w。

復(fù)位超時(shí)設(shè)置為 200ms。在所有電源軌達(dá)到電源就緒狀態(tài)并且 200ms 過(guò)后,SYSTEM_RESET將變?yōu)楦唠娖剑固幚砥骱?FPGA 免于復(fù)位。

看門狗定時(shí)器配置為SYSTEM_RESET解除置言后的 25.6 秒初始啟動(dòng)延遲。此延遲使MPC8548有時(shí)間在切換WDI之前完成啟動(dòng)例程。相關(guān)意味著初始啟動(dòng)延遲從上電序列結(jié)束時(shí)開始測(cè)量。

其他定時(shí)器參數(shù)包括 3.3V IO (400V/s) 的壓擺率控制;1600ms自動(dòng)重試延遲,使MAX16046在上電序列嘗試失敗后等待1.6秒,然后再試一次;以及故障啟動(dòng)定時(shí)器/故障下垂定時(shí)器,允許每個(gè)電源軌在反向排序期間在閾值內(nèi)上升或下降 25ms。

設(shè)置完所有配置參數(shù)后,可以將數(shù)據(jù)保存到文件中以進(jìn)行批量編程或保存到版本控制系統(tǒng)中。MAX16046組態(tài)軟件可以為JTAG編程工具生成SVF文件。

將配置文件加載到組裝的目標(biāo)板后,可以使用配置軟件的監(jiān)控選項(xiàng)卡來(lái)幫助進(jìn)行原型評(píng)估。監(jiān)視選項(xiàng)卡使用MAX16046的ADC提供每個(gè)電源的供電軌電壓的實(shí)時(shí)圖表。圖形的采樣速率太慢,無(wú)法觀察序列順序,但可以檢查電壓。

圖 8.顯示排序的電壓監(jiān)控屏幕。

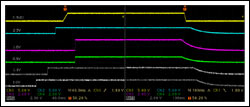

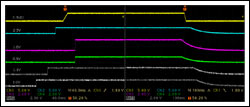

圖8顯示了我們電路中電壓的屏幕截圖。圖9顯示了一張標(biāo)有電壓軌的復(fù)合示波器照片。閉環(huán)跟蹤壓擺率可在3.3V IO電源軌上觀察到。

圖 9.測(cè)序范圍照片。

可以檢查示波器照片,并與MAX16046配置軟件配置的順序和時(shí)序進(jìn)行比較;它也可以與原始測(cè)序要求相匹配。在這種情況下,測(cè)量的序列順序與上一節(jié)規(guī)范中給出的要求相匹配。

裕量可以通過(guò)將兩個(gè)測(cè)試點(diǎn)TP1和TP2中的任何一個(gè)接地來(lái)評(píng)估,這會(huì)導(dǎo)致所有電源上升和下降到預(yù)定值。電源軌電壓可以使用MAX16046或單獨(dú)的電壓表測(cè)量。

結(jié)論

MAX16046提供了一種在復(fù)雜的多電源系統(tǒng)中實(shí)現(xiàn)排序、裕量調(diào)節(jié)和監(jiān)視的簡(jiǎn)單方法。MAX16046配置軟件簡(jiǎn)化了容差和順序的配置。

審核編輯:郭婷

-

FPGA

+關(guān)注

關(guān)注

1626文章

21667瀏覽量

601854 -

asic

+關(guān)注

關(guān)注

34文章

1194瀏覽量

120327 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7452瀏覽量

163606 -

cpu

+關(guān)注

關(guān)注

68文章

10825瀏覽量

211150

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

一周推薦:Analog Devices數(shù)字電源系統(tǒng)管理 (PSM) 器件

MAX16046/MAX16048 pdf

系統(tǒng)管理IC滿足多電壓系統(tǒng)的監(jiān)視和排序要求

系統(tǒng)管理IC滿足多電壓系統(tǒng)的監(jiān)視和排序要求

系統(tǒng)管理IC滿足多電壓系統(tǒng)的監(jiān)視和排序要求

系統(tǒng)管理IC滿足多電壓系統(tǒng)的監(jiān)視和排序要求

系統(tǒng)管理的詳細(xì)設(shè)計(jì)

MAX16046,MAX16046A, MAX16048A中

MAX16046–MAX16049 EEPROM可編程系統(tǒng)管

MAX16046–MAX16049 EEPROM可編程系統(tǒng)管

Sequencing with the MAX16046 S

利用MAX16046系統(tǒng)管理IC進(jìn)行排序

MAX16046A/MAX16048A EEPROM可配置系

為MAX16046 EEPROM可編程系統(tǒng)管理器添加自動(dòng)重啟功能

MAX16046–MAX16049 EEPROM可編程系統(tǒng)管理器的在線編程

使用MAX16046系統(tǒng)管理IC進(jìn)行排序

使用MAX16046系統(tǒng)管理IC進(jìn)行排序

評(píng)論