一、硬件說明

二、特性

三、管腳說明

四、驅(qū)動安裝

五、JTAG與UART共用

版本說明

| v1 |

(1)添加了支持UART的版本說明。 (2)添加了對JTAG接口用作UART的說明。 |

一、硬件說明

USB接口 :方口線

USB線長度 :1m

杜邦線長 :15cm

說明:該下載器把SPI與JTAG管腳進行了分開處理。 鑒于JTAG使用較多,SPI使用較少,所以把JTAG放在插座上側(cè)。

二、特性

(1)支持JTAG

(2)支持SPI,

(3)SPI接口CCK和CDI0可以用作串口(后面有更詳細說明)。

(4)電壓范圍支持1.5V~5V. 注意必須要接VCC.

三、管腳說明

(1)一般來說JTGA下載只要連接VCC,TCK,TDI,TMS,TDO和GND 共6個腳即可。

如果是T20F225或者T4,T8等器件要連接CRST_N。

(2)如果下載flash,一般連接VCC,CCK,CDI0,CDI1,SS_N和GND即可。 HOLD引腳可以用于連接FPGA復(fù)位引腳,防止FPGA對flash操作而影響SPI下載。

(3)兩個VCC是連接在一起的,由于VCC驅(qū)動內(nèi)部電平轉(zhuǎn)換芯片,所以VCC必須連接。

四、驅(qū)動安裝

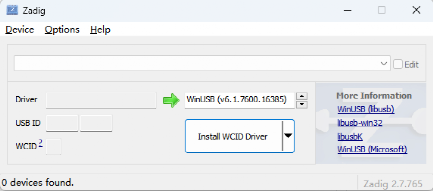

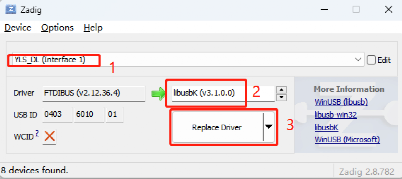

(1)打開zadig(zadig下載鏈接https://zadig.akeo.ie)

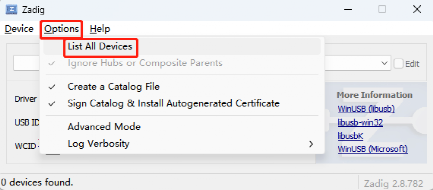

(2)選擇選項 ->列出所有設(shè)備

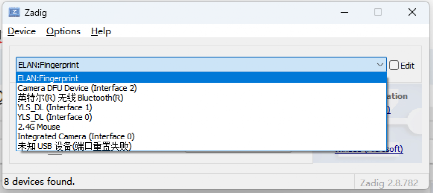

(3)然后在下拉框中可以找到Y(jié)LS_DL(interface 0)和YLS_DL(interface 1)。 這就下載器名稱,分別對應(yīng)SPI和JTAG.

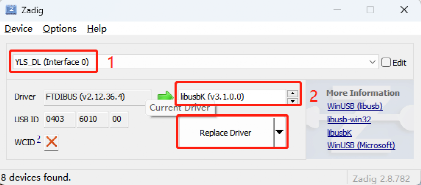

(4)選擇YLS_DL(interface 0),然后Drive替換項選擇libusbK(版本可能有差異,不用管)。 最后選擇Replace Driver

(5)然后按照步驟4,重新安裝YLS_DL(Interface 1)的驅(qū)動。

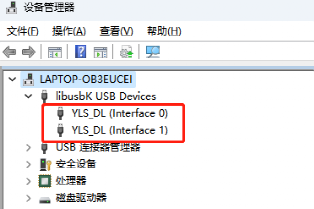

(6)安裝完成之后在設(shè)備管理器中可以看到。

(7)這里如果連接了上下載器,打開programmer可以看到讀取的下載器信息和JTAG ID如下。 器件ID根據(jù)易靈思不同系列會有所不同。

五、JTAG與UART共用

提示:該功能要求Efinity版本在 2022.2.322.5.7版本及以后。

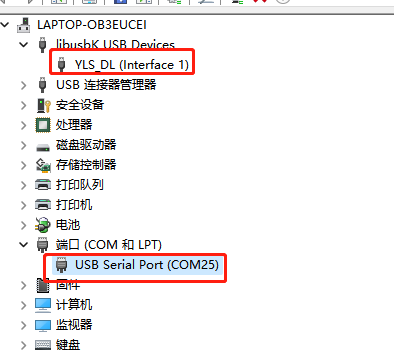

目前易靈思已經(jīng)支持JTAG與UART共用。按圖中,只安裝YLS_DL(interface 1)而不安裝Interface 0的驅(qū)動,會在端口中找到USB Serial Port(COM25),不同電腦的COM口號不完全一樣。這時就可以用該COM口作為串口。

其中CCK和CDI0分別對應(yīng)UART的RXD和TXD.

另外要注意的是VCC必須要連接,驅(qū)動內(nèi)部的電平轉(zhuǎn)換芯片,否則無法工作,另外由于JTAG與SPI的VCC是連接在一起的,所以要注意UART的電平也是由VCC決定,如果VCC連接1.8V,那UART也只能連接1.8V的IO。

當然如果只安裝SPI的驅(qū)動也是可以用JTAG接口當作串口的,TCK和TDI對應(yīng)UART的RXD和TXD.

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1626文章

21667瀏覽量

601850 -

usb

+關(guān)注

關(guān)注

60文章

7896瀏覽量

263989 -

uart

+關(guān)注

關(guān)注

22文章

1227瀏覽量

101173 -

下載器

+關(guān)注

關(guān)注

1文章

62瀏覽量

12806 -

易靈思

+關(guān)注

關(guān)注

5文章

45瀏覽量

4852

原文標題:易靈思FPGA下載器-v1

文章出處:【微信號:gh_ea2445df5d2a,微信公眾號:FPGA及視頻處理】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

易靈思(Elitestek)FPGA編程器功能特點及驅(qū)動安裝方法

玩轉(zhuǎn)FPGA 賽靈思(xilinx)FPGA設(shè)計大賽獲獎名單!!!

FPGA是用altera多還是賽靈思的多呢

易靈思推Trion Titanium FPGA,采用 “Quantum? 計算架構(gòu)”

易靈思FPGA產(chǎn)品幫助安防領(lǐng)域創(chuàng)新和突破

易靈思FPGA軟件更新的節(jié)奏,也許能磨出一個好產(chǎn)品

用賽靈思FPGA加速機器學(xué)習(xí)推斷

易靈思FPGA下載器安裝方法

易靈思FPGA下載器安裝方法

評論