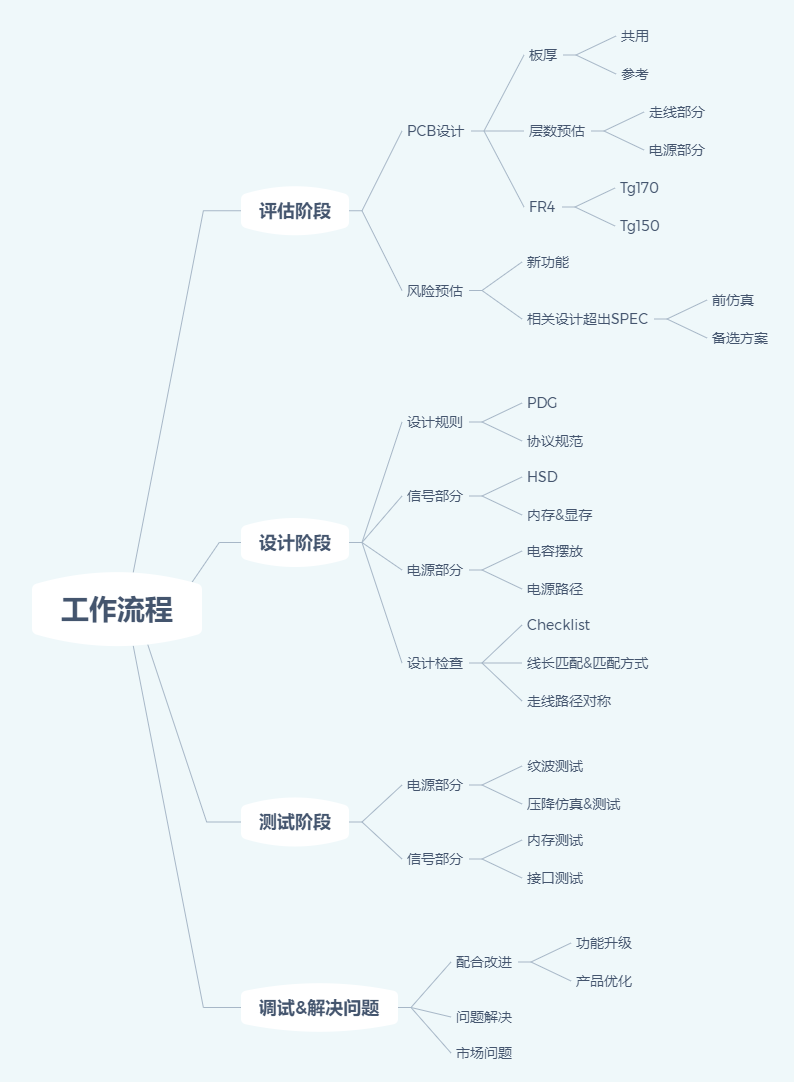

關(guān)于設(shè)計(jì)過程中,SI信號(hào)完整性工程師工作的流程如下:

01

評(píng)估階段

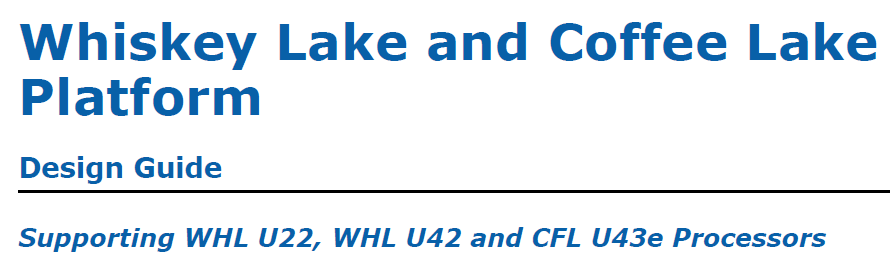

Intel & AMD 等芯片廠商每年會(huì)發(fā)布一款新平臺(tái)Design guide,各大生產(chǎn)商會(huì)在接下來的6~9個(gè)月,或者更快的時(shí)間內(nèi)設(shè)計(jì)出相關(guān)產(chǎn)品,搶占市場(chǎng)。針對(duì)消費(fèi)類的產(chǎn)品,唯快不破!

離開Samsung前做的最后的一個(gè)平臺(tái)

MRT市場(chǎng)會(huì)根據(jù)市場(chǎng)調(diào)研以及最新平臺(tái)的新功能,給到研發(fā)中心一個(gè)設(shè)計(jì)需求及相關(guān)高低配置。消費(fèi)類產(chǎn)品一般有高低價(jià)位,針對(duì)PC,高低配的差別,除了存儲(chǔ)容量,更大的體現(xiàn)于獨(dú)立顯卡和集成顯卡。當(dāng)然,消費(fèi)者關(guān)注的外表材質(zhì),也會(huì)因?yàn)榕渲枚兴煌?/p>

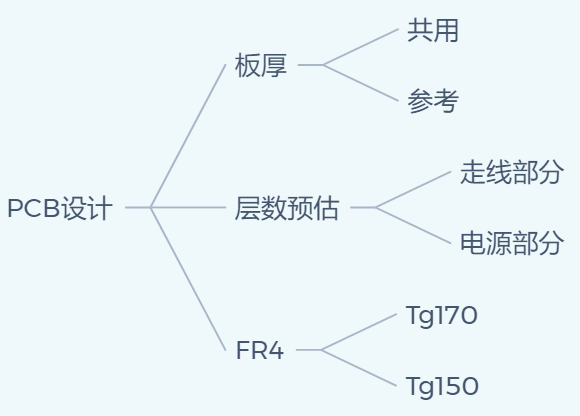

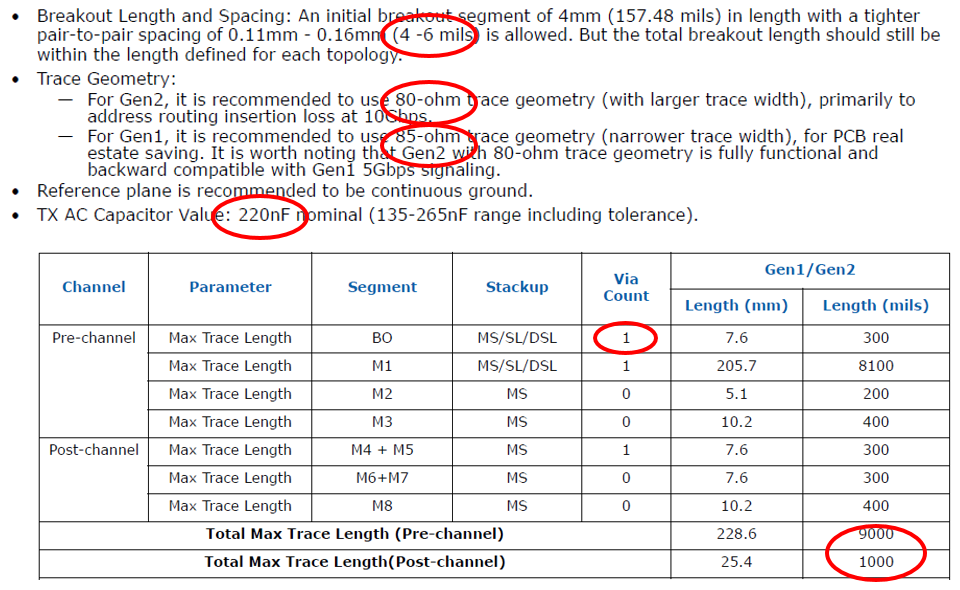

機(jī)構(gòu)工程師會(huì)根據(jù)平臺(tái)資料和先行評(píng)估,給到我們一個(gè)PCB板的厚度范圍。如果這個(gè)范圍在先期的平臺(tái)中有使用過的機(jī)種符合,我們會(huì)盡量共用之前的PCB板厚和疊層,共用的主要好處是在PCB生產(chǎn)過程中的阻抗管控,特別是回板周期的保證。

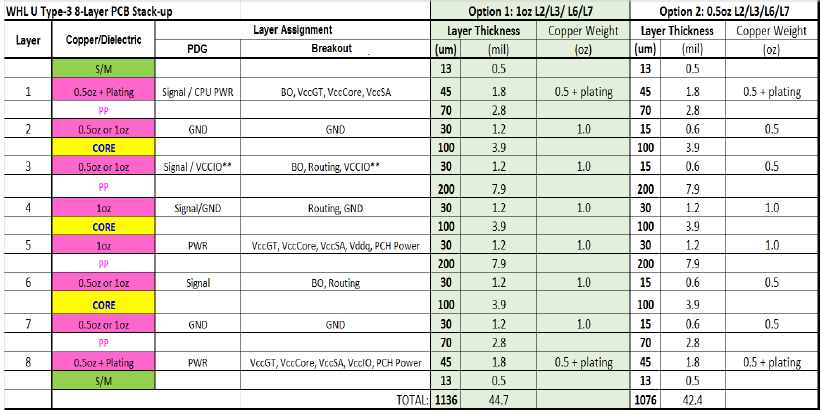

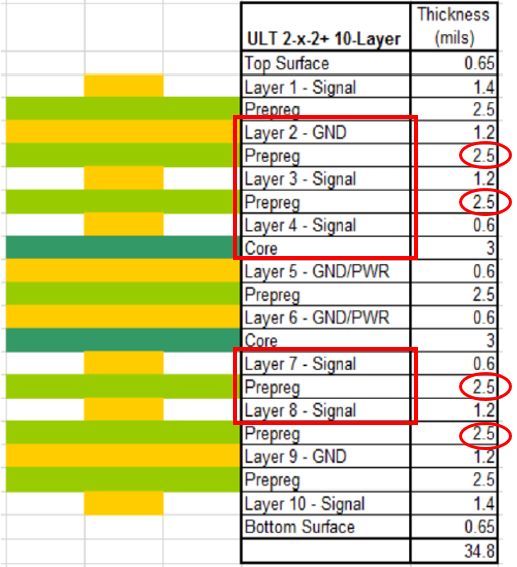

如果不能共用,我們會(huì)參考平臺(tái)設(shè)計(jì)規(guī)范中給出的疊層,下圖為8-Layer參考疊層:

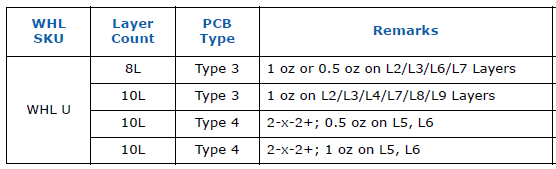

當(dāng)然,平臺(tái)也會(huì)給出不同板厚不同疊層的多種選擇:

這樣,各家廠商會(huì)根據(jù)自身產(chǎn)品的定位和配置來做出選擇。

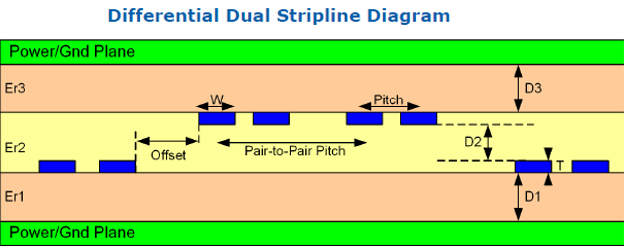

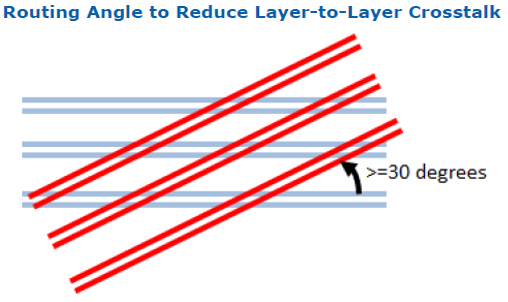

需要指出的是,不同于高速產(chǎn)品(服務(wù)器&交換機(jī)等),消費(fèi)類產(chǎn)品特別是Notebook是走線密度特別大的,經(jīng)常會(huì)走雙帶線。針對(duì)上下層的串?dāng)_,只是給出走線Overlap建議,根本沒有提到返回路徑完整性。

30度的建議看起來容易,其實(shí)Layout操作起來還是很麻煩的。針對(duì)Overlap重復(fù)度,之前還做過相關(guān)設(shè)計(jì)經(jīng)驗(yàn)總結(jié),現(xiàn)在應(yīng)該不適用了。

從WHL平臺(tái)開始,市面上出現(xiàn)了很多游戲本和超極本,為了追求產(chǎn)品的超薄,需要管控PCB板厚,也就需要控制介質(zhì)厚度,沒有所謂的遠(yuǎn)端參考,更多地需要對(duì)完整地平面做各種切割來保證電源完整性。

等到轉(zhuǎn)換賽道,從事更高速率的產(chǎn)品設(shè)計(jì)中,這些操作是不敢想象的。產(chǎn)品的不同,側(cè)重點(diǎn)也有所不同,認(rèn)知也有所不同,這正是一葉障目。

走線部分:

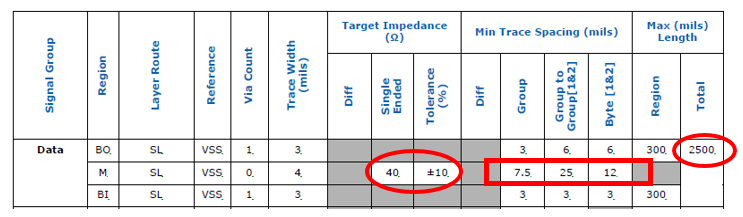

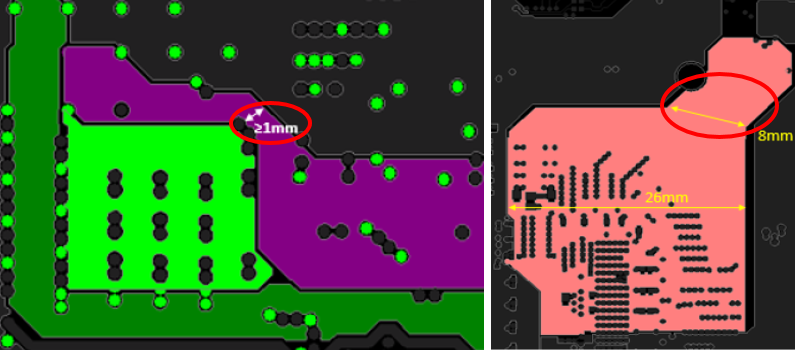

根據(jù)阻抗軟件算出差分阻抗的線寬線距,內(nèi)存和顯存單端阻抗的線寬。然后根據(jù)走線guide來評(píng)估走線范圍是否滿足走線間距及相互間距的要求。其實(shí)也就是滿足Inter pair& Intra pair,至于其他雜線間距的要求都是可調(diào)的。

內(nèi)存和顯存走線也按照這種方式方法進(jìn)行預(yù)估,其實(shí)內(nèi)存和顯卡的走線相對(duì)固定,只是可能因?yàn)榕渲貌煌呔€數(shù)量(DQ&CMD)的變化而增加層數(shù)而已。

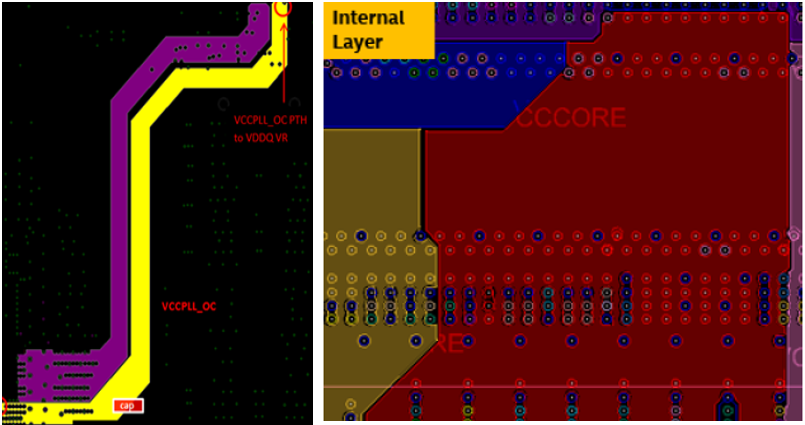

電源部分:

對(duì)各部分電源進(jìn)行簡(jiǎn)單分層,重點(diǎn)關(guān)注電流負(fù)載需求大的CORE電,需要考慮不同層面的結(jié)合與轉(zhuǎn)換,來保證其電源完整性。

上面的步驟都是前期布局預(yù)估,布線層數(shù)還沒完全確定。這時(shí)候需要Layout工程師來做相關(guān)工作:高速信號(hào)狹窄部分走線;內(nèi)存和顯存擺放大器件;鋪選電源路徑。

通過這些工作,來最終確定PCB板層數(shù)。根據(jù)確定的層數(shù),我們最終確定板厚和疊層。

至于板材的選擇,因?yàn)橄M(fèi)類產(chǎn)品成本的限制,一般不會(huì)有損耗要求,只會(huì)給出FR4 的Tg,讓板廠自行決定選材,印象中,有使用過TU768。不管板廠選擇什么板材,必須進(jìn)行相關(guān)阻抗的管控,特別是針對(duì)內(nèi)存的單端線阻抗管控,內(nèi)存相關(guān)的Margin 測(cè)試管控比較嚴(yán)格。

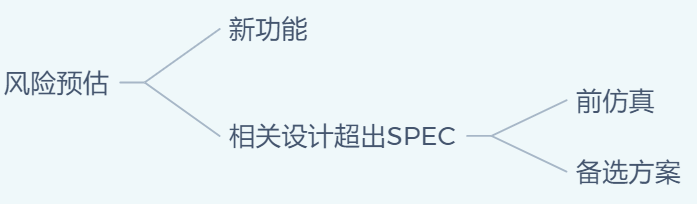

二、風(fēng)險(xiǎn)預(yù)估

各個(gè)工種會(huì)根據(jù)自身的設(shè)計(jì)規(guī)范給出風(fēng)險(xiǎn)預(yù)警。針對(duì)信號(hào)完整性這邊,無非就是板型的限制造成信號(hào)線長(zhǎng)不符合要求,走線空間不符合要求等等。一般新平臺(tái)的新功能,因?yàn)闆]有設(shè)計(jì)經(jīng)驗(yàn),比如WHL Type C 的充電功能、Thunderbolt功能等都會(huì)預(yù)警。如果時(shí)間上來得及,會(huì)對(duì)一些風(fēng)險(xiǎn)點(diǎn)進(jìn)行前仿真,如線長(zhǎng)超出SPEC。

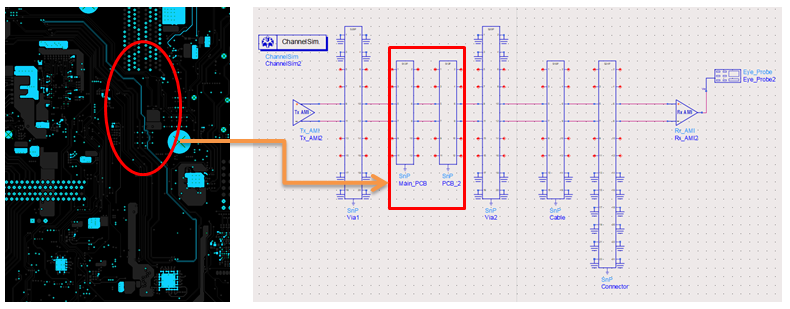

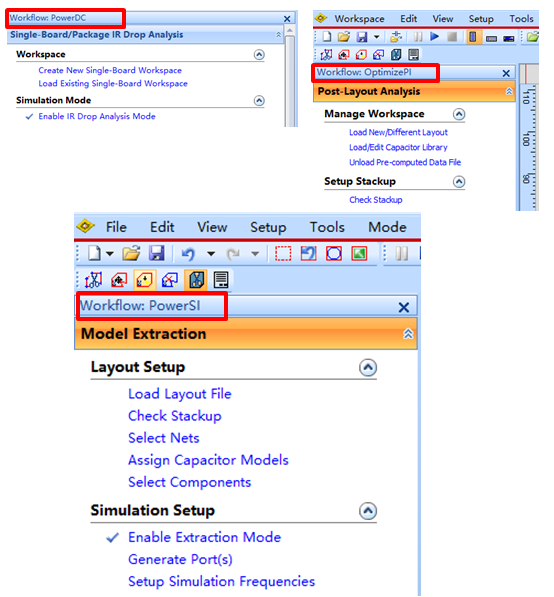

比如,設(shè)計(jì)中有PCIe信號(hào)超過SPEC或者經(jīng)驗(yàn)值。Layout工程師先行設(shè)計(jì)出相關(guān)部分的走線,然后用PowerSI提取出S參數(shù),用ADS模擬鏈路搭建,仿真出結(jié)果。

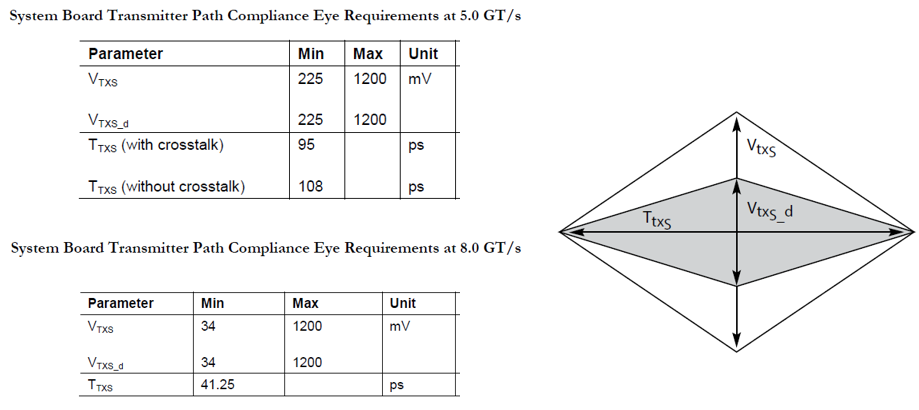

將得到的眼圖及相關(guān)指標(biāo),與協(xié)議規(guī)范的標(biāo)準(zhǔn)或者模板進(jìn)行對(duì)比,來衡量是否符合標(biāo)準(zhǔn)。不符合的情況下,評(píng)估風(fēng)險(xiǎn)級(jí)別。

針對(duì)相關(guān)的風(fēng)險(xiǎn)點(diǎn),給出備選方案。

02

設(shè)計(jì)階段

進(jìn)入設(shè)計(jì)階段,需要輸出詳細(xì)的設(shè)計(jì)規(guī)則給到Layout 工程師。設(shè)計(jì)細(xì)則有很多,很多公司也大同小異,每個(gè)公司也會(huì)有相應(yīng)的文檔格式和輸出。

一、信號(hào)部分

這部分我們重點(diǎn)關(guān)注的是高速線、內(nèi)存&顯存的部分:

高速線(PCIe,USB,HDMI,SATA)差分阻抗線寬線距,組內(nèi)&組間距離(Inter pair &Intra pair)。

內(nèi)存&顯卡的阻抗(40?&50?)及組內(nèi)&組間距離(16mil);

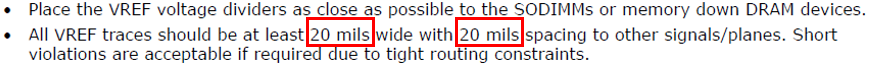

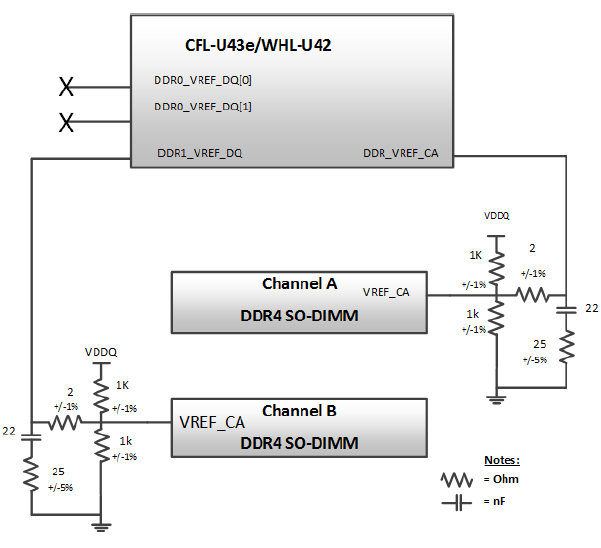

Reference Voltage(VREF)

除了上面重點(diǎn)部分,其他信號(hào)走線的規(guī)則,比如電源部分與信號(hào)線的距離以及一些其他相關(guān)規(guī)定,這里就不一一列舉了。

二、電源部分

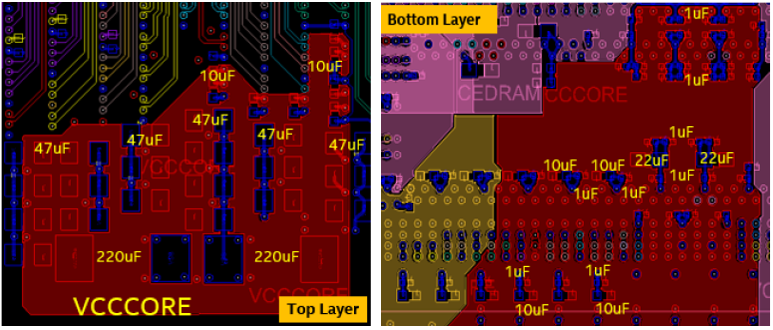

電源部分我們重點(diǎn)關(guān)注兩點(diǎn):電容擺放&電源路徑。

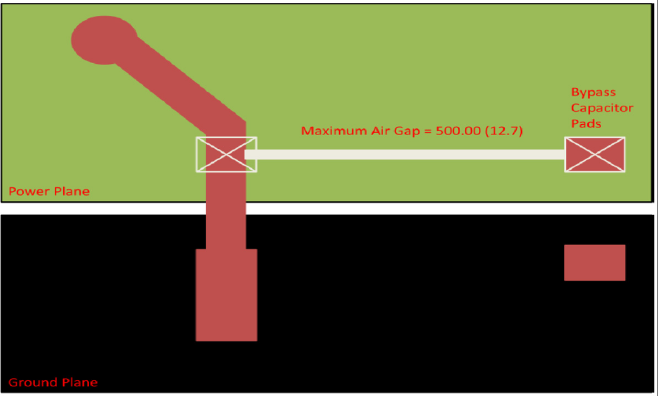

電容擺放:

我們需要先確定去耦電容的種類和大體數(shù)量,然后框選去耦電容的擺放范圍。擺放原則一般遵循去耦半徑范圍大小來擺放。小電容靠前,大電容靠后,有空間擺放的時(shí)候,也可以考慮部分大電容靠前,來防止電壓過沖保護(hù)。這里前后的概念是基于終端用電Pin區(qū)域來說的。

去耦電容的數(shù)量部分,在后期產(chǎn)品量產(chǎn)后,會(huì)對(duì)其進(jìn)行優(yōu)化。減少電容數(shù)量,來降低產(chǎn)品成本。電容數(shù)量的減小,可以通過電容優(yōu)化仿真和結(jié)合后期電源紋波測(cè)試的margin來評(píng)估。

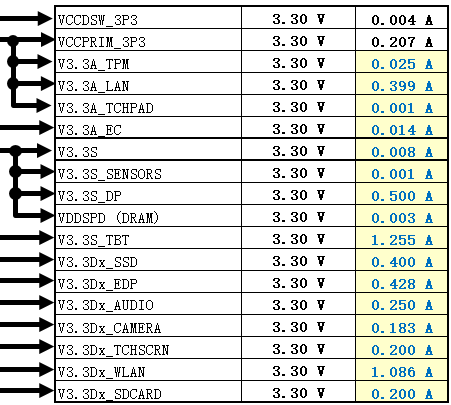

電源路徑:

先期我們會(huì)根據(jù)相關(guān)設(shè)計(jì)規(guī)范文件,找出各部分電源的最大承載電源,根據(jù)承載電流做出電源樹(Power Tree),來評(píng)估和確定主次路徑電流大小。

根據(jù)電源樹,來分配各部分電源大體的主次路徑。協(xié)調(diào)各層各部分電源的鋪墊方式及大小。一般按40mil/1A的電源來預(yù)估電源Shape的寬度。針對(duì)有些電的負(fù)載比較,一般考慮在內(nèi)層給于補(bǔ)充,來保證其負(fù)載,同時(shí)在轉(zhuǎn)換電源層的時(shí)候,要注意打孔的數(shù)量。銅皮1oz,Via10過孔通流在1A預(yù)估。

這里需要特別強(qiáng)調(diào)的是:整個(gè)電源路徑,一定要關(guān)注其狹窄部分,這部分特別影響通流能力。比如5V的電,跟后期測(cè)試相關(guān)節(jié)后的IR Drop有很大的關(guān)系。

三、設(shè)計(jì)檢查

PCB Gerber前檢查的條目也很多,每個(gè)公司也會(huì)有自己的Checklist。信號(hào)方面主要是HSD相關(guān)高速線的檢查。

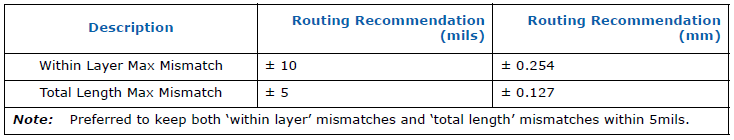

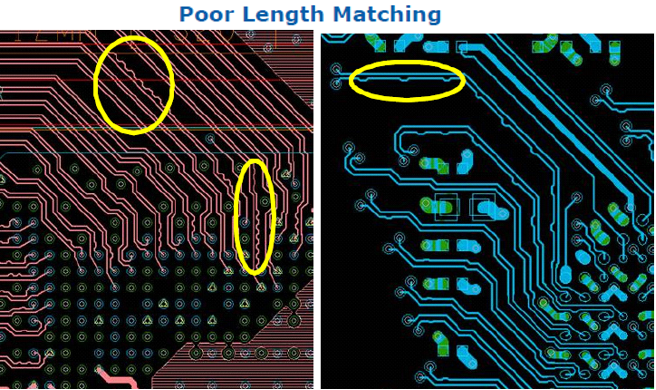

線長(zhǎng)匹配檢查:

我們會(huì)輸出一個(gè)等長(zhǎng)表格,來確保整個(gè)高速線的匹配。

匹配方式:

會(huì)給出參考線長(zhǎng)匹配方式及一些差的匹配方式:

路徑檢查:

保證走線路徑相互對(duì)稱,轉(zhuǎn)換過孔處有回流地孔,遠(yuǎn)離干擾源(如電源)等。

03

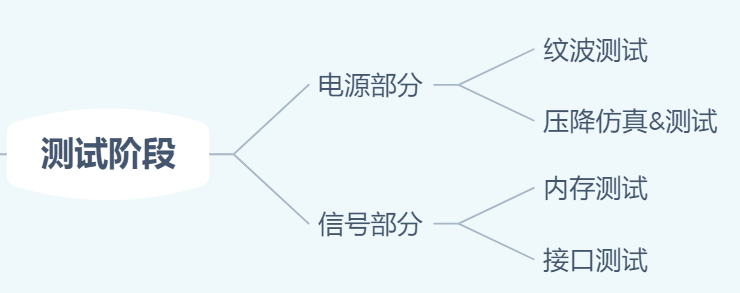

測(cè)試階段

PCB Gerber之后,一般在10~15天回板。這段時(shí)間,需要整理相關(guān)資料,準(zhǔn)備測(cè)試階段的工作。

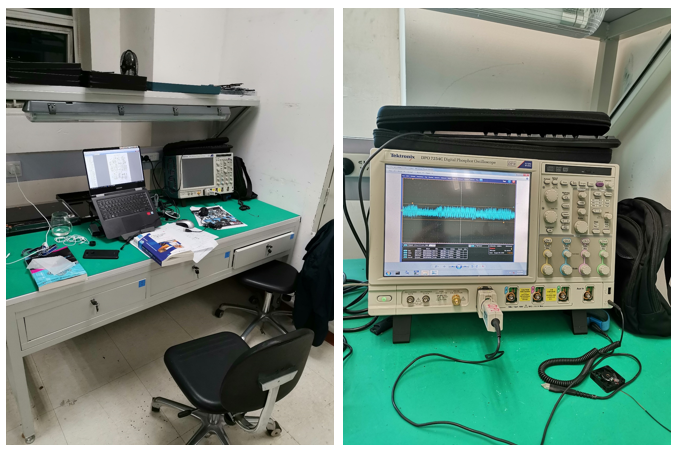

因?yàn)橄M(fèi)類產(chǎn)品的時(shí)效性,測(cè)試的時(shí)間一般在10~15天。測(cè)試的Item很多,時(shí)間關(guān)系,一般只測(cè)高配版本。一般這段時(shí)間會(huì)一直耗在實(shí)驗(yàn)室,直到測(cè)試&問題解決才能出關(guān)坐回辦公室。

一、電源部分

電源測(cè)試的Item很多,這里只講講其中幾個(gè)。

紋波測(cè)試:

電源紋波測(cè)試量很大,需要讓測(cè)試主板在高性能狀態(tài),一般會(huì)運(yùn)行相關(guān)測(cè)試軟件,然后用示波器點(diǎn)測(cè)終端的耦合電容。同一個(gè)電不同容值,不同的電不同容值,都要點(diǎn)測(cè)。

紋波測(cè)試重點(diǎn)關(guān)注Pk-Pk值,終端的標(biāo)準(zhǔn)是+/-5%,源端+/-3%的標(biāo)準(zhǔn),測(cè)試標(biāo)準(zhǔn)因產(chǎn)品而定。紋波測(cè)試的作用,除了終端電源的完整性,也為后期量產(chǎn)后,機(jī)種降成本(Costdown)設(shè)計(jì)提供測(cè)試數(shù)據(jù)。

如果有些電測(cè)試有問題,就得需要從源端、電源路徑、終端耦合電容的擺放等多方面找出問題,然后解決。

檢查電容擺放位置(0.5 inches)之內(nèi)

降低成本:

量產(chǎn)后,可以結(jié)合OptimizePI,降低機(jī)種成本。通過OptimizePI仿真,可以優(yōu)化減少耦合電容種類和數(shù)量。再根據(jù)紋波實(shí)測(cè)的結(jié)果,給出優(yōu)化的結(jié)果。可以的話,通過相關(guān)的PCB測(cè)試板重工認(rèn)證。不知道現(xiàn)在的版本有沒有更新優(yōu)化的版本,能夠給出優(yōu)化后電容擺放的范圍。

壓降測(cè)試:

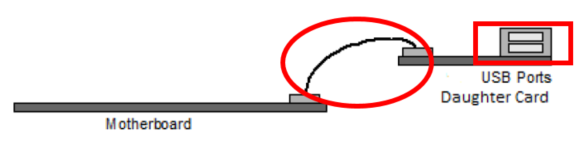

壓降測(cè)試的原因是PDN有阻抗,負(fù)載電流從源端到終端,會(huì)有壓降的產(chǎn)生。以USB3.0為例,終端的電壓值需要≥4.75V,才能保證終端設(shè)備的識(shí)別。特別是小板上的USB3.0接口。印象中,開發(fā)過一款產(chǎn)品,賣點(diǎn)就是小板上有USB3.0接口,因?yàn)橐?jīng)過FPC Cable,接口的壓降問題就搞了很長(zhǎng)時(shí)間。

IR Drop 壓降測(cè)試除了可以用軟件Power DC仿真跑出電壓值,還可以使用測(cè)試夾具抽載(USB3.0&1A,USB2.0&500 mA),測(cè)出終端的電壓值,看其是否符合SPEC。

針對(duì)Drop風(fēng)險(xiǎn)比較大的鏈路,PowerDC搭建仿真,根據(jù)仿真結(jié)果,給出風(fēng)險(xiǎn)預(yù)估。但是這種,只能針對(duì)主板帶終端接口的鏈路。PowerDC搭建仿真,是沒辦法導(dǎo)入FPC Cable模型,來預(yù)估帶Cable 的壓降,不知道現(xiàn)在版本,可不可以導(dǎo)入使用。

PI 仿真三大件

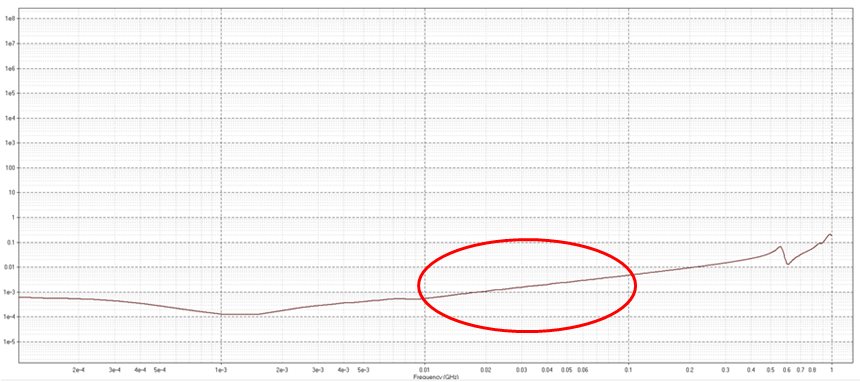

PowerSI 提取AC PDN 電阻,不同于高頻段的噪聲由芯片過濾, PCB板耦合電容作用于兆級(jí)別。

二、信號(hào)部分

信號(hào)的測(cè)試不僅僅是高速信號(hào)相關(guān)測(cè)試,時(shí)鐘的部分也要進(jìn)行測(cè)試(保持時(shí)間,建立時(shí)間等)。這里只講印象比較深刻的幾個(gè)。

內(nèi)存測(cè)試:

一般默認(rèn)VREF的電為System Memory Voltage一半,比如DDR4是1.2V,即為600 mV。測(cè)試方法:將分壓電阻拿掉,用外部Power Supply 對(duì)其供電,以600 mV為基準(zhǔn),上下調(diào)節(jié)電壓值,同時(shí)運(yùn)行Memory Stress Test。一般測(cè)試時(shí)間≥2H。一直降低或提高測(cè)試值,直到測(cè)試Fail。此時(shí)測(cè)試值和600 mV的差值即可認(rèn)為VREF Margin。

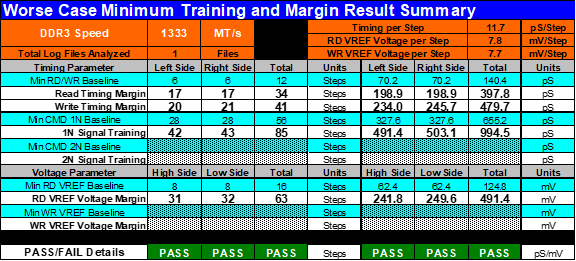

也可以通過Intel 給的關(guān)于DDR測(cè)試軟體工具RMT(Rank Margin Tool) 。BIOS打開Debug port,測(cè)試軟件通過修改內(nèi)部設(shè)置, 讓其開機(jī)時(shí)自動(dòng)運(yùn)行Training程序, 同時(shí)通過Debug Port輸出Training的結(jié)果,從而得到Memory Margin。如下圖,所得到的結(jié)果包含Write/Read Timing Margin,ADD/CMD Timing Margin等信息。也會(huì)對(duì)其結(jié)果做出是否PASS的判斷。關(guān)于RMT測(cè)試的詳細(xì)內(nèi)容,可以參考Intel參考文檔。

DDR3的測(cè)試結(jié)果圖,印象中Timing Margin 的最小值是14

至于其他的點(diǎn)測(cè)就不一一列舉了。印象中,最痛苦的測(cè)試:用兩個(gè)7240測(cè)VCM。這個(gè)測(cè)試必須兩個(gè)人,一個(gè)人抓波形,一個(gè)人兩只手各拿一個(gè)7240探頭。先抓好波形,還要Count 200以上,這段時(shí)間手不能動(dòng),必須保持住。一般測(cè)下來,手都快廢了。

接口方面的測(cè)試就比較粗暴和直接。上了測(cè)試夾具就自動(dòng)跑測(cè)試程序。

接口測(cè)試:

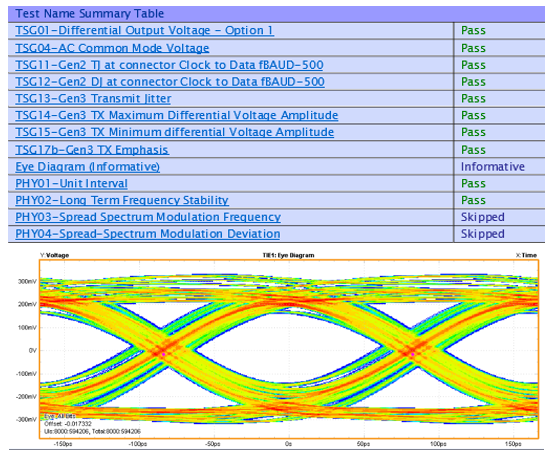

USB3.0,PCIe2.0&3.0等接口一致性測(cè)試,一般是對(duì)發(fā)送信號(hào)進(jìn)行質(zhì)量測(cè)試,一般看眼圖相關(guān)指標(biāo)。

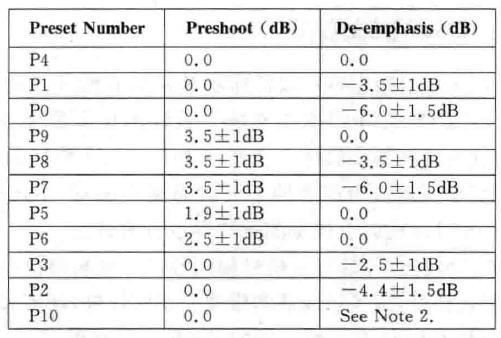

主板的BIOS會(huì)設(shè)定一個(gè)默認(rèn)值,這個(gè)默認(rèn)值可能是經(jīng)驗(yàn)值,也可能是設(shè)計(jì)規(guī)范根據(jù)線長(zhǎng)范圍給出的一個(gè)參考值,如果測(cè)試眼圖顯示Fail,會(huì)通過修改發(fā)送端的預(yù)加重或者是接收端EQ(均衡)參數(shù),來改善眼圖質(zhì)量,讓其滿足相關(guān)協(xié)議規(guī)范測(cè)試標(biāo)準(zhǔn)。

根據(jù)測(cè)試結(jié)果,選擇一個(gè)設(shè)置值,BIOS工程師將其設(shè)定,供新的版本使用。

PCIE3.0預(yù)加重的組合

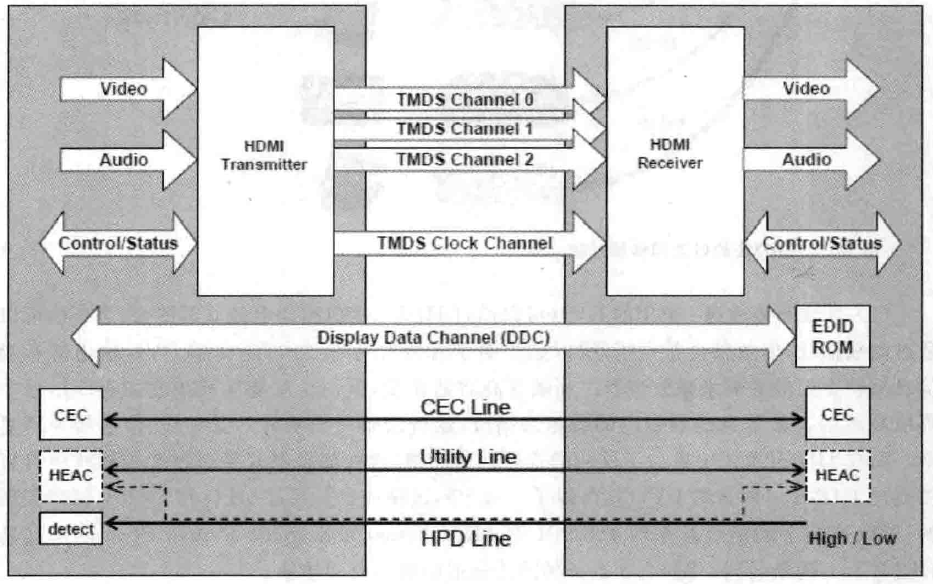

HDMI

不同于其他接口,想講一下HDMI接口,也可能是現(xiàn)有的工作對(duì)這個(gè)接口的關(guān)注越來越少了。現(xiàn)有顯示產(chǎn)品都支持HDMI接口,HDMI接口的普及度和重視程度在消費(fèi)類產(chǎn)品中也越來越高。

記得當(dāng)初有人還整理了一份HDMI接口各種分辨率及對(duì)應(yīng)各種幀頻。后來有的顯示產(chǎn)品號(hào)稱支持4K,一看支持的最大幀頻,就默默走開了。

當(dāng)時(shí)1.4標(biāo)準(zhǔn)比較常見,現(xiàn)在2.0標(biāo)準(zhǔn)應(yīng)該普及了吧。2.0標(biāo)準(zhǔn)可以支持4K x 2K ,最大幀頻到60 Hz。現(xiàn)在HDMI2.1的標(biāo)準(zhǔn)都出來了,都能支持48 Gbps, 支持4K120Hz的畫面?zhèn)鬏敗?/p>

TMDS( Trans it ion Minimized Differential Signa l ing)

最小化傳輸差分信號(hào)傳輸技術(shù)。TMDS是一種微分信號(hào)機(jī)制,采用的是差分傳動(dòng)方式。看到TMDS,就想起LVDS,都有抗干擾能力。至于兩者的區(qū)別,這里就不做展開了。

TMDS使用的也是8b/10b編碼技術(shù),但其編碼方式和PCIe&SATA等串行編碼方式不同,通過特殊的編碼來減少視頻信號(hào)傳輸時(shí)信號(hào)線上的跳變邊沿從而控制對(duì)外的電磁輻射,同時(shí)又可以保證接收端正確的時(shí)鐘鎖定。

一個(gè)HDMI包括3個(gè)TMDS數(shù)據(jù)通道和1個(gè)TMDS時(shí)鐘通道

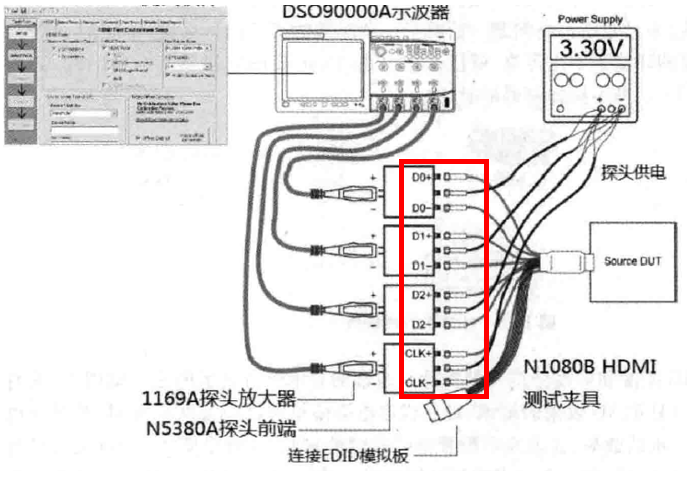

HDMI 的測(cè)試需要對(duì)高分辨率&低分辨率以及不同分辨率下不同幀頻的測(cè)試。下圖紅色標(biāo)記處需要手動(dòng)擰下再交叉擰上,來測(cè)試不同組合。這玩意戴上手套接口就不好擰緊,影響測(cè)試結(jié)果。光手?jǐn)Q,如果測(cè)得不順利,后果比較嚴(yán)重。手疼真記憶猶新。

HDMI的測(cè)試需要專門提供一個(gè)3.3 V的電源,直流偏置來保證信號(hào)的輸出。這也是跟其他接口測(cè)試不一樣的地方。

測(cè)試階段流程圖:

測(cè)試結(jié)束后,整合相關(guān)測(cè)試報(bào)告上傳系統(tǒng)。如果測(cè)試中有Fail項(xiàng)目,需要給出相關(guān)原因,提出解決或者優(yōu)化方案。

04

調(diào)試和解決問題

一、配合改進(jìn)

別的工種需要優(yōu)化和修改,或者導(dǎo)入和支持新的部件,涉及到高速線號(hào)部分,我們需要進(jìn)行相關(guān)調(diào)試及測(cè)試認(rèn)證,來配合產(chǎn)品優(yōu)化及功能升級(jí)。

二、問題解決

高速信號(hào)方面的測(cè)試,如果遇到Fail的項(xiàng)目,就需要Debug。如果確認(rèn)需要修改或者優(yōu)化版圖來解決,需要盡快將修改建議統(tǒng)一格式,上傳系統(tǒng)。Layout工程師修改優(yōu)化Layout后,需要我們確認(rèn)修改是否符合要求,并在系統(tǒng)確認(rèn)。

回板后,需要再次測(cè)試驗(yàn)證,確認(rèn)是否解決之前階段的問題。

三、市場(chǎng)問題

產(chǎn)品上市后,會(huì)有市場(chǎng)問題。高速信號(hào)完整性相關(guān)的問題,比如USB3.0接口不識(shí)別、HDMI不支持高分辨率等問題,都需要我們來確認(rèn)、分析與解決。

總結(jié)

其實(shí),上面所寫的幾個(gè)階段內(nèi)容,是經(jīng)過修改整理的。實(shí)際的機(jī)種劃分階段,肯定跟這個(gè)大有不同。只不過信號(hào)完整性工程師的工作內(nèi)容大體就是這些,大同小異。疑難雜癥的問題就另當(dāng)別算了。如果說硬件工程師是原理圖上功能的實(shí)現(xiàn),信號(hào)完整性工程師更多的是PCB板級(jí)信號(hào)質(zhì)量的管理。隨著產(chǎn)品速率的高速化及復(fù)雜化,信號(hào)完整性工程師將越來越……

工作流程詳細(xì)圖

審核編輯 :李倩

-

阻抗

+關(guān)注

關(guān)注

17文章

940瀏覽量

45822 -

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

394文章

4670瀏覽量

85293 -

信號(hào)完整性

+關(guān)注

關(guān)注

68文章

1397瀏覽量

95386

原文標(biāo)題:5000字圖文詳解SI信號(hào)完整性工程師工作流程

文章出處:【微信號(hào):mcu168,微信公眾號(hào):硬件攻城獅】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

什么是信號(hào)完整性SI?信號(hào)完整性設(shè)計(jì)的難點(diǎn)

詳解SI信號(hào)完整性工程師工作流程

詳解SI信號(hào)完整性工程師工作流程

評(píng)論