我一直沒(méi)搞明白BUFIO是干嘛用的。

官方解釋有這么一段話(huà),如下:(virtex的)

“BUFIO是用來(lái)驅(qū)動(dòng)I/O列內(nèi)的專(zhuān)用時(shí)鐘網(wǎng)絡(luò),這個(gè)專(zhuān)用的時(shí)鐘網(wǎng)絡(luò)獨(dú)立于全局時(shí)鐘資源,適合采集源同步數(shù)據(jù)。BUFIO只能由位于同一時(shí)鐘區(qū)域的Clock-Capable I/O驅(qū)動(dòng)。一個(gè)時(shí)鐘區(qū)域有4個(gè)BURIO,其中的2個(gè)可以驅(qū)動(dòng)相鄰區(qū)域的I/O時(shí)鐘網(wǎng)絡(luò)。BUFIO不能驅(qū)動(dòng)邏輯資源(CLB、BRAM等),因?yàn)镮/O時(shí)鐘網(wǎng)絡(luò)只存在于I/O列中。”

就是如果BUFIO只能驅(qū)動(dòng)IO,到達(dá)不了CLB和RAM,可是數(shù)據(jù)最終是要進(jìn)邏輯的啊,為什么呢?

首先、需要明確BUFIO是輸入用的。BUFIO是用來(lái)驅(qū)動(dòng)輸入時(shí)鐘的,將外部時(shí)鐘引入FPGA的!與IOBUF不同啊,但與IBUFG類(lèi)似,時(shí)鐘信號(hào)進(jìn)FPGA也可以經(jīng)過(guò)IBUFG。

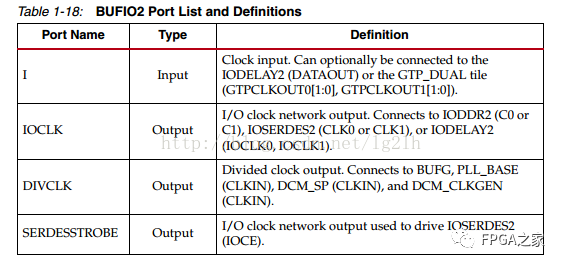

其次、再來(lái)看BUFIO的輸入和輸出:SPARTAN6 的UG382手冊(cè)里這么寫(xiě)的,如下:

BUFIO2 can drive ISERDES2 and OSERDES2 for either SDR or DDR clocking. BUFIO2 can

also route clock inputs from either a GCLK or a GTP_DUAL tile to a BUFG, DCM, or PLL

clock input. BUFIO2_2CLK can be used to replace one of the BUFIO2s required for DDR

clocking of the ISERDES2 and OSERDES2

(SDR:?jiǎn)芜呇兀珼DR:雙邊沿)

就是說(shuō)BUFIO2輸入可以是GCLK(全局時(shí)鐘)和GTP_DUAL。然后輸出到BUFG或者,DCM ,PLL的時(shí)鐘輸入。

也就是說(shuō)數(shù)據(jù)流順序 PAD-->BUFIO-->BUFG或者PAD-->BUFIO-->DCM(PLL)--->BUFG不知道有這樣用的嗎。

但實(shí)際應(yīng)用可以這樣,BUFIO配和ISERDES2使用,ISERDES2是將串行數(shù)據(jù)轉(zhuǎn)成并行數(shù)據(jù),相當(dāng)于分頻了。而B(niǎo)UFIO具有分頻的功能。

舉例串行數(shù)據(jù)轉(zhuǎn)成4bit并行數(shù)據(jù):串行數(shù)據(jù)相當(dāng)4分頻,同樣將隨路時(shí)鐘clk_in(就是和串行數(shù)據(jù)同步進(jìn)來(lái)的時(shí)鐘,,作為串行數(shù)據(jù)的采集時(shí)鐘)同步BUFIO接進(jìn)FPGA,

BUFIO可以將輸入的隨路時(shí)鐘clk_in進(jìn)行4分頻為clk_in4。這樣把clk_in4給BUFG,然后就可以同步將4bit的數(shù)據(jù)輸入采集到邏輯FIFO中去了。

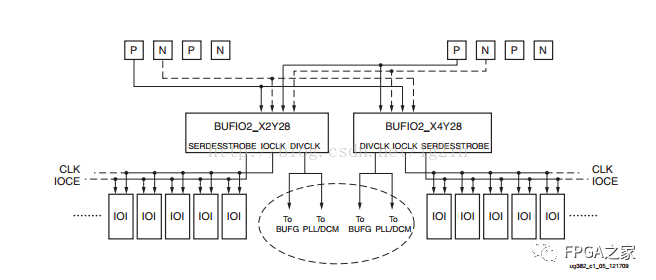

配個(gè)圖,看看BUFIO的輸入輸出可以接什么:

輸出鏈接示意圖,如下:可以看到PN-->BUFIO-->BUFG(DCM)或者PN-->BUFIO-->IO,驅(qū)動(dòng)IO(PN只差分對(duì)的P和N)

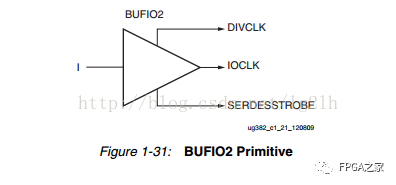

結(jié)合一下BUFIO的原語(yǔ)結(jié)構(gòu):

可以看出:

- IOCLK就去驅(qū)動(dòng)IO了或者IOSERDES2的CLK0,1;IODDR2等

- DIVCLK可以去接BUFG或者PLL。

- SERDESSTROB可以去驅(qū)動(dòng)IOSERDES2的IOCE使能腳了。

以上是對(duì)SP6講的,在virtex里面,有文章開(kāi)頭那句話(huà):BUFIO是用來(lái)驅(qū)動(dòng)I/O列內(nèi)的專(zhuān)用時(shí)鐘網(wǎng)絡(luò),這個(gè)專(zhuān)用的時(shí)鐘網(wǎng)絡(luò)獨(dú)立于全局時(shí)鐘資源,適合采集源同步數(shù)據(jù)。BUFIO只能由位于同一時(shí)鐘區(qū)域的Clock-Capable I/O驅(qū)動(dòng)。一個(gè)時(shí)鐘區(qū)域有4個(gè)BURIO,其中的2個(gè)可以驅(qū)動(dòng)相鄰區(qū)域的I/O時(shí)鐘網(wǎng)絡(luò)。BUFIO不能驅(qū)動(dòng)邏輯資源(CLB、BRAM等),因?yàn)镮/O時(shí)鐘網(wǎng)絡(luò)只存在于I/O列中。”

就是說(shuō)virtex里面BUFIO好像只能由Clock-Capable I/O驅(qū)動(dòng)了。

-

時(shí)鐘

+關(guān)注

關(guān)注

10文章

1720瀏覽量

131364 -

CLB

+關(guān)注

關(guān)注

0文章

29瀏覽量

5941 -

i/o

+關(guān)注

關(guān)注

0文章

33瀏覽量

4570

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

xilinx中的carry4原語(yǔ)在高云FPGA中用什么原語(yǔ)替代?

Xilinx FPGA無(wú)痛入門(mén),海量教程免費(fèi)下載

如何從Virtex原語(yǔ)切換到Spartan原語(yǔ)?

為什么當(dāng)我將錯(cuò)誤降級(jí)為警告時(shí), 在FPGA編輯器中就找不到BUFIO2了?

請(qǐng)問(wèn)ISERDESE2原語(yǔ)支持多少位輸入?

FPGA上有哪些額外的原語(yǔ)?

FPGA雙沿采樣之IDDR原語(yǔ)實(shí)現(xiàn) 精選資料推薦

STM32入門(mén)之RCC與復(fù)位

Xilinx 7 Series FPGA時(shí)鐘網(wǎng)絡(luò)的區(qū)別(BUFG,BUFGR,BUFIO)

Xilinx FPGA常用原語(yǔ)介紹

Vivado IDDR與ODDR原語(yǔ)的使用

(29)FPGA原語(yǔ)設(shè)計(jì)(差分時(shí)鐘轉(zhuǎn)單端時(shí)鐘)

(30)FPGA原語(yǔ)設(shè)計(jì)(單端時(shí)鐘轉(zhuǎn)差分時(shí)鐘)

FPGA入門(mén)之原語(yǔ)BUFIO的理解

FPGA入門(mén)之原語(yǔ)BUFIO的理解

評(píng)論