如今,SoCs正變得越來越復雜,數據經常從一個時鐘域傳輸到另一個時鐘域。

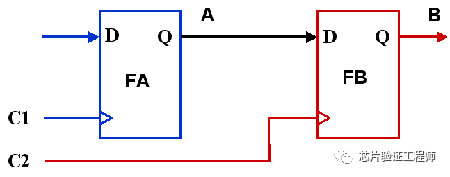

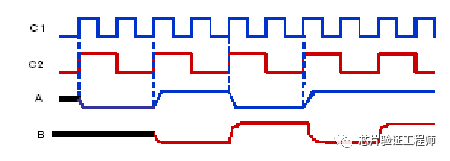

上圖信號A由C1時鐘域觸發,被C2時鐘域采樣。 根據這兩個時鐘之間的關系,在將數據從源時鐘傳輸到目標時鐘時,可能會出現不同類型的問題,并且這些問題的解決方案也有所不同。

本文討論了不同類型的跨時鐘域,以及每種類型中可能遇到的問題及其解決方案。 在接下來的所有部分中,都直接使用了上圖所示的信號名稱。 例如,C1和C2分別表示源時鐘和目標時鐘。 類似地,A和B分別被用作源觸發器輸出和目標觸發器輸出。 此外,源和目標觸發器被假定為正沿觸發。

跨時鐘域問題

本節描述了在出現跨時鐘域時可能出現的三個主要問題,然后還描述了這些問題的解決方案。

A.亞穩態問題。

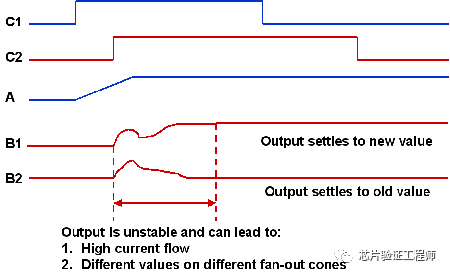

如果信號A上的翻轉發生在非常接近時鐘C2的邊沿處,它可能會導致在目標觸發器“FB”處的setup 或hold 違反。 結果,輸出信號B進行無限振蕩。 因此,輸出是不穩定的,在C2的下一個時鐘邊緣到達之前也可能會穩定到某個穩定的值。這種現象被稱為亞穩態,或者說觸發器“FB”已經進入亞穩態。

從設計的角度來看,亞穩態又會產生以下后果:

1、如果不穩定的數據被輸入到設計中的其他幾個地方,它可能會導致大電流,在最壞的情況下甚至導致芯片燒壞。

2、不同的 fan-out可能會讀取不同的信號值,并可能導致設計進入未知的功能狀態,導致設計出現功能問題。

3、目標時鐘域輸出可能穩定到新值或返回到舊值。 然而,傳播延遲可能很高,會導致時序問題。

如下圖,如果輸入信號A在非常接近C2時鐘的上升沿翻轉,則目標觸發器的輸出可以是亞穩態的。 因此,它可以不穩定,并可能最終穩定到信號B1和B2所描述的1或0。

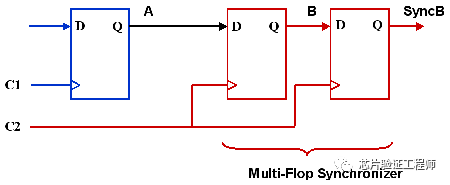

可以通過在目標域中添加同步器來避免亞穩態問題。 同步器允許振蕩在足夠的時間穩定下來,并確保在目標時鐘域獲得穩定的輸出。 一個常用的同步器是一個級聯觸發器,如下圖所示。

該結構主要用于設計中的控制信號和單比特數據信號。 多位的數據信號需要其他類型的同步方案,如MUX recirculation、握手和FIFO。

B.數據丟失

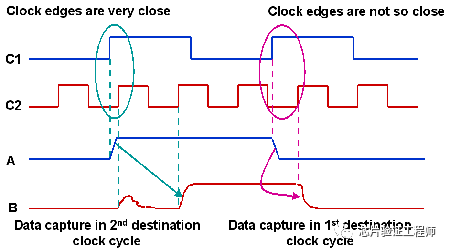

每當生成一個新的源數據時,由于亞穩態性,它可能不會在目標時鐘的第一個周期中被目標域捕獲。只要源信號上的每個翻轉都在目標域中被捕獲,數據就不會丟失。為了確保這一點,源數據應在一段最短的時間內保持穩定,以便滿足對目標時鐘的至少一個邊沿的setup 和hold 時間的要求。

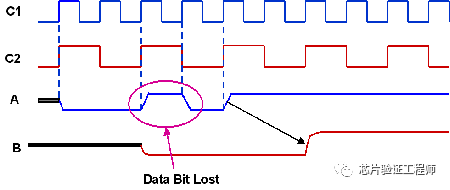

如果C1和C2的時鐘邊沿非常靠近,則在源數據A翻轉之后的C2的第一個時鐘邊沿無法捕獲它。 該數據最終被時鐘C2的第二個時鐘邊沿捕獲,如下圖所示。

但是,如果在數據A翻轉和時鐘C2的邊沿之間有足夠的時間,則在C2的第一個周期捕獲數據。 因此,源時鐘域數據和目標時鐘域數據之間可能不會一一對應。 無論如何,一般情況下源數據上的每個翻轉都應該在目標時鐘域中被捕獲。

假設源時鐘C1的速度是目標時鐘C2的兩倍,并且這兩個時鐘之間沒有相位差。 進一步假設在時鐘C1的正邊沿生成的輸入數據序列“A”為“00110011”。 在時鐘C2的正邊沿捕獲的數據B將為“0101”。 在這里,由于信號A上的所有翻轉都被B捕獲了,所以數據不會丟失。

但是,如果輸入序列為“00101111”,則目標域中的輸出將為“0011”。 這里輸入序列中的第三個數據值“1”丟失。

為了防止數據丟失,數據應該在源時鐘域中保持足夠長的時間不變,以便在目標時鐘域中正確捕獲。 換句話說,在源數據上的每次轉換之后,至少有一個目標時鐘邊沿應該到達沒有違反setup或hold的地方,以便在目標時鐘域中正確地捕獲源數據。

C. 數據一致性

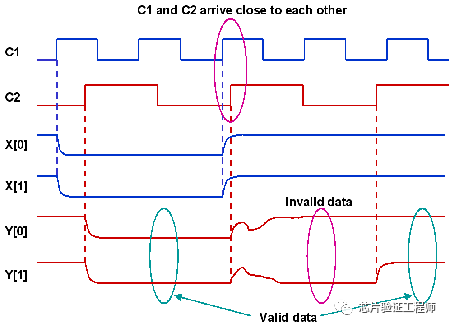

如前一節所示,每當在源時鐘域中生成新數據時,可能需要1個或多個目標時鐘周期來捕獲它。 考慮這樣一種情況,即多個信號從一個時鐘域傳輸到另一個時鐘域,并且每個信號使用多級觸發器同步器分別進行同步。 如果所有信號同時發生變化,并且源時鐘和目標時鐘邊沿接近,那么一些信號可能在第一個時鐘周期中在目標域中被捕獲,而另一些信號可能通過亞穩態在第二個時鐘周期中被捕獲。 這可能會導致目標端信號上的值組合無效。 也就是說,在這種情況下,數據的一致性已經丟失了。

如果這些信號一起控制著設計的某些功能,那么這種無效的狀態可能會導致功能錯誤。

例如:假設“00”和“11”是由時鐘C1生成的信號X[0:1]的兩個有效值。 最初在X的兩個位上都有一個從1->0的過渡。 這兩個轉變在第一個周期本身都被時鐘C2捕獲。 因此,信號Y變成了“00”。

接下來,在信號X的兩個比特位上都有一個從0->1的轉換。 在這里,時鐘C2的上升沿接近于信號X的翻轉。 X[0]上的翻轉在第一個時鐘周期中被捕獲,而X[1]上的翻轉在C2的第二個時鐘周期中被捕獲。 這將導致Y[0:1]上的一個中間值為“10”,這是一個無效的狀態。 在這種情況下,數據的一致性丟失了。

在上面的示例中,問題的原因是所有比特沒有在相同的目標時鐘周期中捕獲。 如果所有比特在同一周期中保留其原始值或更新值,則設計要么保持原始狀態,要么進入正確的新狀態(參考異步FIFO)。

如果電路的設計方式是,在將設計從一種狀態更改到另一種狀態時,只需要更改一個位,那么該位將更改為一個新值或者保留原始值。 由于所有其他位在這兩種狀態下都有相同的值,所以在這種情況下,完整的總線要么變為新值,要么保留原始值。

這反過來又意味著,如果總線是格雷編碼的,那么這個問題將會得到解決,并且將永遠不會得到一個無效的狀態。

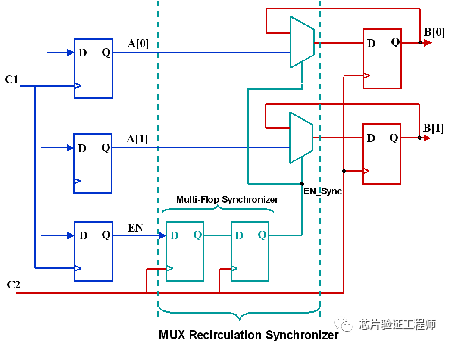

但是,這僅適用于控制總線,因為無法對數據總線進行格雷編碼。在這種情況下,可以使用握手、FIFO和MUX recirculation(如下圖)等其他技術來生成一個公共的控制邏輯來正確地傳輸數據。

這里,在源時鐘域中產生的控制信號EN使用多級觸發器同步器在目標域中進行同步。同步控制信號EN_Sync驅動mux的選擇引腳,從而控制總線A所有位的數據傳輸。通過這種方式,總線的各個位不會單獨同步,因此不存在數據不一致性。但是,重要的是要確保當控制信號被激活時,源域數據A[0:1]應保持不變。

審核編輯:湯梓紅

-

時鐘

+關注

關注

10文章

1720瀏覽量

131365 -

總線

+關注

關注

10文章

2867瀏覽量

87991 -

觸發器

+關注

關注

14文章

1996瀏覽量

61052 -

輸出信號

+關注

關注

0文章

275瀏覽量

11847 -

時鐘域

+關注

關注

0文章

52瀏覽量

9529

原文標題:驗證學習 | 深刻理解跨時鐘域:三個主要問題和解決方案

文章出處:【微信號:芯司機,微信公眾號:芯司機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

討論跨時鐘域時可能出現的三個主要問題及其解決方案

深刻理解Python中的元類(metaclass)

深刻理解跨時鐘域的三個主要問題和解決方案

深刻理解跨時鐘域的三個主要問題和解決方案

評論