一、綜合理論基礎(chǔ)

綜合理論,稱為綜合目的編碼風(fēng)格(Coding Style for Synthesis),和非綜合目的編碼風(fēng)格(Coding Style for NonSynthesis)。

綜合目的編碼,是指:

什么樣的代碼或代碼塊,對(duì)應(yīng)綜合結(jié)果的什么樣的電路(What Statements is What Circuit)

需要什么電路,應(yīng)該使用什么樣的代碼描述(What Circuit is What Statements)

根據(jù)綜合理論的發(fā)展和HDL語(yǔ)言的發(fā)展,西方理論界提出綜合友好的概念,即EDA的工程師,必須知道代碼的綜合意義。與西方科學(xué)技術(shù)體系的“形式邏輯”相同,綜合理論也是誕生與“形式邏輯”。

1.1代碼模型分析CMA(Code-Model Analysis)

綜合理論的基礎(chǔ)是代碼模型分析:

代碼行中,被驅(qū)動(dòng)的信號(hào)(賦值號(hào)左側(cè)的信號(hào)),對(duì)應(yīng)所綜合電路的輸出信號(hào)

代碼行中,被引用的信號(hào)(賦值號(hào)右側(cè)的信號(hào)),對(duì)應(yīng)所綜合電路的輸入信號(hào)

根據(jù)電路的實(shí)際物理,進(jìn)行資源分配。

代碼或代碼塊CB(Code Block),所綜合得到的電路模型,稱為代碼模型CM(Code Model)

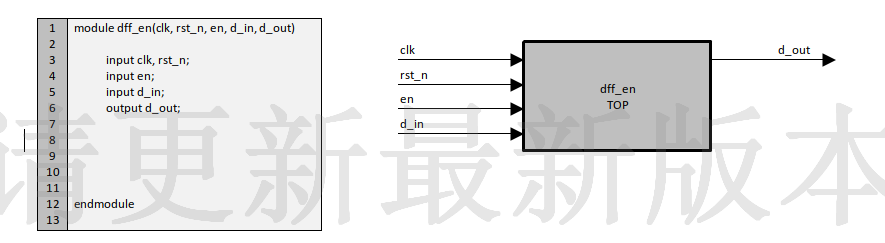

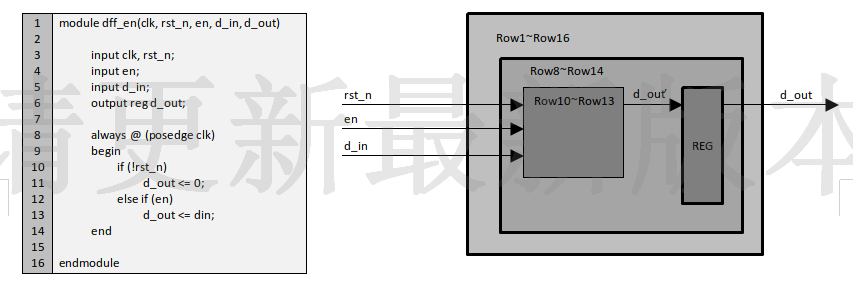

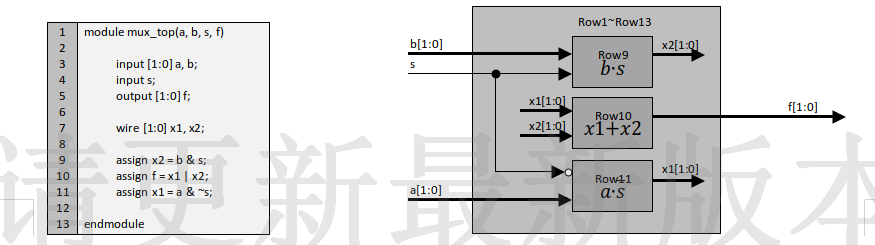

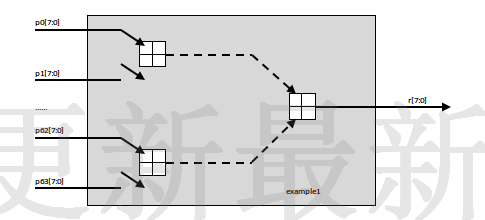

例一(顯模Explicit Model):

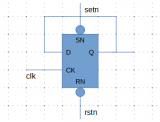

1.1.1頂層電路模型

1.1.2頂層描述

1.2并發(fā)語(yǔ)句和順序語(yǔ)句的可綜合性

HDL語(yǔ)言與算法語(yǔ)言類似,需要討論研究編碼順序與綜合意義之間的關(guān)系。在HDL的早期理論界,是這樣定義的:

在HDL的編碼順序中,編寫順序發(fā)生改變,不會(huì)影響綜合結(jié)果的代碼,稱為并發(fā)語(yǔ)句CAS(Concurrent Assignment Statements)

在HDL的編碼順序中,編寫順序發(fā)生改變,將會(huì)影響綜合結(jié)果的代碼,稱為順序語(yǔ)句SAS(Sequential Assignment Statements)

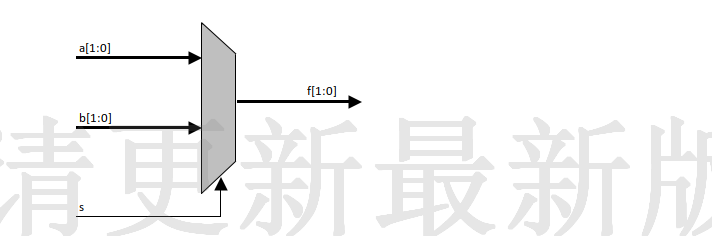

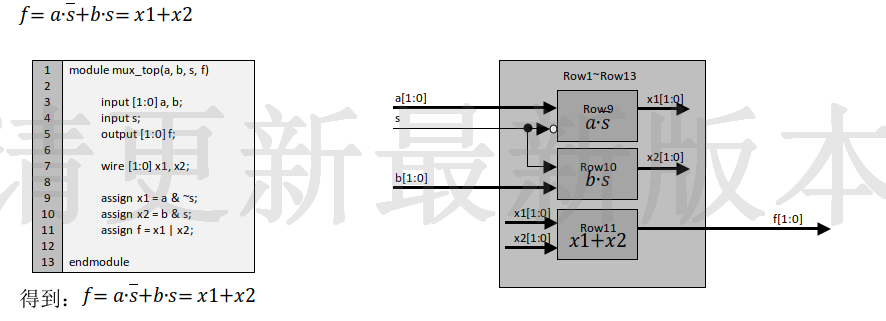

例二(并發(fā)語(yǔ)句例子):

一個(gè)二選一多路器的邏輯:

布爾表達(dá)式:

改變編碼順序后:

得到:

綜合意義相同,是并發(fā)語(yǔ)句CAS

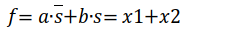

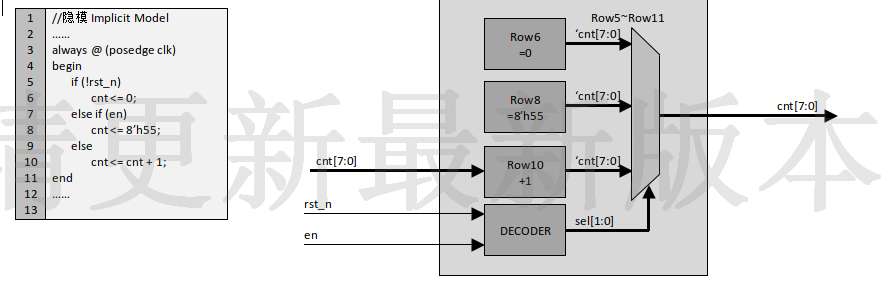

例三(順序語(yǔ)句例子)

譯碼邏輯真值表:

rst_n | en | sel | Note |

0 | 0 | SEL_ROW6 | 復(fù)位選擇 |

0 | 1 | SEL_ROW6 | |

1 | 0 | SEL_ROW10 | |

1 | 1 | SEL_ROW8 |

譯碼邏輯真值表:

rst_n | en | sel | Note |

0 | 0 | SEL_ROW8 | 復(fù)位選擇 |

0 | 1 | SEL_ROW6 | |

1 | 0 | SEL_ROW10 | |

1 | 1 | SEL_ROW6 |

綜合意義不同,是順序語(yǔ)句SAS

常用語(yǔ)句的并發(fā)和順序類型表:

語(yǔ)句塊 | 描述方式 | 類型 | Note |

module | module-endmodule | CAS | 顯模描述 |

begin | begin-end | CAS | 隱模描述 |

behaviour | always | CAS | |

datflow | assign | SAS | |

if | if-else if-else | SAS | |

case | case-endcase | SAS | |

loop | while for | CAS | for語(yǔ)句可綜合 |

sub/fuc | task-endtask function-endfunction | CAS | |

二、循環(huán)語(yǔ)句的可綜合性

2.1循環(huán)語(yǔ)句的可綜合性描述

循環(huán)語(yǔ)句中的循環(huán)體,在算法語(yǔ)言中,循環(huán)體的執(zhí)行時(shí)一個(gè)典型的順序過程,但在HDL語(yǔ)言中,用于綜合目的時(shí),這些循環(huán)體卻是一個(gè)并發(fā)過程,此時(shí),這些循環(huán)體被綜合器重復(fù)描述,以提高編碼效率。

循環(huán)體中的輸出,不同的循環(huán)變量引用時(shí),得到不同的輸出,則稱為:并發(fā)循環(huán),對(duì)應(yīng)的電路框架稱為并發(fā)循環(huán)框架。

循環(huán)體中的輸出,在不同的循環(huán)變量引用時(shí),得到相同的輸出,則稱為:順序循環(huán),對(duì)應(yīng)的電路框架稱為順序循環(huán)框架。

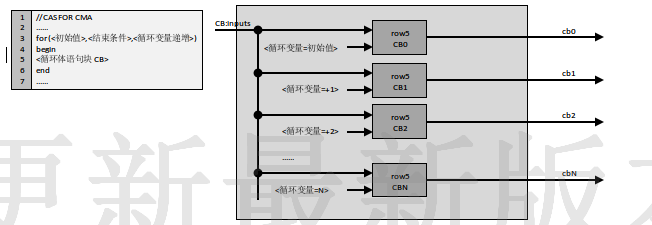

行為并發(fā)循環(huán)框架CMA:

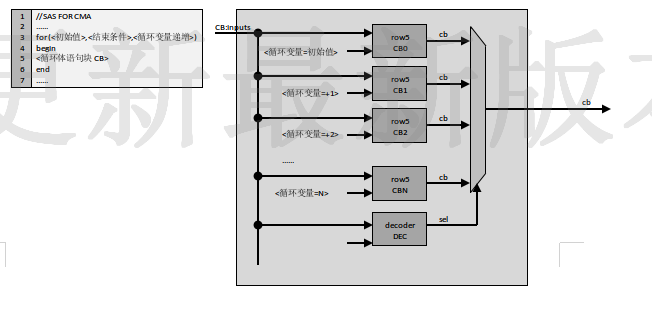

行為順序循環(huán)框架CMA:

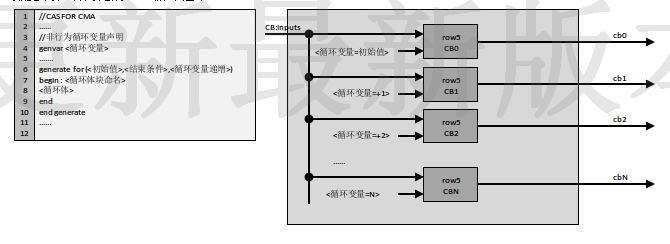

數(shù)據(jù)流和結(jié)構(gòu)化的CAS循環(huán)框架:

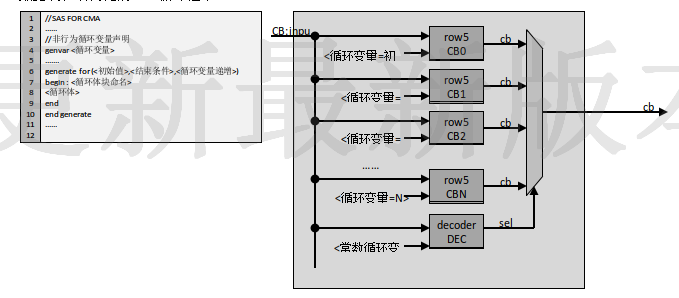

數(shù)據(jù)流和結(jié)構(gòu)化的SAS循環(huán)框架:

2.2循環(huán)語(yǔ)句設(shè)計(jì)例子一

設(shè)計(jì)一個(gè)如下圖所示的具有寬度為8的64輸入端口的異或二叉樹電路:

使用數(shù)學(xué)歸納法,證明循環(huán)語(yǔ)句實(shí)現(xiàn)的可綜合性:

首先將循環(huán)變量修改為一個(gè)很小的基數(shù),使用結(jié)構(gòu)化建模描述,加以驗(yàn)證。

將基數(shù)加一,仍然使用結(jié)構(gòu)化建模模型,加以驗(yàn)證。

將循環(huán)變量修改為L(zhǎng)PM定制,加入循環(huán)變量,加以驗(yàn)證

將LPM定制的循環(huán)變量加以,加以驗(yàn)證

歡迎加入至芯科技FPGA微信學(xué)習(xí)交流群,這里有一群優(yōu)秀的FPGA工程師、學(xué)生、老師、這里FPGA技術(shù)交流學(xué)習(xí)氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點(diǎn)個(gè)在看你最好看

原文標(biāo)題:至芯FPGA課程之綜合理論分享

文章出處:【微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21665瀏覽量

601828

原文標(biāo)題:至芯FPGA課程之綜合理論分享

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

接口測(cè)試理論、疑問收錄與擴(kuò)展相關(guān)知識(shí)點(diǎn)

芯至科技與Ampere達(dá)成業(yè)務(wù)合作

【全新課程資料】正點(diǎn)原子《ESP32物聯(lián)網(wǎng)項(xiàng)目實(shí)戰(zhàn)》培訓(xùn)課程資料上線!

國(guó)產(chǎn)RK3568J基于FSPI的ARM+FPGA通信方案分享

一個(gè)更適合工程師和研究僧的FPGA提升課程

珠海鏨芯實(shí)現(xiàn)28納米FPGA流片

芯璐科技數(shù)千萬(wàn)元天使輪投資,系FPGA芯片設(shè)計(jì)企業(yè)

fpga學(xué)習(xí)需要具備哪些課程

基于單片機(jī)控制的交通燈設(shè)計(jì)

FPGA管教分配需要考慮因素

FPGA基本開發(fā)設(shè)計(jì)流程

國(guó)外大學(xué)的FPGA開發(fā)項(xiàng)目盤點(diǎn)

至芯FPGA課程之綜合理論分享

至芯FPGA課程之綜合理論分享

評(píng)論