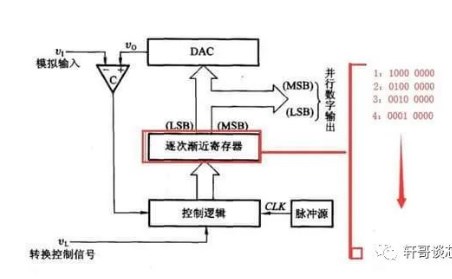

STM32中的ADC是逐次逼近型ADC(Successive Approximation ADC),是逐個產生比較電壓Vref,并逐次與輸入電壓分別比較,以逐漸逼近的方式進行A/D轉換的。而其中的用來產生Vref的電路就是DAC電路。因此一般DAC電路比較容易設計,而DAC在采樣速度和精度的權衡上會比較復雜。

SAR ADC的轉換原理是把輸入的模擬信號按規定的時間間隔采樣(采樣),并與一系列標準的數字信號相比較,數字信號逐次收斂,直至兩種信號相等為止(量化完成),最后輸出代表此信號的二進制數(編碼)。

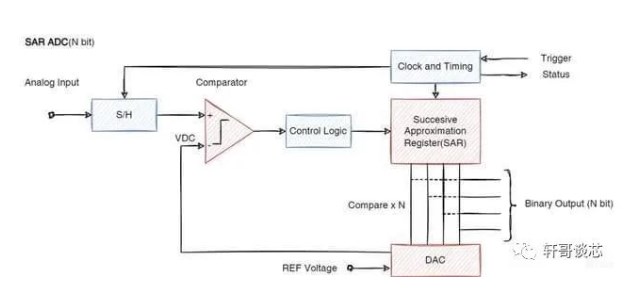

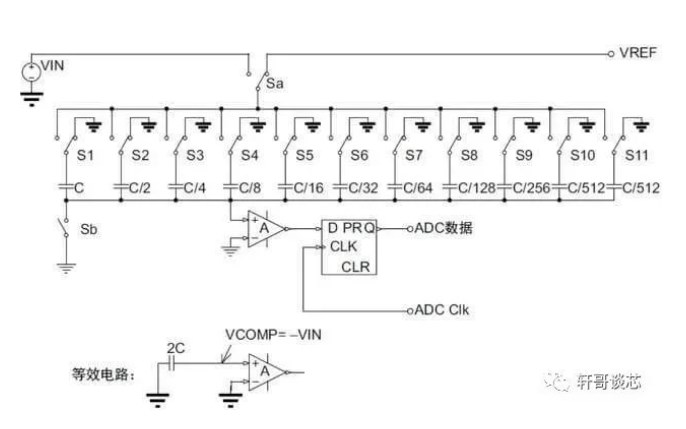

SAR ADC結構

結構上主要包括采樣保持電路(S/H),比較器(COMPARATOR,COMP),SAR邏輯控制電路、時鐘(CLOCK)和時序(TIMING)控制電路及DAC電路。

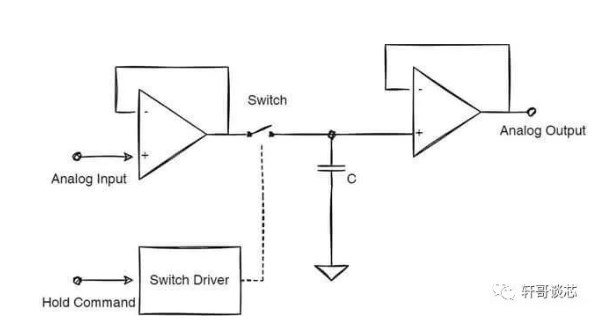

S/H電路

為了達到快速的采樣,被采樣的脈沖寬度一般是很短的,在下一個采樣脈沖到來之前,要暫時保持所采得的樣值脈沖幅度,以便進行后續轉換。所以,在采樣電路之后和比較電路之間要加保持電路。它的原理是通過一個開關連接一個電容,通過給電容進行充電來保持模擬信號的幅值信息。

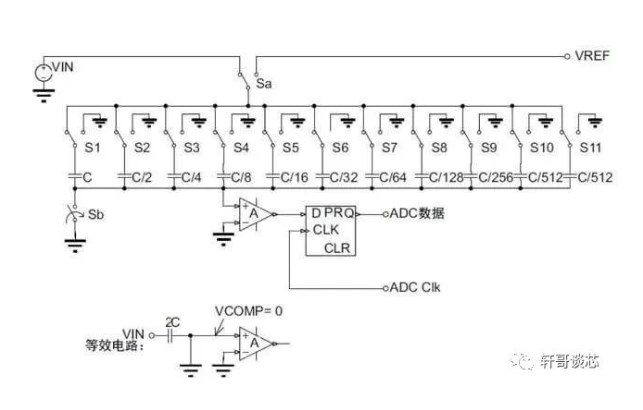

DAC電路

大多SAR ADC的DAC都使用電容式DAC來提供內在的跟蹤/保持功能。電容式DAC是采用電荷再分配原理來產生模擬輸出電壓的。電容式DAC由N個具有二進制權重值的電容器陣列再加上一個“虛擬LSB”電容器組成。

首先通過Sa開關連接VIN,并將所有S1-S11的開關連接到VIN,給所有并聯的電容進行充電,這樣就將所有電容充滿,并且充電電壓為VIN。

然后通過將Sa開關連接到Vref,并且通過數字信號對應到S1-S11的開關上,也就是關閉一些電容的開關連接到GND上,斷開電容,對地放電。

此時對于Vref上的電壓就會根據斷開電容的容量使得輸出電壓降低,從而將數字信號轉換成一個模擬信號。

電容器陣列容量總量要等于2C。

轉換步驟

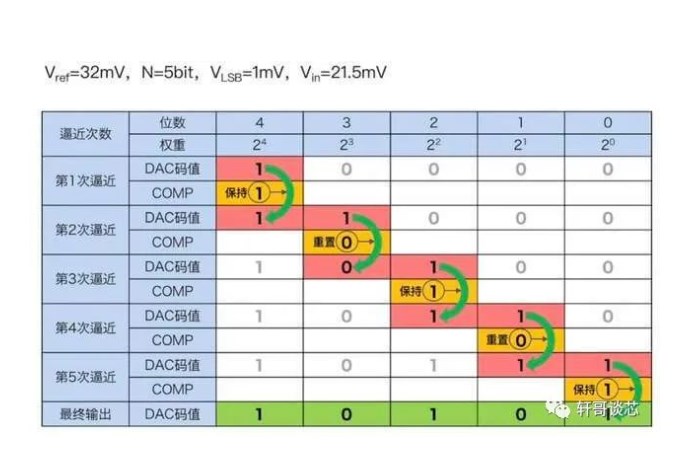

轉換步驟數等于 ADC的分辨率,比如12bits ADC就有12個轉換步驟,每個 ADC 時鐘產生一個數據位。

采樣狀態

該狀態下,電容充電至電壓VIN。Sa切換至VIN,采樣期間Sb開關閉合。

保持狀態

該狀態下,輸入斷開,電容保持輸入電壓。Sb開關打開,然后S1-S11切換至接地,且Sa切換至VREF。

轉換(量化和編碼)狀態

該狀態下,每個 ADCCLK 執行一個步驟,每一步完成后 ADC 輸出一位數。采用二分法進行逐次逼近到 ADC 的精度(位數)。整個轉換過程如下圖所示。

-

電容器

+關注

關注

63文章

6102瀏覽量

98456 -

比較器

+關注

關注

14文章

1614瀏覽量

106836 -

STM32

+關注

關注

2258文章

10828瀏覽量

352509 -

充電電壓

+關注

關注

0文章

27瀏覽量

6743 -

adc信號

+關注

關注

0文章

5瀏覽量

2216

發布評論請先 登錄

相關推薦

藍牙中的拓撲結構有散射網,MESH網是同一回事嗎?

MOV中的8位圖立即數是怎么一回事

MOV中的8位圖立即數是怎么一回事呢?

請問芯片中ISP Flash和LDROM是不是一回事?

PCB設計中自動布線和手動布線是怎么一回事?資料下載

STM32中的SAR ADC是怎么一回事?

STM32中的SAR ADC是怎么一回事?

評論