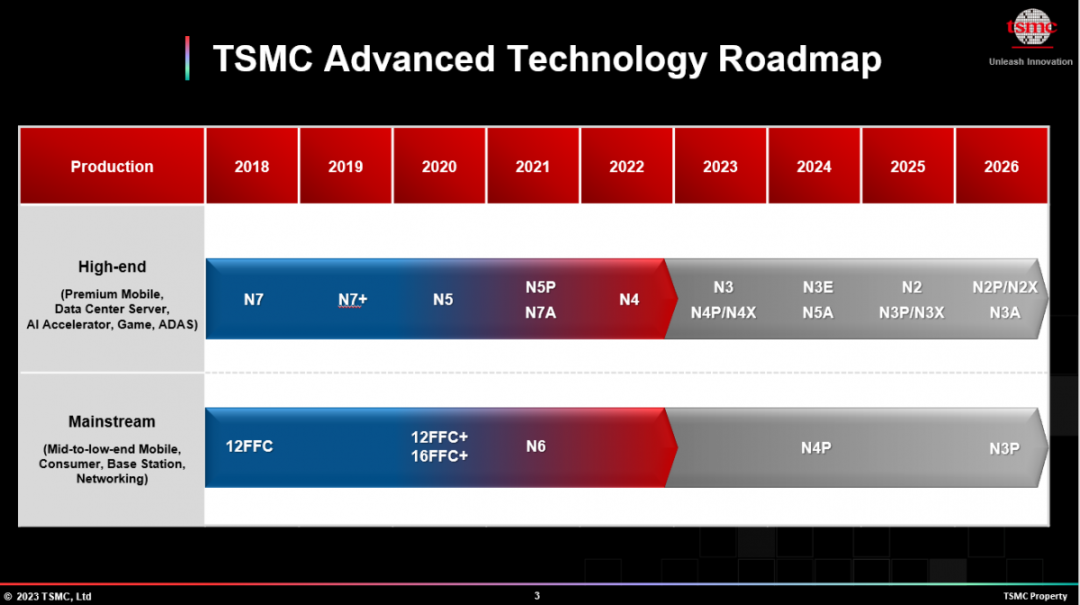

上個月的2023北美技術研討會上,臺積電又又又透露了一些N2家族工藝節點的新消息——計劃中的2nm工藝節點會在2025-2026年到來。結合這次的消息,以及過去1、2年三星和Intel透露相關各自2nm節點的消息,本文嘗試展望一下2025年以后的2nm工藝。

有關未來工藝展望,或者foundry廠路線圖,是這幾個主要市場參與者給予市場信心的關鍵。所以雖然3nm都還沒真正拿在我們手上,Intel、三星、臺積電也早就在宣傳再靠后的2nm,甚至更先進的工藝了,即便其中的某些八字都還沒一撇。

上個月的2023北美技術研討會上,臺積電又又又透露了一些N2家族工藝節點的新消息——計劃中的2nm工藝節點會在2025-2026年到來。那么結合這次的消息,以及過去1、2年三星和Intel透露相關各自2nm節點的消息,本文嘗試展望一下2025年以后的2nm工藝。

需要指出的是,以現如今半導體制造尖端工藝的復雜度和成本投入,即便foundry廠公布了技術路線圖,未來的變數也依然可能非常大——甚至連節點量產時間都只能做個參考。三星幾年前就曾說過3nm工藝有望于2020年全面上線;Intel早于2010年說過2017年就上馬7nm工藝;臺積電的放衛星名場面更多...所以本文的所有內容,在2025年之前就僅供參考。

最早的2nm,可能來自Intel?

從路(fang)線(wei)圖(xing)計劃表來看,臺積電和三星的一致口徑是2nm工藝預計于2025年開始量產——但起碼也是2025年下半年或者更晚的時間。

這里需要注意的問題是,“開始量產”“準備好量產”并非芯片問世時間。比如如果臺積電N2工藝將在2025年下半年開始量產,則N2工藝的芯片真正上市至少需要等到2026年;且從營收的角度來看,N2工藝產生的營收也要到2026年才會反映到財報中。

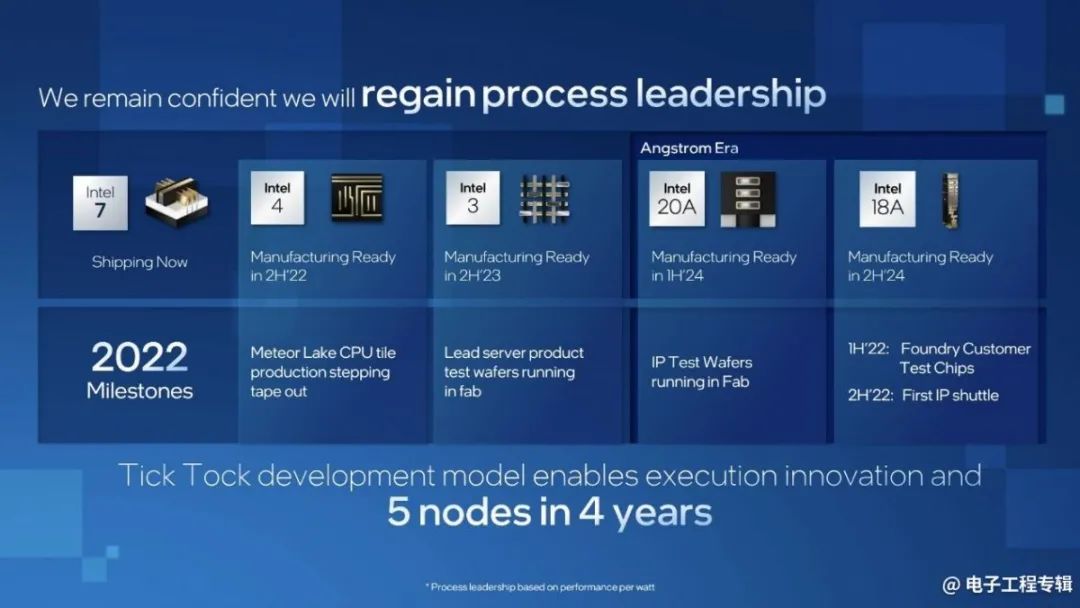

Intel這邊:自從7nm/5nm時代,在半導體制造工藝技術上被臺積電和三星趕超,Intel就改變了技術迭代策略。從2022年Int?el投資者會議更新過的計劃表來看,Intel 20A工藝——通常可看作是Intel版本的2nm工藝,即便Intel現在在市場宣傳上很忌諱去談x nm——“準備好量產”的時間是2024年上半年。

今年2月Intel在國內舉辦的戰略媒體溝通會上再度確認了Intel 20A“測試芯片已流片”。不過需要注意的是,因為現在foundry廠的工藝名稱(比如Intel 20A, TSMC N2, Samsung 2GAP)越來越放飛自我,而工藝名稱并不代表晶體管或器件的實際物理尺寸,加上現在我們并不十分清楚這三家的“2nm”工藝的器件尺寸,所以仍然很難在同一平臺上去說這三者是同代工藝。

Intel 20A工藝的后續工藝是18A——也是Intel此前宣稱要重返半導體制造工藝王座的一代節點,預期“準備好量產”的時間已經被提前到了2024年下半年。如果各家foundry廠的未來工藝能如期交付,則顯然Intel會是最快的。

但如前文所述,尖端制造工藝foundry廠有放衛星的傳統——當然這也不是他們想看到的。畢竟尖端制造工藝的技術難度和成本攀升速度,造就了大量的不確定性。

全部切換至GAAFET的一代工藝

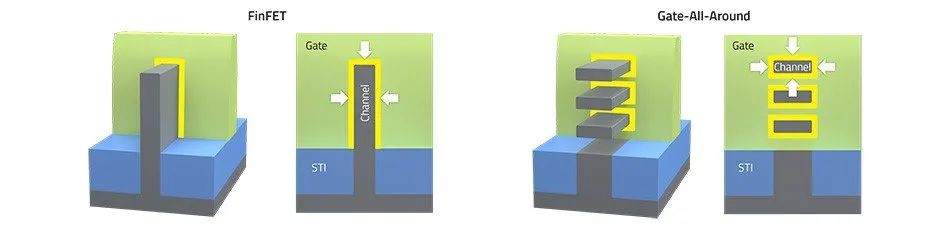

關注尖端制造工藝的同學應該都知道,三星在3nm這代工藝上就要開始采用GAAFET結構的晶體管上,替換用了這么多年的FinFET。GAA全稱gate-all-around——有關GAAFET器件結構,我們此前已多有撰文提及。從示意圖就不能看出,原先的fin被橫置過來——橫置以后叫做nanosheet。

這種結構的晶體管有效溝道寬度不僅靈活,而且比FinFET更大,能夠在器件整體尺寸縮減的情況下,達成更高的驅動電流、更出色的性能、更低的漏電流。調整nanosheet的寬度和數量,是能夠表現這種結構的靈活性的;則在更高性能、更低功耗之間就有了更大的選擇余地。

臺積電決定在N2工藝上采用nanosheet,而Intel則決定在Intel 20A工藝節點上采用RibbonFET。這些都是GAAFET結構的具體實施。

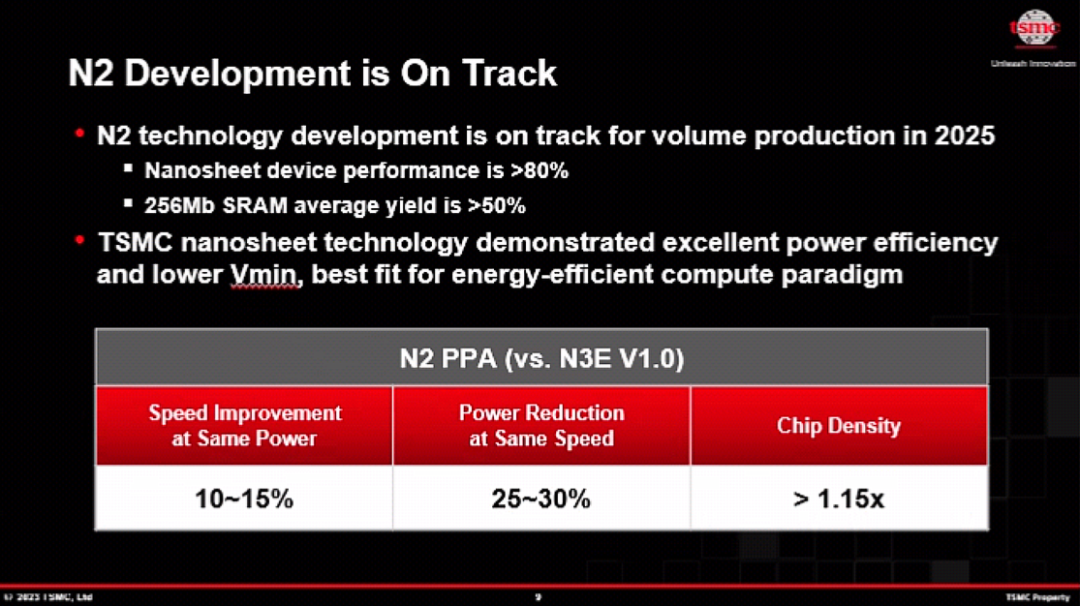

目前對外公開了結構、2nm節點迭代造成密度與性能變化的,臺積電似乎是唯一一個。臺積電在去年的技術研討會上提到,和N3E工藝相比,在相同功耗、相同晶體管數量的情況下,N2工藝能夠帶來性能方面10%-15%的提升;或者同頻率與復雜度下功耗25%-30%的下降;晶體管密度提升1.1倍。

性能、功耗數字變化,就臺積電工藝節點迭代的傳統來看,算是比較合理的。而且需要考慮到換晶體管結構,前期經驗不足導致的效率問題。但晶體管密度只提升1.1倍,就顯得非常拉垮。但需要注意這里的1.1倍密度提升,是基于一顆典型芯片包含50%的邏輯電路、30%的SRAM單元,以及20%的模擬電路。

通常我們說N5→N3工藝1.6倍晶體管密度提升,是特指邏輯電路。工藝節點之間,模擬和存儲電路部分的器件尺寸微縮速度通常總是慢于邏輯電路的。而且近兩代先進工藝節點,這兩者的微縮幅度尤其小。但無論如何1.1x都不是個很理想的數字。

在今年的技術研討會上,臺積電似乎更新了這個數字,變為>1.15x——對比對象當然仍是N3E。其實N3E相比N3的器件密度,傳說還變大了(這也是N3可能被拋棄的一個體現)。比較正面的信息是,在本次活動上臺積電說N2技術開發仍在軌道上,且不變的是2025年進入量產。

臺積電表示在正式進入大規模量產之前,其GAA晶體管性能正好于目標規格的80%,且256Mb SRAM測試芯片的平均良率已經超過了50%。據說能效和Vmin等方面的數據都比較理想,“非常適用于能效計算”需求。最近Synopsys才發布新聞稿說正與臺積電合作,針對N2工藝推進數字與定制設計EDA流程。

除了臺積電的另外兩家,似乎尚未就2nm工藝公布什么像樣的數字。Intel只是說Intel 4相比Intel 7會有20%的每瓦性能提升;Intel 3相比Intel 4則有18%的每瓦性能提升;Intel 20A相比Intel 3有15%的每瓦性能提升。

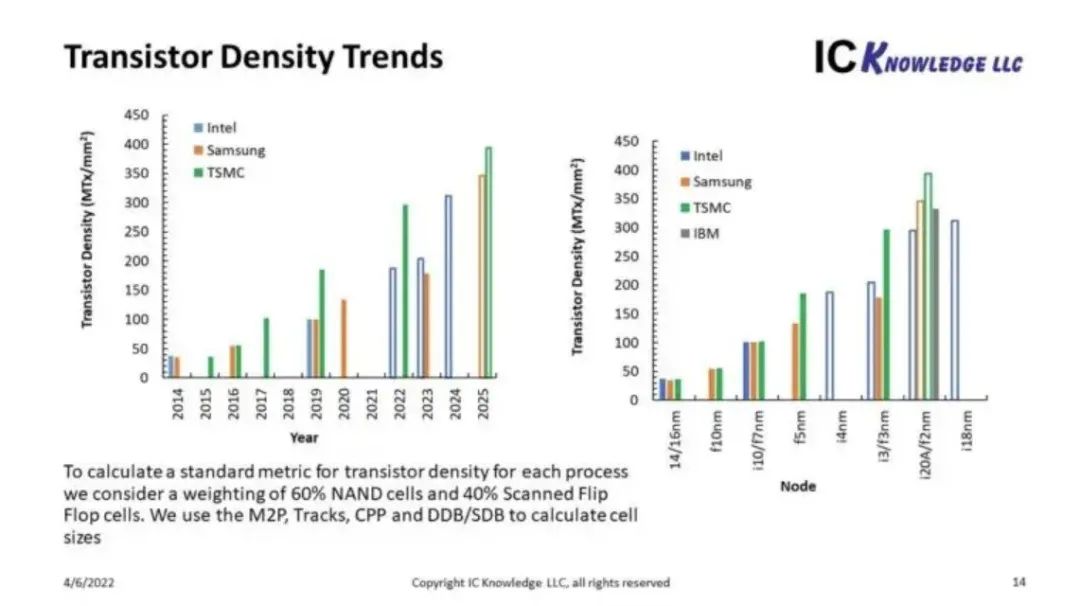

Scotten Jones去年4月寫過一篇文章,提到Intel 20A相比上代工藝會有1.6x密度提升——這說的當然就是邏輯電路的晶體管典型統計方式了。

從當時他給出的預測圖來看,如果只看晶體管密度,那么臺積電和三星仍將在絕對值上于2nm工藝節點上有所領先。這大約也能解釋Intel 20A的推出時間將早于臺積電N2和三星2GAP。或者說Intel 20A大概是實現了差拍/錯位競爭的。

的確在先進制造工藝越往后發展的當下,器件物理尺寸變化在不同的foundry廠之間可能會呈現出很大的不同;不同foundry廠的工藝也越來越難以劃歸到某一個統一的nm節點下。當然也可能是Intel的技術偏向性、競爭的市場領域有差異。但需要指出,IC Knowledge的這份數據可靠性是存疑的。

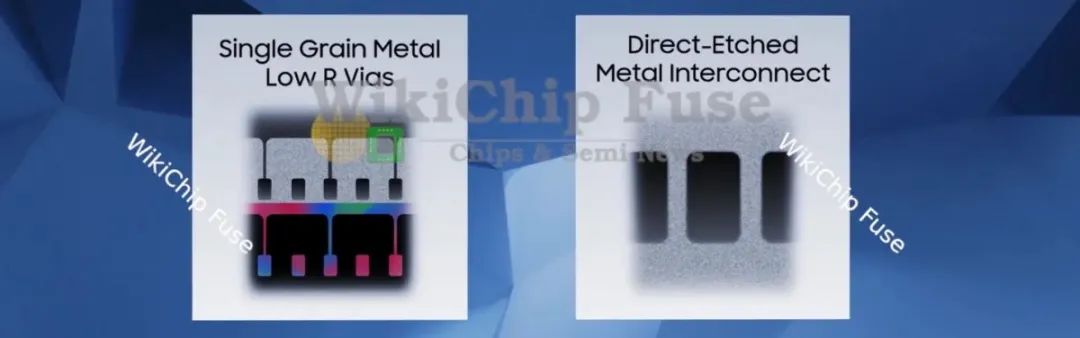

來源:WikiChip Fuse

有關三星2GAP的消息是最少的,我們能夠搜到有關三星2GAP的消息,大部分都是相關其2025年這個時間節點的。三星Foundry公開有關2GAP為數不多的信息是,2GAP會達成更高的晶體管密度——具體到晶體管結構上,MBCFET(也就是GAAFET)會多一片nanosheet,也就達成了總共4片nanosheet。這一點倒是和Intel的RibbonFET類似,目的都是進一步提升驅動電流。

來源:WikiChip Fuse

另外三星去年還曾提過正著力在部分金屬層堆棧的提升上,包括single grain metal(著力于低電阻),以及direct-etched metal interconnect。

不過在三星2GAP工藝上,我們還了解到一則信息:那就是三星2nm會采用名為“BSPDN”的技術,全稱backside power delivery network。三星是在SEDEX 2022上提到這則消息的。The Lec報道說BSPDN的概念最早是IMEC于2019年談到的;IEDM 2021上也有相關2nm工藝的paper提到過backside power delivery。當時這篇paper提到,對應的設計相比于frontside power delivery達成了44%的性能提升、32%的能效提升。

關注過我們此前對Intel制造工藝解讀的同學,對于這里的backside power delivery應該不會陌生——這也是未來半導體制造工藝的趨勢了。實際上Intel、臺積電的計劃表上也都能看到這項技術的實施。

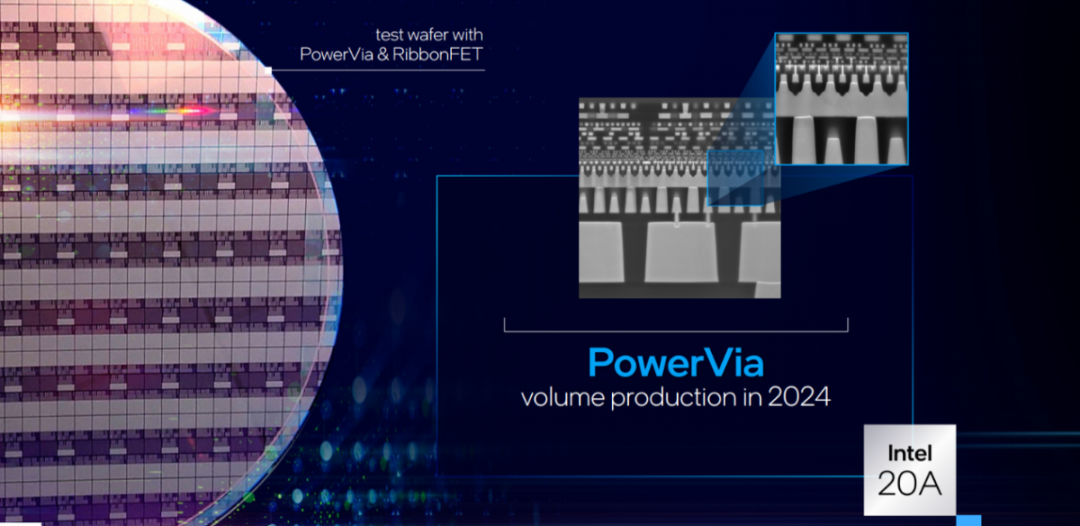

Intel在此前的技術介紹中談到過Intel 20A工藝準備采用一種名為PowerVia的技術,也就是backside power delivery。可能在具體實施上,三家的方案會存在一些差異。Intel的PowerVia是將供電網絡,或者叫電源軌全部移到晶體管另一側。傳統的互聯技術,供電和信號線路是混雜在一起的——或者說都在同一側,對性能和功耗都會有影響。

因為傳統方案在設計上需要確保沒有信號干擾,供電線路往往就是信號通路的干擾,而互聯信號通路本身也會對供電電阻產生影響。所以將兩者分開放到晶體管兩側,也就能夠解決問題。如此,供電網絡可以直接連接晶體管,不需要通過上方的互聯堆棧;而信號互聯也能更為密集,信號傳輸效率,包括延遲表現也有了提升;電力互聯部分電阻也減少了。最終也就實現了性能、功耗、面積的優化。

三星此前在SEDEX 2022上介紹說,和frontside power delivery網絡不同的是,BSPDN采用backside方式;frontside這一面放邏輯功能,而backside一面則用于供電或信號路由(signal routing)。主體上也是把供電網絡放到背面,嘗試解決傳統方案的各種路由擁塞問題。

就三家的放嘴炮程度(不是)來看,于backside power delivery這一技術上可能落后的是臺積電。從去年年中臺積電的歐洲技術研討會來看,2nm時代最初的N2工藝不會用上backside power delivery方案,或者叫backside power rails。臺積電當時沒說是什么原因。不過AnandTech此前報道說,臺積電發現這項技術會增加不少額外工藝步驟,臺積電期望在最初的GAAFET實施上避開這些環節。

臺積電N2缺失backside power delivery可能是N2的晶體管密度提升并不大的原因之一。2026年的N2P工藝才會用上這個技術,以期解決BOEL流程中via電阻增加的更多問題,當然也會對應的提升晶體管性能、降低功耗。將供電網絡和數據連接進行解耦,在過去這么多年來都是foundry廠的技術熱點。

只不過臺積電并未提到N2P將會帶來多大程度的性能、功耗表現、晶體管密度的提升。AnandTech說backside power rails能夠帶來“個位數功耗表現提升”和“兩位數的晶體管密度提升”——如此看來,N2P相比N2會是個比較大幅度的同代演進。

最后值得一提的是,從臺積電目前的計劃表來看,其N2工藝家族還有個N2X工藝——類似于N3時代的N3X,是個性能增強版工藝,主要面向HPC類別的應用,比如說高端CPU處理器。具體情況未知。

從前述所有資料來看,預期臺積電N2和2GAP最早與我們正式見面需要等到2026年,早如Intel 20A的問世起碼也得到2025年了——而且這些時間的可靠性都還相當值得懷疑。不過2nm時代的市場競爭或許會變得更加慘烈,不僅是因為器件新結構的全面變遷和技術迭代,還在于Intel和三星都有在2nm節點與臺積電一較高下的決心。

審核編輯 :李倩

-

臺積電

+關注

關注

43文章

5535瀏覽量

165701 -

工藝

+關注

關注

4文章

546瀏覽量

28696 -

半導體制造

+關注

關注

8文章

378瀏覽量

23982

原文標題:聊聊2025年要到來的2nm工藝

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

臺積電2nm芯片助力 蘋果把大招留給了iPhone18

日本Rapidus計劃2025年啟動2nm制程測試工廠

臺積電2nm芯片研發迎新突破

臺積電2nm芯片研發工作已步入正軌

今日看點丨傳臺積電2nm制程加速安裝設備;吉利汽車新一代雷神電混系統年內發布

蘋果欲優先獲取臺積電2nm產能,預計2024年安裝設備生產

臺積電2nm制程穩步推進,2025年將實現量產

臺積電首次提及 1.4nm 工藝技術,2nm 工藝按計劃 2025 年量產

今日看點丨臺積電首次提及 1.4nm 工藝技術,2nm 工藝按計劃 2025 年量產;消息稱字節跳動將取消下一代 VR 頭顯

2nm意味著什么?2nm何時到來?它與3nm有何不同?

臺積電有望2025年量產2nm芯片

2nm芯片什么時候出 2nm芯片手機有哪些

2nm芯片是什么意思 2nm芯片什么時候量產

聊聊2025年要到來的2nm工藝

聊聊2025年要到來的2nm工藝

評論