CDM(Charge Device Model),與MM與HBM一起作為ESD的三種類型之一。隨著IC工藝進(jìn)程的發(fā)展與自動(dòng)化生產(chǎn)流程的普及,CDM已經(jīng)取代MM與HBM成為芯片失效的主要靜電類型,目前CDM造成的失效占比遠(yuǎn)高于HBM與MM。而現(xiàn)階段的流程管理與高自動(dòng)化生產(chǎn)流程,能大幅度降低HBM與MM的發(fā)生概率,但是卻無法降低CDM的發(fā)生概率。隨著目前工藝結(jié)點(diǎn)的降低,CDM所造成的損害也日益嚴(yán)重。因?yàn)镃DM的自發(fā)特性,CDM防護(hù)已經(jīng)成為芯片設(shè)計(jì)中不得不考慮的指標(biāo)。除此之外隨著芯片在工業(yè),車規(guī),醫(yī)療等領(lǐng)域的大規(guī)模推廣,CDM防護(hù)能力業(yè)已成為很多領(lǐng)域的硬性指標(biāo)。目前CDM的防護(hù)也是業(yè)界所聚焦的設(shè)計(jì)難點(diǎn)。

一.CDM機(jī)理

筆者一直比較贊同陳東旸博士的觀點(diǎn):ESD作為一種普遍的自然現(xiàn)象,其背后是復(fù)雜的物理作用,需要從更深層次的角度去理解ESD的機(jī)理。而CDM作為一種自發(fā)性的放電行為,其背后機(jī)理也是需要從更微觀的角度進(jìn)行探討。

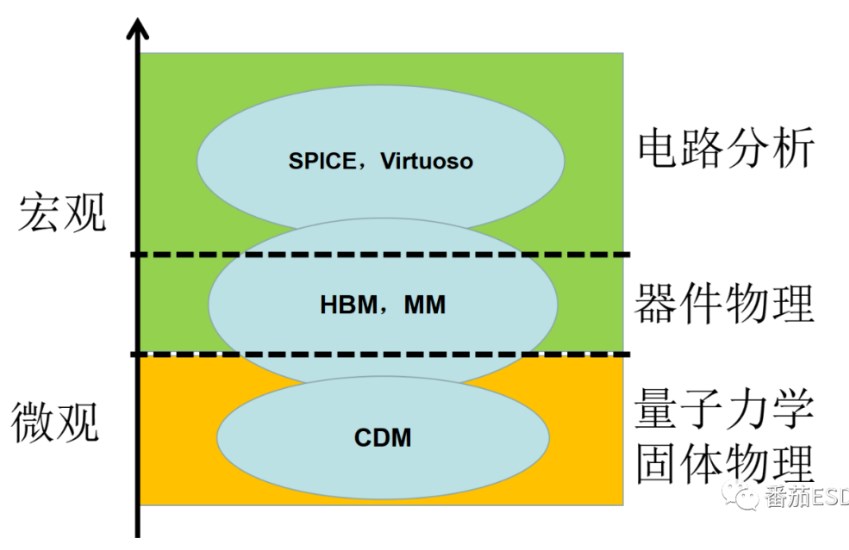

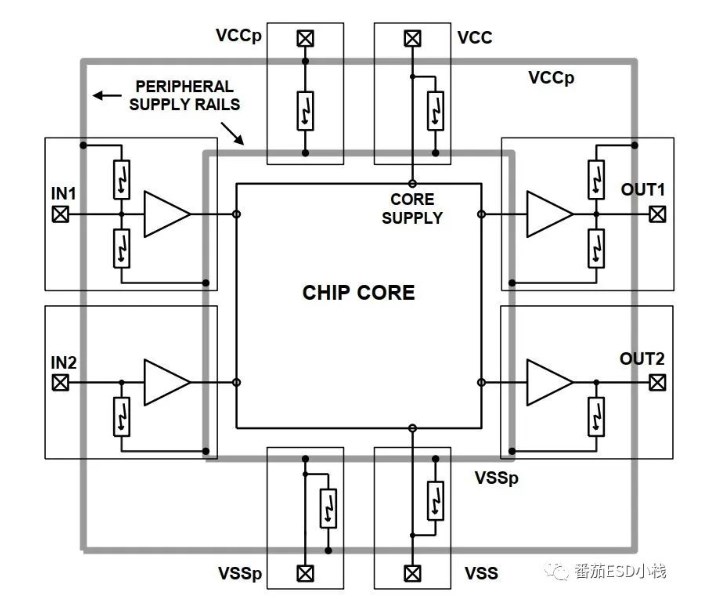

圖一.HBM,MM,CDM三種ESD的關(guān)系。

目前主流的SPICE等電路仿真軟件都是基于電路原理進(jìn)行仿真建模,最多將擬合后二級(jí)效應(yīng)代入修正。而HBM與MM等ESD事件需要對(duì)電場(chǎng)分布,能量分布等參數(shù)進(jìn)行建模分析,傳統(tǒng)電路仿真軟件已經(jīng)無能為力,此時(shí)需要Sentaurus和Silvaco等TCAD軟件進(jìn)行仿真建模。一方面為了仿真收斂會(huì)大幅度簡(jiǎn)化模型復(fù)雜度,另一方面,核心參數(shù)fab會(huì)模糊處理,從而造成仿真結(jié)果較為粗糙。而CDM的建模更加困難,因?yàn)镃DM的自發(fā)特性,其聚焦于材料內(nèi)部載流子的變化,所以針對(duì)CDM的建模仿真已經(jīng)進(jìn)入極其復(fù)雜的微觀領(lǐng)域。

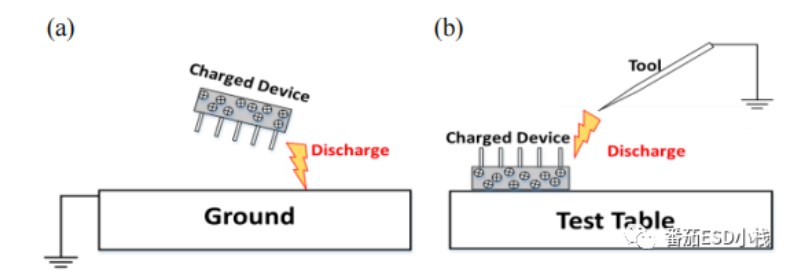

CDM是指芯片/裸片因?yàn)橥怆妶?chǎng),摩擦生電等因素其自身內(nèi)部積聚了大量電荷,當(dāng)與接地導(dǎo)體接觸后(這里的接地是相對(duì)概率,只要電勢(shì)相對(duì)夠低便可認(rèn)為是接地,比如接地電位或者金屬機(jī)殼,工具等),大量電荷從體系逸出,此時(shí)會(huì)在極短的時(shí)間內(nèi)產(chǎn)生靜電脈沖,這個(gè)脈沖就是CDM放電。CDM的放電特點(diǎn)就是時(shí)間短,電流脈沖高,波形不確定。

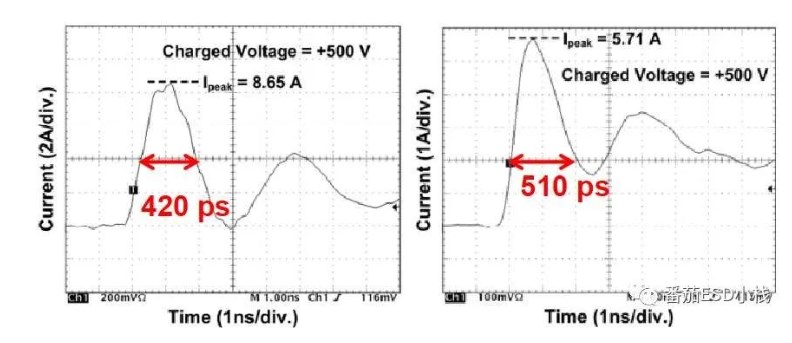

圖二.不同芯片的CDM波形圖。

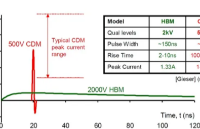

從圖中可以看出,CDM的脈沖持續(xù)時(shí)間很短,電流峰值很大。而且不同的芯片/裸片因?yàn)榻Y(jié)構(gòu),電容等參數(shù)的差異,相同條件下不同芯片的CDM波形也會(huì)有較大差異。由原理得知CDM的特點(diǎn):

自發(fā)性。CDM放電是器件在外界因素的擾動(dòng)下本身儲(chǔ)存了大量帶電載流子,而芯片/裸片本身的結(jié)構(gòu)和電容決定了儲(chǔ)存在器件電荷的電量和放電持續(xù)時(shí)間,所以CDM波形是由芯片自身決定,其不像HBM和MM一樣有固定的波形。

由內(nèi)到外。HBM和MM都是由外而內(nèi)的ESD事件,靜電流是由芯片外部灌入內(nèi)部,所以針對(duì)HBM和MM的防護(hù)主要集中在IO。而CDM反之,CDM是器件內(nèi)部向外部放電,所以針對(duì)CDM的防護(hù)相較于其他類型的ESD防護(hù)設(shè)計(jì)難度更高。因?yàn)槊}沖時(shí)間短,所以CDM防護(hù)的重點(diǎn)是建立低寄生電容的泄放通道,CDM幅值雖然很高,但是其防護(hù)電路不需要很大的面積,只需要能及時(shí)將積聚在半導(dǎo)體襯底材料內(nèi)的載流子泄放出去。

CDM主要誘因之一是外部電場(chǎng)作用,整個(gè)芯片或者裸片都處在外界電場(chǎng)作用下,此時(shí)半導(dǎo)體內(nèi)部載流子在外界電場(chǎng)下會(huì)重新分布,為了維持電中性條件,半導(dǎo)體內(nèi)部會(huì)產(chǎn)生自發(fā)極化電場(chǎng)。在極化電場(chǎng)與外電場(chǎng)的相互作用下,整個(gè)體系還維持電中性平衡,此時(shí)如果相對(duì)接地的金屬與芯片或者裸片接觸,大量載流子流入/出導(dǎo)體,形成自發(fā)的CDM放電。

圖三.CDM原理示意圖。

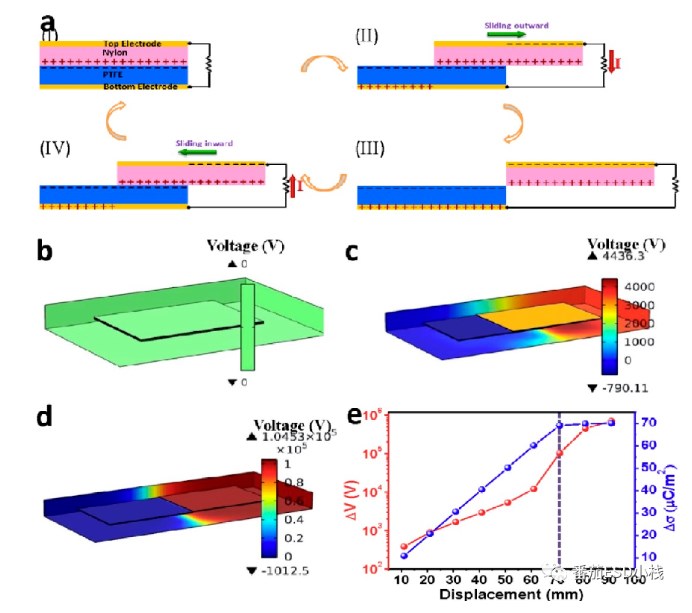

從微觀上說,無論是否存在外電場(chǎng)誘發(fā),半導(dǎo)體材料自身時(shí)刻處在一個(gè)動(dòng)態(tài)平衡的過程中。無時(shí)無刻都有電子逸出和復(fù)合。摩擦生電與受熱不均也會(huì)破壞體系的電中性條件,形成靜電。其中當(dāng)芯片/裸片之間相互碰撞或者接觸,在接觸面會(huì)產(chǎn)生異質(zhì)結(jié)或者金半接觸,載流子會(huì)重新分布,從而形成極化電場(chǎng),此時(shí)載流子分布產(chǎn)生梯度,如果與電位較低的導(dǎo)體接觸,大量的載流子從芯片內(nèi)部轉(zhuǎn)移,從而造成CDM靜電。而溫度分布的不均,也會(huì)造成CDM靜電,不同溫度會(huì)造成費(fèi)米能級(jí)不同,從而造成極化電場(chǎng)。

圖四.摩擦生電示意圖。

簡(jiǎn)而言之便是因?yàn)楦鞣N外部環(huán)境的變化,改變了半導(dǎo)體材料的電中性條件,使得載流子分布不均,空穴與電子各自積聚在不同區(qū)域,通過內(nèi)建電場(chǎng)維持體系平衡。當(dāng)與相對(duì)接地的金屬接觸后,這部分聚集的載流子逸出體系,造成CDM放電。因此CDM在生產(chǎn)制造、封裝、測(cè)試、運(yùn)輸過程中是極難被避免的。而隨著工藝結(jié)點(diǎn)的降低,芯片對(duì)CDM的耐受程度也隨之降低,CDM的失效基本都集中在柵氧化層。

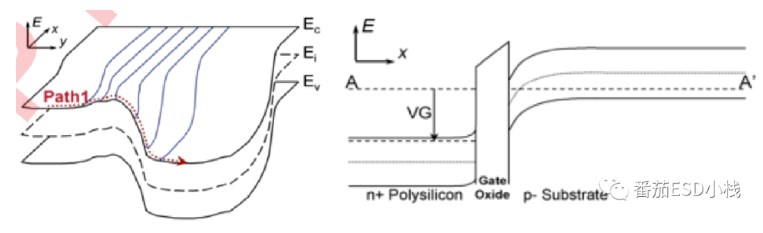

圖五.MOS管中電荷積聚的能帶示意圖。

由圖中可以看出,載流子的積聚會(huì)改變半導(dǎo)體材料的費(fèi)米能級(jí)分布(電子越多,費(fèi)米能級(jí)越低,空穴越多,費(fèi)米能級(jí)越高。)而當(dāng)接地的金屬一旦與柵極接觸,金屬功函數(shù)與費(fèi)米能級(jí)的電勢(shì)差會(huì)產(chǎn)生極化電場(chǎng),如果該電場(chǎng)過強(qiáng),就會(huì)造成柵氧化層的損壞。所以CDM的失效主要集中在柵極,CDM造成的柵極失效位置也受很多因素影響。(下期會(huì)專門講解)

二.CDM的差異

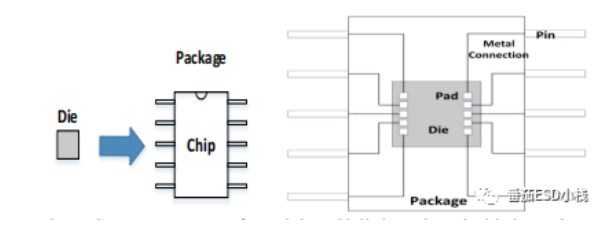

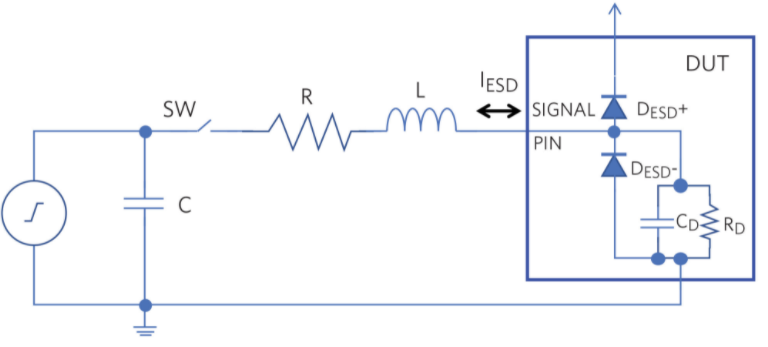

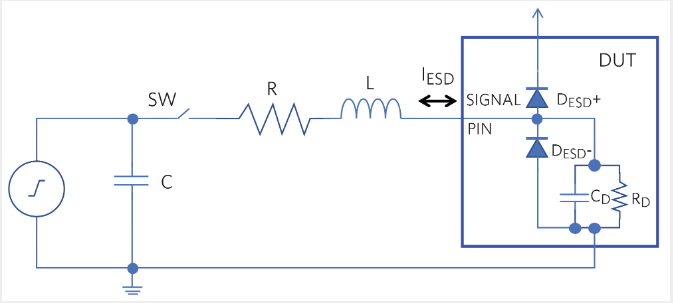

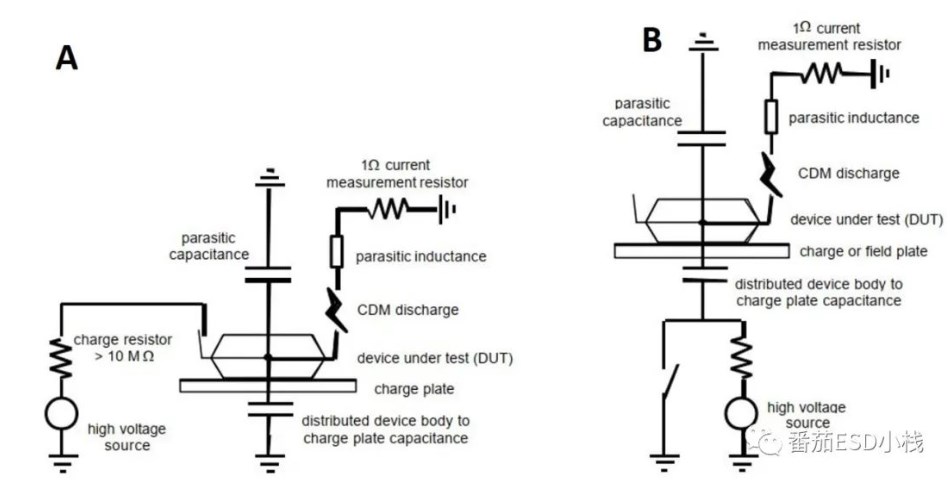

目前CDM測(cè)試有兩種:一種是封裝后的Chip-Level,另一種是未進(jìn)行封裝的Silicon-Die。

圖六.芯片封裝示意圖。

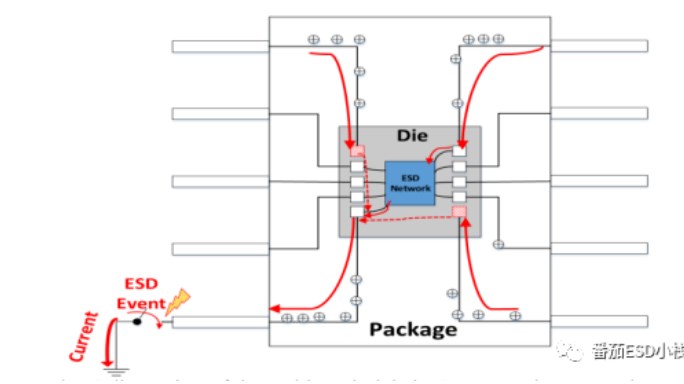

封裝后芯片與未封裝的裸片其CDM機(jī)理存在一定差異。封裝后的芯片因?yàn)榭蚣芘c金屬互連的存在,摩擦生電或者外界電場(chǎng)產(chǎn)生的電荷會(huì)被存儲(chǔ)在框架中。而未封裝的裸片,這部分電荷會(huì)被存儲(chǔ)在襯底半導(dǎo)體材料中。如圖所示,當(dāng)接地金屬與封裝后的芯片接觸,大量電荷或者直接通過金屬互連從體系轉(zhuǎn)移出去,或者通過內(nèi)部芯片的PAD進(jìn)行泄放。

圖七.封裝芯片CDM示意圖。

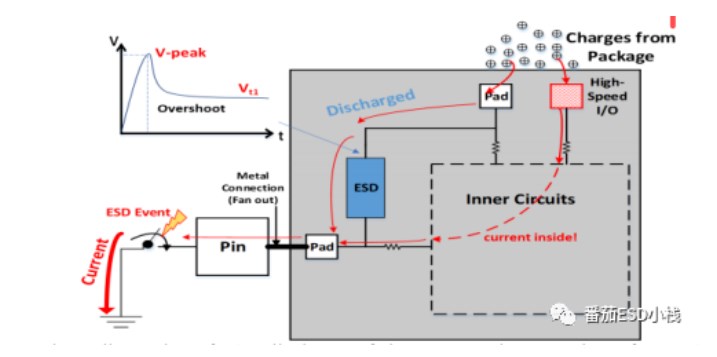

而存儲(chǔ)在框架內(nèi)的電荷也不一定會(huì)老老實(shí)實(shí)呆在一個(gè)地方,其也有可能通過金屬互連在無接地金屬觸發(fā)的情況下在芯片內(nèi)部亂竄。如圖所示,針對(duì)由封裝流入內(nèi)部的電荷,可以看成是一種“由外到內(nèi)”的ESD事件,這種由外到內(nèi)的ESD電流便類似于HBM和MM,傳統(tǒng)的ESD防護(hù)措施能發(fā)揮一定作用。而未封裝的裸片,其CDM電荷儲(chǔ)存在襯底,其放電路徑是由內(nèi)到外,傳統(tǒng)的HBM防護(hù)措施可能會(huì)失效。

圖八.封裝電荷流入內(nèi)部芯片。

所以封裝也是影響CDM能力的一大因素,選擇合適的封裝與bonding方案也能提高芯片的CDM能力。

-

ESD

+關(guān)注

關(guān)注

48文章

2012瀏覽量

172736 -

CDM

+關(guān)注

關(guān)注

0文章

30瀏覽量

12220 -

寄生電容

+關(guān)注

關(guān)注

1文章

291瀏覽量

19192 -

esd防護(hù)

+關(guān)注

關(guān)注

1文章

31瀏覽量

12431

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

繞組磁勢(shì)諧波產(chǎn)生的原因和機(jī)理

電容的失效模式和失效機(jī)理

淺談Silabs 的Flash 單片機(jī)丟失程序的原因及對(duì)策

什么是小尺寸集成電路CDM測(cè)試?

硬件高手提升技能,解決運(yùn)算放大器CDM難以測(cè)量問題

小尺寸集成電路CDM測(cè)試

CDM6系列斷路器操作指南

日本CDM 8.0正式版已經(jīng)發(fā)布下載

PCB失效或不良的準(zhǔn)確原因和機(jī)理資料下載

HBM、MM和CDM測(cè)試的基礎(chǔ)知識(shí)

HBM、MM和CDM測(cè)試基礎(chǔ)

CDM的測(cè)試與失效分析

CDM防護(hù)措施以及設(shè)計(jì)思路

什么是AEC-Q-CDM測(cè)試?

淺談CDM的原因與機(jī)理

淺談CDM的原因與機(jī)理

評(píng)論