在芯片級ESD防護中最普遍的器件就是增強型NMOS(下文中的NMOS都是增強型),接下來的幾期會淺談一下NMOS在ESD防護中的作用與設(shè)計思路。

目前主流的ESD-NMOS有兩大設(shè)計思路:GGNMOS(Gate Ground NMOS),GCNMOS(Gate Couple NMOS)。其中GGNMOS最為常見,設(shè)計最為簡單。但是其巨大的寄生電容使其在serdes與AD-DA等領(lǐng)域應(yīng)用受限。而GCNMOS與GGNMOS完全是兩種工作原理,GCNMOS的應(yīng)用場景更為廣闊,使用更為靈活,且相較于GGNMOS晦澀復雜且玄學的器件級仿真,GCNMOS可以在cadence中進行電路級仿真,使得其在電路設(shè)計人員眼中的可靠性大幅提高(GGNMOS也一樣靠譜,但是仿不出來結(jié)果。。。沒法交差。。。。)

GGNMOS與GCNMOS其本質(zhì)的差異是工作原理的不同,這期就先從GGNMOS講起。

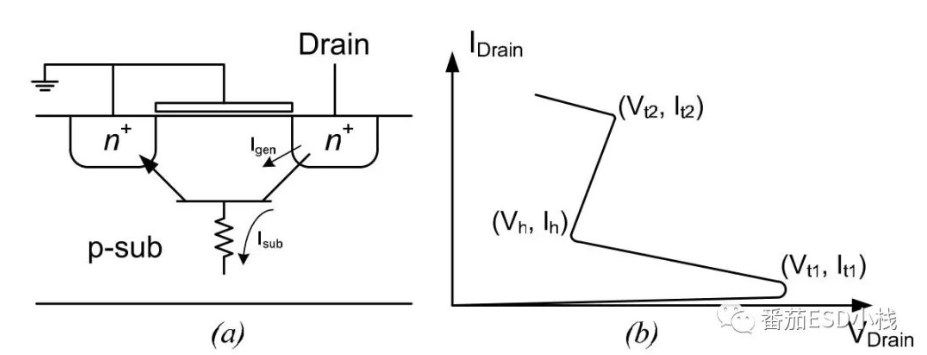

圖一.GGNMOS工作原理與TLP曲線

GGNMOS工作原理:

GGNMOS結(jié)構(gòu)如圖所示:柵極接地,整個管子處在常關(guān)態(tài),導電溝道關(guān)閉。通過調(diào)整Drain與P-sub的摻雜濃度與拓撲結(jié)構(gòu)使其Breakdown Voltage位于ESD Design Window內(nèi),要高于正常工作電壓。在正常工作的情況下整個GGNMOS處于高阻態(tài),并聯(lián)在PAD與GND軌間,不會影響電路的正常工作狀態(tài)。當ESD電流從PAD進入IC后,整個回路電壓提升,當電壓達到Drain(N)/Sub(P)的反偏擊穿電壓后,器件體內(nèi)Drain/P-sub會發(fā)生雪崩擊穿,大量雪崩擊穿產(chǎn)生的載流子通過襯底電阻,產(chǎn)生壓降。當Vsub-source壓降》0.7V后,在器件體內(nèi)由Drain—Psub—Source構(gòu)成的NPN寄生三極管完全導通,此時Drain的電位對應(yīng)TLP曲線中的(Vt1,It1)點,該點電壓稱為trigger voltage。

當發(fā)生trigger后,整個GGNMOS表現(xiàn)出負阻行為,稱為snap-back,發(fā)生snap-back是由于Drain—Psub—Source構(gòu)成的NPN寄生三極管導通后,來自source端的漂移載流子數(shù)目開始增多,導電機制的變化使得維持相同電流的偏壓大幅度降低,器件出現(xiàn)負阻特性。當電壓降低到Vh,電流提升到Ih。(Vh,Ih)被稱為holding voltage,這一點說明器件中電流基本是由漂移載流子提供,雪崩擊穿產(chǎn)生的載流子可忽略不計。此時負阻特性結(jié)束,整個器件發(fā)生電導調(diào)制效應(yīng),可以理解為整個器件完全導通,IV特性與電阻相似。隨著電壓與電流的增加,當達到(Vt2,It2)點,整個器件會發(fā)生二次擊穿,表明器件燒毀。

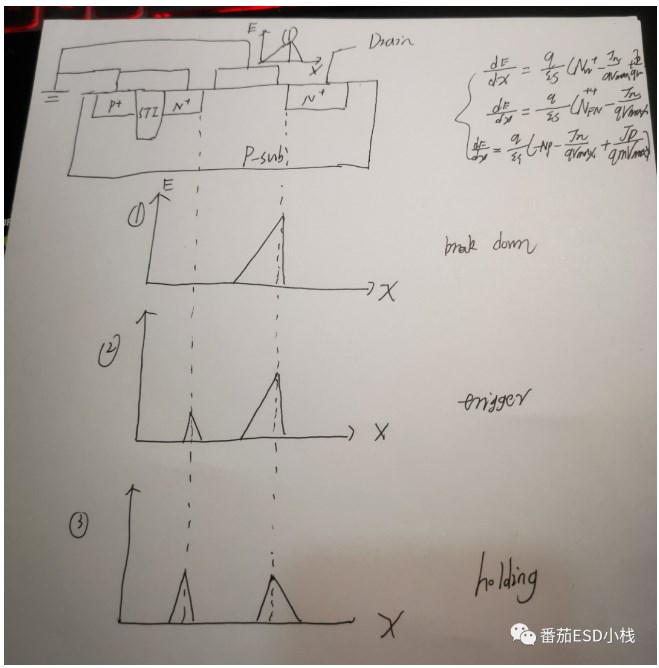

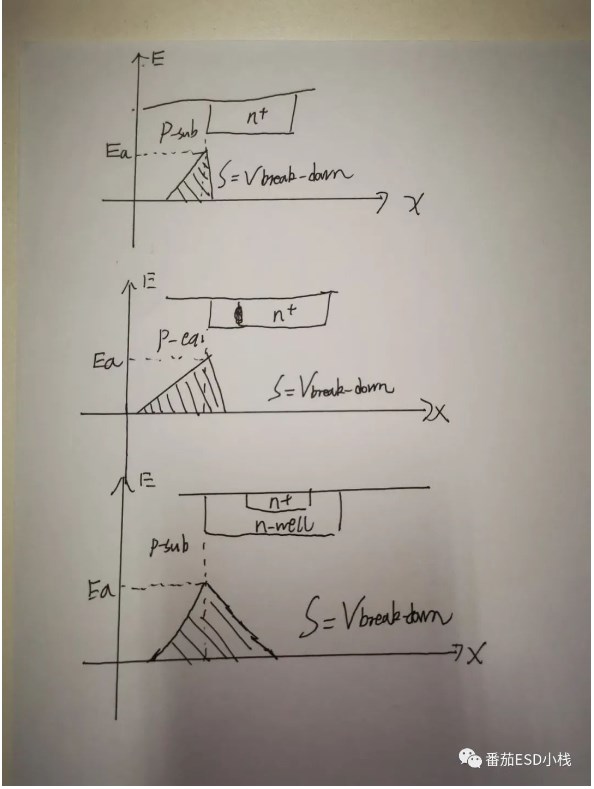

圖二.GGNMOS不同狀態(tài)下的電場分布。

圖二給出了電場分布的大致示意圖,并給出大注入情況下的二維橫向泊松方程。考慮到三維空間下,在縱向也會產(chǎn)生電場。外加Krik效應(yīng)與Early效應(yīng),真實狀態(tài)的電場分布會極其復雜。

總結(jié):ESD電流會造成Drain與襯底P-sub的反偏結(jié)擊穿,此時器件中以雪崩擊穿載流子為主,襯底電阻在雪崩載流子作用下產(chǎn)生偏壓,Drain—Psub—Source構(gòu)成的NPN寄生三極管完全導通,此時電壓稱為Trigger Voltage表明器件開始發(fā)生snap-back特性,導電機制發(fā)生轉(zhuǎn)變,當偏移載流子提供所有的電流后,電壓會降低,該點的電壓稱為Holding Voltage,之后器件的電路特性類似于電阻,直至二次擊穿,器件損壞。

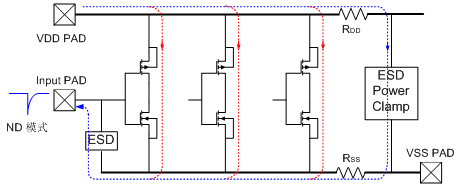

GGNMOS設(shè)計思路:

用于ESD防護的NMOS與常規(guī)NMOS現(xiàn)階段已經(jīng)產(chǎn)生了結(jié)構(gòu)差異。目前最主要的工藝差異有LDD注入和Silicide層,ESD防護器件目前會去除這兩項工藝,同時GGNMOS會將Drain拉寬。

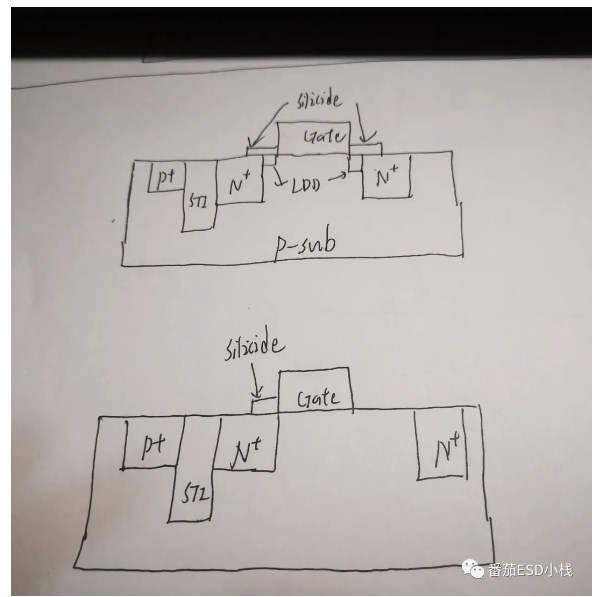

圖三。普通NMOS與ESD-NMOS的區(qū)別。

LDD在普通NMOS中便于表面溝道的形成,但是在GGNMOS中會造成這部分耐壓過低,電場過于集中,不利于器件魯棒性。同樣Silicide是降低源漏區(qū)的表面電阻,便于載流子在表面流動,而GGNMOS反而需要載流子往體里流動,通過體內(nèi)的寄生三極管流出,所以專門的Silicide block mask 遮擋Silicide注入。

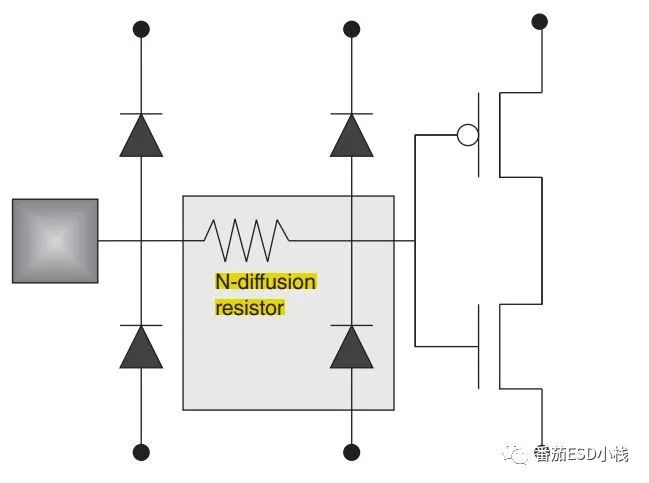

目前大部分snap-back型ESD器件的設(shè)計思路無外乎三點:trigger Voltage ,holdding Voltage,Second breakdown Voltage 。GGNMOS也是如此。針對trigger Voltage主要是調(diào)整反偏PN結(jié)的雪崩擊穿電壓。一種設(shè)計思路是改變兩邊的摻雜濃度:線性緩變結(jié)的反向擊穿電壓會高于突變結(jié),濃度越低反向擊穿電壓越高。

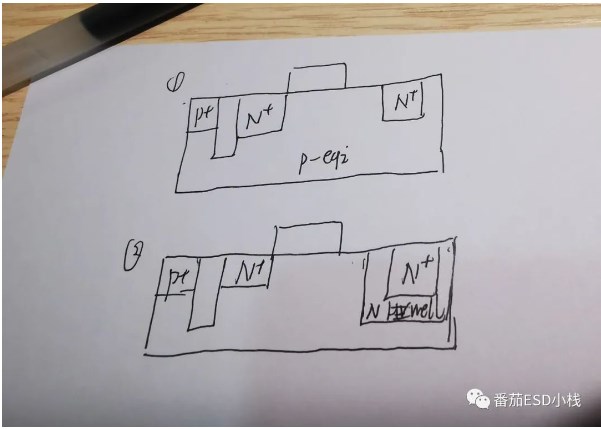

圖四。GGNMOS漏端濃度調(diào)節(jié)方法。

如圖所示,調(diào)節(jié)方法要么改變P-sub濃度,在某些外延層工藝中襯底替換為P-eqi,要么將N+放入Nwell中。通過這兩種思路來改變結(jié)擊穿電壓。

-

三極管

+關(guān)注

關(guān)注

142文章

3600瀏覽量

121661 -

ESD

+關(guān)注

關(guān)注

48文章

2012瀏覽量

172782 -

LDD接口

+關(guān)注

關(guān)注

0文章

6瀏覽量

7435 -

NPN

+關(guān)注

關(guān)注

11文章

2640瀏覽量

47184 -

NMOS管

+關(guān)注

關(guān)注

2文章

120瀏覽量

5398

發(fā)布評論請先 登錄

相關(guān)推薦

多軸運動控制板ESD雷擊浪涌防護靜電整改測試案例分享#電路設(shè)計 #電子元器件 #ESD防護 #浪涌保護器

淺析ESD 防護與ESD 防護器件

電路級靜電防護設(shè)計技巧與ESD防護方法

【轉(zhuǎn)】電路級靜電防護設(shè)計技巧與ESD防護方法

電路級靜電防護設(shè)計技巧與ESD防護方法

探索ESD防護器件的原理及選用

USB3.0接口的ESD防護設(shè)計

如何進行ESD防護?

AT32 USB接口ESD防護設(shè)計指南

ESD防護的PCB設(shè)計準則

淺談ESD防護設(shè)計—NMOS的妙用(二)

全芯片ESD防護網(wǎng)絡(luò)

淺談ESD防護設(shè)計—NMOS的妙用(一)

淺談ESD防護設(shè)計—NMOS的妙用(一)

評論