問題描述

客戶在調試QSPI模塊過程中,將TC397的QSPI模塊的CPOL位設置為1,但是示波器顯示時鐘引腳輸出信號的空閑狀態并不是高電平,在debug模式下,可觀察到CPOL位已設置為1,這是怎么回事呢?

圖1

設置TC397的QSPI模塊工作在CPOL=1, CPH =1協議模式

解決過程

SpiIf_initChannelConfig()函數在初始化QSPI channel時,提供了很多配置參數項,其中就有clockPolarity,但是單單設置clockPolarity= SpiIf_ClockPolarity_idleHigh,雖然會將CPOL位設置為1,但是捕獲的波形顯示空閑狀態電平并未變成高電平。

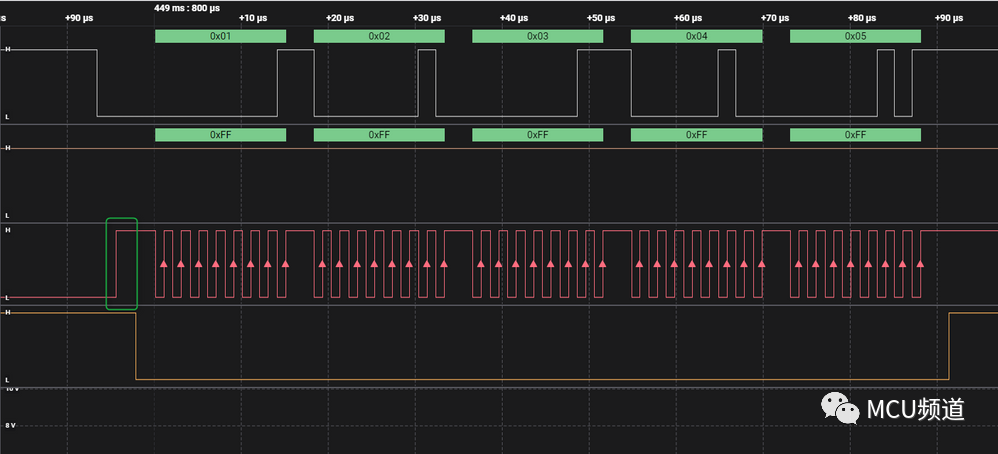

這是由于SpiIf_initChannelConfig()函數的默認參數項設置IDLE時序階段時長為0,使得幀傳輸間隙缺少IDLE時序階段,所以需要設置csInactiveDelay > 0(如下所示)來插入IDLE時序階段,如下圖所示。

voidSpiIf_initChannelConfig(SpiIf_ChConfig*config,SpiIf*driver)

{

config->driver=driver;

config->baudrate=0;

config->mode.enabled=1;

config->mode.autoCS=1;

config->mode.loopback=0;

config->mode.clockPolarity=SpiIf_ClockPolarity_idleHigh;

config->mode.shiftClock=SpiIf_ShiftClock_shiftTransmitDataOnLeadingEdge;

config->mode.dataHeading=SpiIf_DataHeading_msbFirst;

config->mode.dataWidth=8;

config->mode.csActiveLevel=Ifx_ActiveState_low;

config->mode.csLeadDelay=SpiIf_SlsoTiming_0;

config->mode.csTrailDelay=SpiIf_SlsoTiming_0;

config->mode.csInactiveDelay=SpiIf_SlsoTiming_2;

config->mode.parityCheck=0;

config->mode.parityMode=Ifx_ParityMode_even;

config->errorChecks.baudrate=0;

config->errorChecks.phase=0;

config->errorChecks.receive=0;

config->errorChecks.transmit=0;

}

圖2

審核編輯:劉清

-

示波器

+關注

關注

113文章

6190瀏覽量

184522 -

QSPI

+關注

關注

0文章

41瀏覽量

12180 -

CPOL

+關注

關注

0文章

9瀏覽量

10032

原文標題:如何設置TC397的QSPI模塊工作在CPOL=1, CPH =1協議模式

文章出處:【微信號:MCU頻道,微信公眾號:MCU頻道】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何設置TC397的QSPI模塊工作在CPH =1協議模式?

如何設置TC397的QSPI模塊工作在CPH =1協議模式?

評論