作者:付漢杰 hankf@amd.com

文章來源:博客園

測試環境

參考文檔

xtp226-ac701-multiboot-c-2015-1.pdf

ug470_7Series_Config.pdf

xapp1247-multiboot-spi.pdf

ug952-ac701-a7-eval-bd.pdf

ug1579-microblaze-embedded-design.pdf

Vitis Embedded Software Debugging Guide (UG1515)

測試單板

ac701

測試工具

Vivado 2022.2

Vitis 2022.2

Mutliboot

UG470 Reconfiguration and MultiBoot Overview

UG470中的介紹如下

The 7 series FPGAs MultiBoot and fallback features support updating systems in the field. Bitstream images can be upgraded dynamically in the field. The FPGA MultiBoot feature enables switching between images on the fly. When an error is detected during the MultiBoot configuration process, the FPGA can trigger a fallback feature that ensures a known good design can be loaded into the device.

AMD FPGA支持的MultiBoot特性,可以使FPGA先嘗試啟動最新的配置(bit)文件,后續稱為Update Bit。如果最新的配置文件出錯,再回退到安全的出廠版本的配置(bit)文件,后續稱為Golden Bit。

MultiBoot特性有兩種方式使能。第一種方式是在配置(bit)文件里嵌入IPROG命令,觸發MultiBoot特性。第二種方式是通過AXI HWICAP寫入IPROG命令,觸發MultiBoot特性。

配置(bit)文件嵌入IPROG命令

建議閱讀XAPP1247 的 “Table 1: MultiBoot Bitstream Properties”。

MultiBoot Bitstream Properties

在工程的約束文件中,加入下列設置,會自動在配置(bit)文件中插入IPROG命令。

set_property BITSTREAM.CONFIG.CONFIGFALLBACK Enable [current_design] set_property BITSTREAM.CONFIG.NEXT_CONFIG_ADDR 0x600000 [current_design] set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

上述約束的NEXT_CONFIG_ADDR,根據實際的Flash分配情況設置。

對于AC701單板,也建議添加下列約束。

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design] set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design] set_property BITSTREAM.CONFIG.EXTMASTERCCLK_EN div-1 [current_design] set_property BITSTREAM.CONFIG.SPI_FALL_EDGE YES [current_design] set_property CONFIG_MODE SPIx4 [current_design] set_property CONFIG_VOLTAGE 3.3 [current_design] set_property CFGBVS VCCO [current_design]

通過AXI HWICAP寫入IPROG命令

AMD提供IP,支持通過AXI總線,訪問ICAPE。

xtp226 也提供了硬件、軟件設計,它支持通過AXI HWICAP寫入IPROG命令,觸發FPGA重新加載。

golden_iprog_spi中的golden.c, 通過讀取AXI GPIO 0的狀態,決定FPGA重新加載時使用的bit文件。AXI GPIO 0對應到AC701上的SW2。AXI GPIO 0的bit-0,也就是SW2的靠角落(DS23、SW4)的開關1在1的狀態(靠液晶屏、7A200T芯片側),則加載0x400000的bit文件。AXI GPIO 0的bit-0為0, bit-3為1(SW2的開關4)在1的狀態,則加載0x800000的bit文件。

status = GpioInputExample(XPAR_AXI_GPIO_0_DEVICE_ID, &DataRead);

if (status == 0) {

xil_printf("GpioInput Read data:0x%X

", DataRead);

if ( (DataRead & 0x00000001) == 0x00000001 )

{

fpga_iprog(0x00400000); // IPROG to GOOD BITSTREAM ,must match address in .prm

}

if ( (DataRead & 0x00000008) == 0x00000008 )

{

fpga_iprog(0x00800000); // IPROG to cause configuration error

}

}

else {

print("GpioInput FAILED.

");

}

對比

第一種方式,通過配置(bit)文件嵌入IPROG命令,實現最簡單,占用資源也最少。但是只能支持一個Update Bit文件。

第二種方式,通過AXI HWICAP寫入IPROG命令,在下發IPROG命令前,可以任意指定Flash地址,非常靈活。但是需要嵌入MicroBlaze和AXI HWICAP,需要占用部分FPGA資源,也需要一點軟件開發。

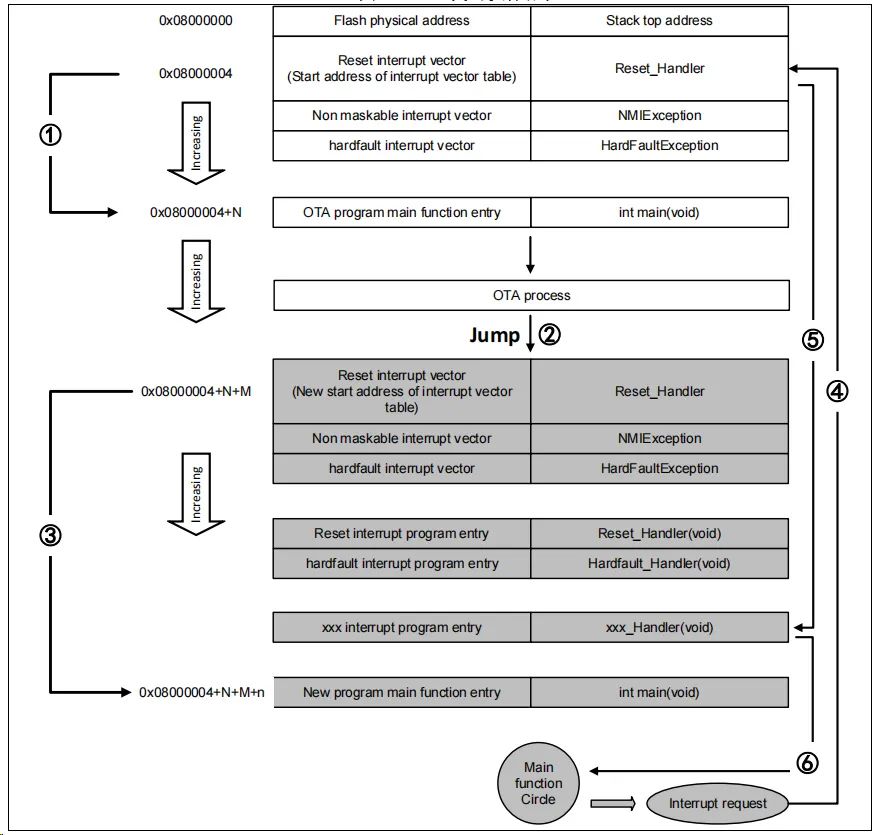

Artix FPGA OTA 在線升級的流程

首先分配Flash的存儲空間。Flash里 0x0 地址存放Golden Bit;Flash里 0x400000 地址存放 Update Bit;其中0x400000需要根據壓縮后的bit文件大小修改。

因為生成Golden Bit時,使用了屬性“BITSTREAM.CONFIG.NEXT_CONFIG_ADDR”, Golden Bit啟動后會自動加載Update Bit。

因為生成Golden/Update Bit時,使用了屬性“BITSTREAM.CONFIG.CONFIGFALLBACK”, 任何Bit失敗后,都會自動加載Golden Bit。

Golden bit和 Update bit內部都集成MicroBlaze、hwicap和Quad SPI Controller,都有在線升級bit的能力。

a. MicroBlaze通過Ethernet、PCIe、UART等,從外部獲得新的Update Bit。

b. MicroBlaze將新的Update Bit寫入Quad SPI的0x400000并校驗

c. MicroBlaze寫IProg命令到HWICAP,重啟動FPGA

d. FPGA使用新的Update Bit配置,之后Update Bit開始工作。

如果后來芯片斷電之后再上電,Update Bit能直接加載Update Bit。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1620文章

21510瀏覽量

598951 -

amd

+關注

關注

25文章

5376瀏覽量

133382 -

OTA

+關注

關注

7文章

552瀏覽量

34983 -

bit

+關注

關注

0文章

47瀏覽量

31934 -

Vivado

+關注

關注

19文章

797瀏覽量

65855

原文標題:【干貨分享】AMD Artix 7 FPGA OTA 在線升級的實現

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【Artix-7 50T FPGA試用體驗】xilxin Artix-7 系列FPGA相關特性

STM32 OTA升級如何實現呢

Xilinx Artix-7系列FPGA教程資料及設計實例_Artix 7開發板電路圖和例程

如何使用Artix-7 FPGA減少功耗

Artix-7 ARTY FPGA評估套件的演示

digilent Nexys 4:Artix-7 FPGA訓練板介紹

在線升級 | 物聯網中的OTA升級原理

在Artix 7 FPGA上使用Vivado的組合邏輯與順序邏輯

AMD Artix 7 FPGA OTA在線升級的實現

AMD Artix 7 FPGA OTA在線升級的實現

評論