什么是阻抗?(Impedance )

具有電阻、電感和電容的電路里,對交流電所起的阻礙作用叫做阻抗。阻抗常用Z表示。阻抗由電阻、感抗和容抗三者組成,但不是三者簡單相加。 阻抗的單位是歐。

對于一個具體電路,阻抗不是不變的,而是隨著頻率變化而變化。在電阻、電感和電容串聯電路中,電路的阻抗一般來說比電阻大。也就是阻抗減小到最小值。在電感和電容并聯電路中,諧振的時候阻抗增加到最大值,這和串聯電路相反。

阻抗匹配在高頻設計中是一個常用的概念,這篇文章對這個“阻抗匹配”進行了比較好的解析。回答了什么是阻抗匹配。

****什么是阻抗 匹配 (Impedance matching)?

是微波電子學里的一部分,主要用于傳輸線上,來達至所有高頻的微波信號皆能傳至負載點的目的,不會有信號反射回來源點,從而提升能源效益。

大體上,阻抗匹配有兩種,一種是透過改變阻抗力(lumped-circuit matching),另一種則是調整傳輸線的波長(transmission line matching)。

為什么要做阻抗匹配?

信號或廣泛電能在傳輸過程中,為實現信號的無反射傳輸或最大功率傳輸,要求電路連接實現阻抗匹配。阻抗匹配關系著系統的整體性能,實現匹配可使系統性能達到最優。阻抗匹配的概念應用范圍廣泛,阻抗匹配常見于各級放大電路之間,放大電路與負載之間,信號與傳輸電路之間,微波電路與系統的設計中,無論是有源還是無源,都必須考慮匹配問題,根本原因是在低頻電路中是電壓與電流,而高頻中是導行電磁波不匹配就會發生嚴重的反射,損壞儀器和設備。

阻抗匹配的基本原理是什么?

阻抗匹配是使微波電路或是系統的反射,載行波盡量接近行波狀態的技術措施。阻抗匹配分為兩大類:

(1)負載與傳輸線之間的阻抗匹配,使負載無反射。方法是接入匹配裝置使輸入阻抗和特性阻抗相等。

(2)信號源與傳輸線之間匹配,分為兩種情況:1)使信號源無反射,方法是接入信號源與傳輸線之間接入匹配裝置。2)信號源共軛匹配,方法是信號源與被匹配電路之間接入匹配裝置,這種情況下多屬于有源電路設計。

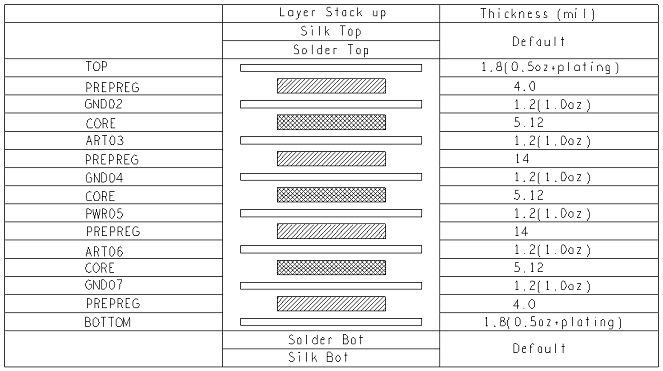

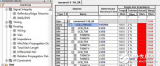

阻抗計算方法(以一個八層板為例)

下面以如圖1所示的八層板為例來介紹下相關阻抗的計算方法

圖1

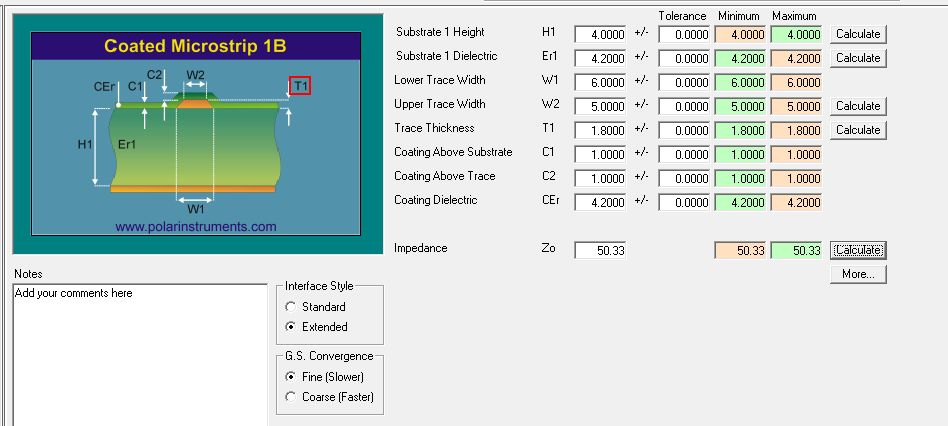

1 **. **微帶線阻抗計算

(1)表層(Top/Bot層)參考第二層,單端阻抗選用CoatedMicrostrip 1B模型,單端50歐姆阻抗計算方法如圖2所示,最后得到表層50歐姆單端線寬為6mil。

圖2表層(Top/Bot層)單端阻抗計算

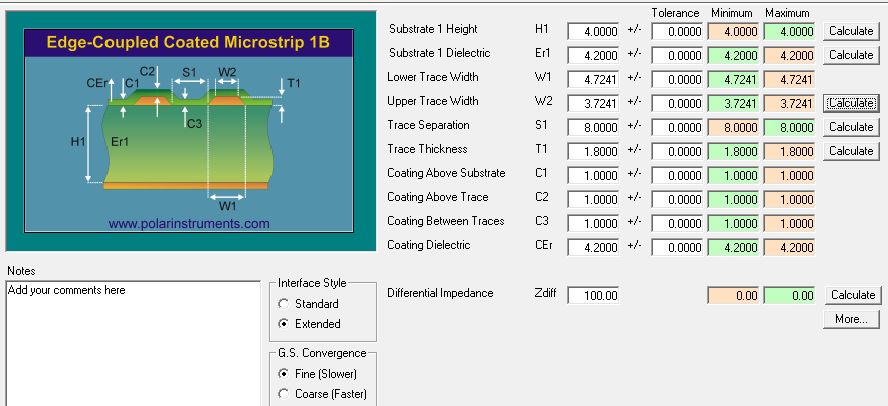

(2)表層差分阻抗選用Edge-CoupledCoated Microstrip 1B模型,差分100歐姆阻抗計算如圖3所示 ,最后得到的表層100歐姆差分線寬線距為4.7/8mil。

圖3 表層(Top/Bot層)差分阻抗計算

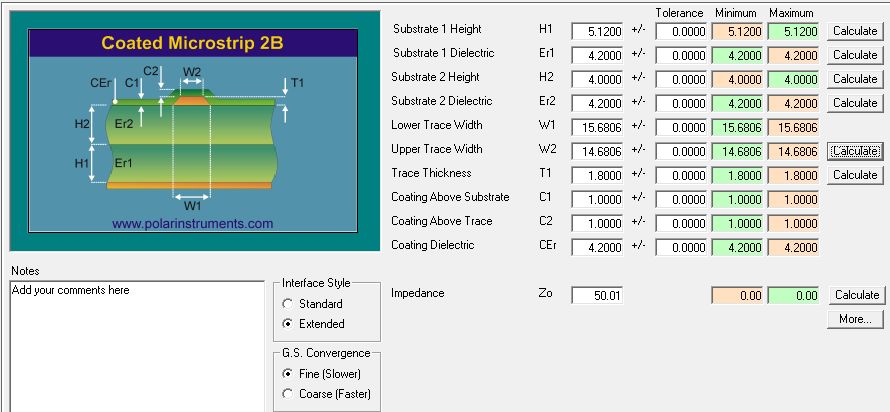

(3)表層(Top/Bot層)射頻信號50歐姆阻抗的計算:

因為射頻信號要有足夠寬的線寬,在阻抗不變的情況下,加大線寬就必須增加阻抗線到參考層的距離,所以50歐姆射頻信號要做隔層參考也就是參考第三層,阻抗模型選用CoatedMicrostrip 2B阻抗計算方法如圖4所示,最后得到表層50歐姆射頻信號的線寬為15.7mil。

圖4 表層50歐姆射頻信號阻抗計算

(4)微帶線阻抗計算參數說明:

1.H1是表層到參考層的介質厚度,不包括參考層的銅厚;

2.C1,C2,C3是綠油的厚度,一般綠油厚度在0.5mil~1mil左右,所以保持默認就好,其厚度對阻抗的影響不是很大;

3.T1的厚度一般為表層基銅銅厚加電鍍的厚度,1.8mil為0.5OZ(基銅厚度)+Plating的結果;

4.一般W1是板上走線的寬度,由于加工 后的線為梯形,所以W2

2.帶狀線阻抗計算

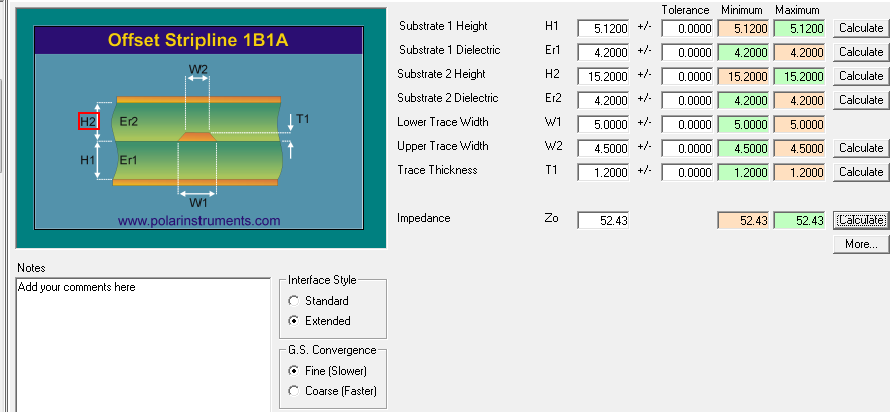

(1)帶狀線(Art03和Art06層)內層單端阻抗選用Offeset Stripline 1B1A模型,50歐姆阻抗計算方法如圖5所示,計算出來的內層50歐姆單端線寬為5mil。

圖5 內層50歐姆單端阻抗計算

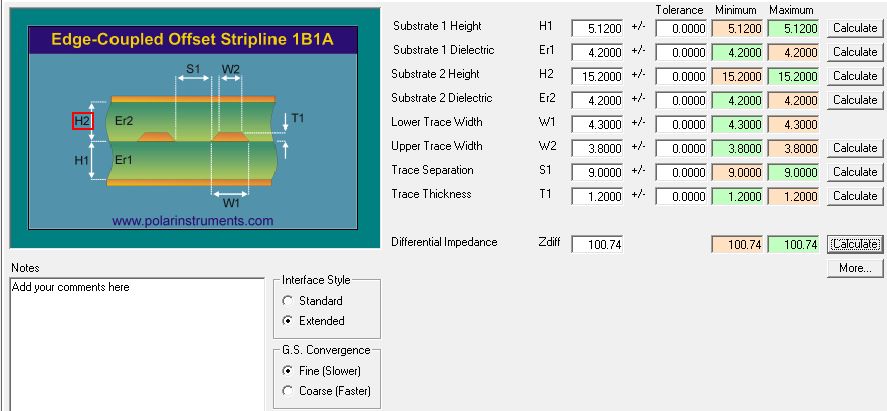

(2)帶狀線(Art03和Art06層)內層差分阻抗選用Edge-Coupled Offeset Stripline模型 1B1A,100差分歐姆阻抗計算方法如圖6所示,計算出來的內層100歐姆差分線寬線距為4.3/9mil。

圖6 內層100歐姆差分阻抗計算

(3)帶狀線阻抗計算參數說明:

1.H1是導線到參考層之間core的厚度,H2是導線到參考層之間pp厚度(考慮pp流膠情況);如圖7-14和7-15阻抗計算圖所示,以ART03為例,H1就是GND02到ART03之間的介質厚度為5.12mil,而H2則是GND04到ART03之間的介質厚度再加上銅厚,所以H2的值應該為14mil+1.2mil=15.2mil;

2.Er1和Er2之間的介質不同時,可以填各自對應的介電常數;

3.T1的厚度一般為內層銅厚;當為HDI板時,需要注意內層是否有電鍍,有電鍍的話需要將電鍍的厚度加上去。

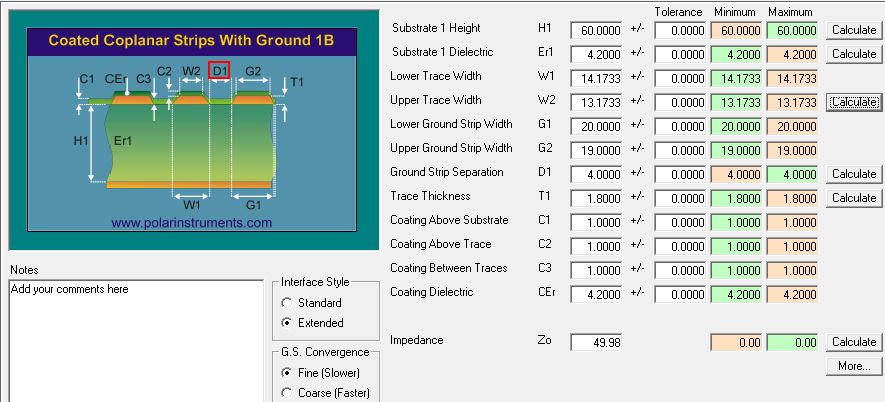

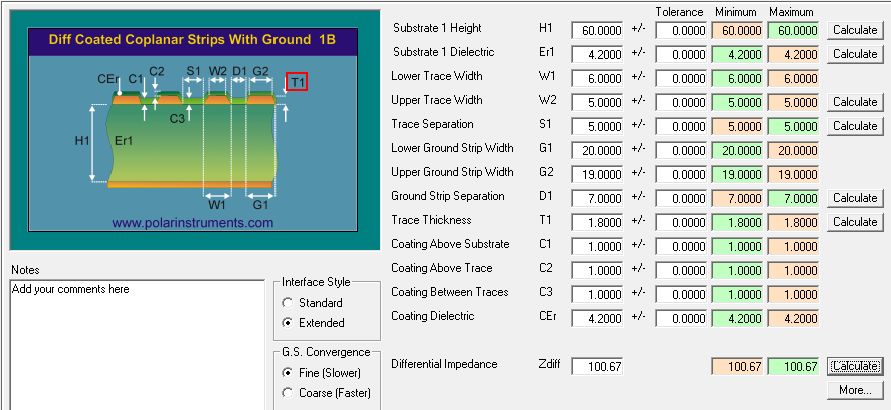

3. 共面波導阻抗計算

上述是常見的阻抗計算,然而有部分PCB板厚較厚,層數較少,利用上述方法沒有辦法計算出阻抗線的具體參數,這個時候就要考慮共面波導模型,這種模型是信號線參考其旁邊的地線做阻抗,一般在雙面板的場合用的比較多。

(1)單端50歐姆,選用Coated Coplanar Strips With Ground 1B模型,其阻抗計算方法如圖7所示,計算結構為阻抗線寬14mil,阻抗線到地線的距離4mil,地線的寬度為20mil。

圖7 50歐姆共面波導阻抗模型計算

(2)差分100歐姆,選用 Diff Coated Coplanar Strips With Ground 1B,其阻抗計算方法如圖8所示,計算結果為100歐姆差分線寬線距為6/5mil,差分線到地線的距離為7mil,地線線寬為20mil。

圖8 100歐姆差分共面波導阻抗模型計算

(3)共面波導阻抗計算參數說明:

1.H1是阻抗線到最近參考層的介質厚度;

2.G1和G2是伴隨地的寬度,一般是越大越好;

3.D1是到伴隨地之間的間距。

4. 阻抗計算的幾個注意事項

(1)線寬寧愿寬,不要細。

因為我們知道制程里存在細的極限,寬是沒有極限的。如果到時候板廠為了調阻抗把線寬調細而碰到細的極限時那就麻煩了,要么增加成本,要么范松阻抗管控,要么修改設計...所以在計算時相對寬就意味著目標阻抗稍微偏低,比如50歐姆,我們算到49歐姆就可以了,盡量不要算到51歐姆。

(2)整體呈現一個趨勢。

我們的設計中可能有多個阻抗管控目標,那么就整體偏大或偏小,不要100歐姆的偏大,90歐姆的偏小

(3)考慮殘銅率和流膠量。

當半固化片一邊或兩片是蝕刻線路時,壓合過程中膠會去填補蝕刻的空隙處,這樣兩層間的膠厚度會減小,殘銅率越小,填的越多,剩下的越少。所以如果你需要的兩層間半固化片厚度是5mil,要根據殘銅率選擇稍厚的半固化片

(4)指定玻璃布型號和含膠量。

看過板材datasheet都知道不同的玻璃布,不同的含膠量的半固化片或者芯板的節點系數是不同的,即使是差不多高度的也可能是3.5和4的差別,這個差別可以引起單線阻抗3歐姆左右的變化。另外玻纖效應和玻璃布開窗大小密切相關,如果你是10Gbps或更高速的設計,而你的疊層又沒有指定材料,板廠用了單張1080的材料,那就可能出現信號完整性問題。

(5)多和板廠溝通

當然殘銅率和流膠量有時候計算會有誤差,新材料的介電系數有時和標稱不一致,有的玻璃布板廠沒有備料等等都會造成設計的疊層實現不了或者交期延后。出現這些情況的時候,最好的辦法就是在設計之初讓板廠按設計師的要求,根據他們的經驗設計個疊層,經過多次的溝通和確認,這樣最多幾個來回就可以得到理想的疊層,方便后續的設計。

-

放大電路

+關注

關注

104文章

1782瀏覽量

106575 -

阻抗匹配

+關注

關注

14文章

348瀏覽量

30760 -

電磁波

+關注

關注

21文章

1444瀏覽量

53754 -

GND

+關注

關注

2文章

529瀏覽量

38663

發布評論請先 登錄

相關推薦

淺析阻抗匹配及其應用

阻抗匹配

阻抗匹配總結

關于高速設計中的阻抗匹配的問題

高速PCB中的阻抗匹配

怎樣理解阻抗匹配_pcb阻抗匹配如何計算

什么是阻抗匹配?為什么要做阻抗匹配?

什么是阻抗匹配?為什么要做阻抗匹配?

評論