Chip First工藝

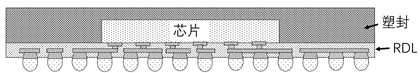

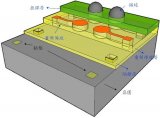

自從Fan-Out封裝問世以來,經過多年的技術發展,扇出式封裝已經形成了多種封裝流程、封裝結構以適應不同產品需要,根據工藝流程,可以分為先貼芯片后加工RDL的Chip First工藝和先制作RDL后貼裝芯片的Chip Last工藝兩大類,其中, 結構相對簡單的是采用Chip First工藝的eWLB ,該結構如圖1所示:

圖1 eWLB結構

其工藝流程如下:

1

將切割好的芯片Pad面向下粘貼在帶臨時鍵合膠的載片上;

2

從芯片背面對載片進行灌膠塑封;

3

移除臨時載片形成塑封后的二次晶圓(扇出式晶圓);

4

去除Pad上的殘留膠并在Pad面形成RDL層;

5

在RDL層上植球并切割成單個成品。

此技術的優勢是 制程相對簡單,成本優勢明顯 。但由于移除載片后,扇出晶圓的翹曲難以控制,對RDL線路的生長技術提出了挑戰,難以制作高密度的RDL,因此該技術主要應用于布線密度較低的中低端的產品。

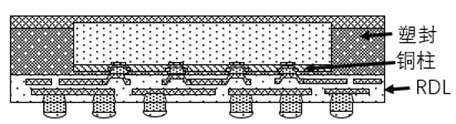

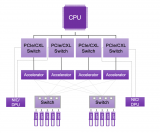

真正讓Chip First扇出式封裝成為行業熱點的原因無疑是因為臺積電(TSMC)在2016年在I-phone7中使用了InFO^TM^結構,該結構如圖2所示。

圖2 臺積電InFO產品結構

其工藝流程如下:

1

在晶圓Pad上制作一層預制銅柱;

2

將切割好的芯片Pad面向上粘貼在帶臨時鍵合膠的載片上;

3

對載片進行灌膠塑封;

4

對塑封好的扇出晶圓進行研磨,露出預制銅柱的頂部;

5

在預制銅柱的頂部進一步制作RDL及植球移除載片;

6

將完成植球的扇出式晶圓切割成單個成品。

該技術由于布線工藝在載片上完成,沒有翹曲等因素的影響,因而能夠實現高密度布線,同時整體封裝厚度也能控制的很低,多應用在高端手機處理器等高價值芯片上。缺點是工藝控制要求高,而且RDL良率直接會影響到芯片成品率,因此最終成品價格較高。

以上方式都是先貼芯片后制作RDL的工藝,所以稱為Chip-First工藝,如果先制作RDL,然后在RDL上貼裝芯片,便稱為Chip-Last工藝。此工藝需要在RDL上倒裝植球后的芯片,通常適用于空間要求略高的FcBGA產品,但由于只在檢驗合格的RDL上貼裝芯片,可避免RDL工程良率給芯片帶來的損失,因此對于價格昂貴的高端芯片而言,有較明顯的價格優勢。

長電科技Chip Last工藝

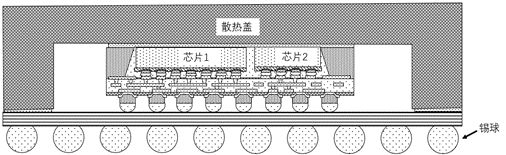

長電科技2021年7月正式推出了一款使用Chip-Last封裝工藝的高密度扇出式封裝 — XDFOI ^TM^ -FcBGA-H,該產品的結構如下:

圖3 JCET XDFOI ^TM^ -FcBGA-H封裝結構

其工藝流程如下:

1

在帶臨時鍵合膠的載片上制作RDL線路層;

2

倒裝焊接上已植球切割好的芯片;

3

芯片底部焊接區域進行底部填充,再對整張貼好芯片的基板進行整體塑封;

4

移除載片并在圓片底部形成Bump;

5

對此整個扇出式原片進行研磨與切割后形成XDFOI^TM^ Fan-Out Unit顆粒;

6

將Fan-Out Unit倒裝封裝在基板上并進行底部填充;

7

貼裝散熱蓋及植球,最終形成XDFOI ^TM^ -FcBGA-H封裝。

此技術的優點在于:避免了RDL良率造成的芯片損失,具有更高的成本競爭力,且直接在載片上布線RDL,簡化了工藝。另外RDL的布線間距也可以達到2um水準,大大提高布線密度,能滿足高性能產品封裝需求。

Fan-Out封裝發展趨勢

隨著Chip-Let技術會越來越得到半導體業界的重視,封裝技術的發展已經成為了半導體行業發展的重要支點,而先進高密度Fan-Out封裝也必然是發展中的熱點。

根據目前的發展趨勢看,Fan-Out封裝主要有以下幾個發展趨勢:

01|高密度布線

根據行業發展預測,下一代Fan-Out技術RDL的布線間距將達到1um以下,這將對RDL布線技術的發展提出進一步挑戰。

02|產品大型化

由于突破了單個硅芯片限制, 多Die合封的封裝單元尺寸很容易突破原有單顆硅芯片常規上限(通常為830mm ^2^ )的限制,各大OSAT的合封單元目標都在1500mm^2^以上,有的面積甚至將達到2500mm ^2^ ,這對封裝工藝以及封裝材料開發提出了巨大的挑戰。

03|封裝結構復雜化

在Chip-Let技術發展路線圖中,芯片互聯種類越來越復雜,不僅有RDL互聯,還有硅基板Interposer互聯,橋接芯片互聯等封裝方式都在快速發展中。封裝模式的多元化對制程能力開發也提出了更高的要求。

臺積電、Intel、Samsung等國際頂尖半導體公司都已成功進軍先進封裝市場。各大先進半導體公司都確立發展高密度扇出式封裝為技術戰略方向。值此變革之時,長電科技緊跟時代潮流,在先進封裝上積極投入,率先在國內開發出了自己的先進高密度Fan-Out封裝。長電科技不但要在國內企業中保持技術領先優勢,還要進一步開拓進取,繼續在先進封裝上加大研發力度,力爭在后摩爾時代的半導體技術開發的國際競爭中占得先機。

-

芯片

+關注

關注

454文章

50460瀏覽量

421979 -

封裝

+關注

關注

126文章

7794瀏覽量

142741 -

Chip

+關注

關注

1文章

59瀏覽量

26401

發布評論請先 登錄

相關推薦

推動AI高性能計算的先進封裝解決方案

先進高性能計算芯片中的扇出式封裝

先進高性能計算芯片中的扇出式封裝

評論