微系統技術是突破摩爾定律極限的重要解決途徑之一,受到廣泛關注。微系統的實現途徑有SoC、SiP和SoP三個層級,其中SiP和SoP以其靈活性和成本優勢成為近期最具應用前景的微系統集成技術。綜述了SiP和SoP的技術內涵、集成形態以及關鍵技術,為微系統集成實現提供參考。

關鍵詞:微系統;系統級封裝(SiP);基于封裝的系統(SoP)

0 引言

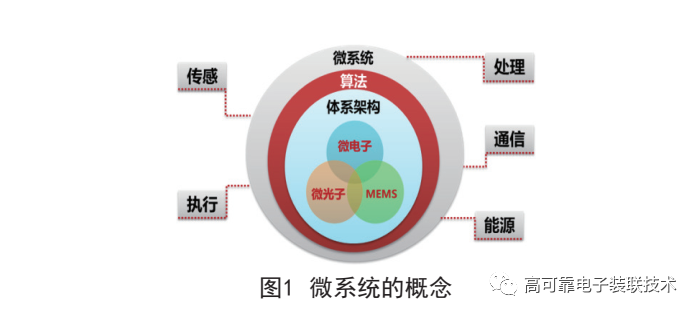

微系統是融合體系架構、算法、微電子、微光子、微機電系統(Micro Electro Mechanical Systems,MEMS)五大要素,采用新的設計思想、設計方法、制造方法,將傳感、處理、執行、通信、能源等五大功能集成在一起,具有多種功能的微裝置[1]。其中,體系架構是構建微系統的骨架,功能算法是微系統的靈魂,微電子、光電子、MEMS等是微系統的基本元素,學科交叉融合是微系統創新的源泉(如圖1所示)。

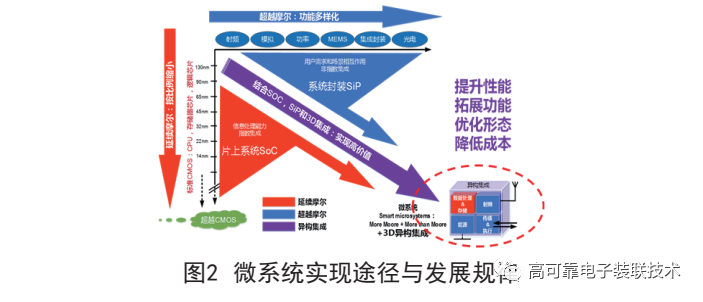

近年來,微電子技術的發展已經從單一的摩爾定律向超越摩爾定律發展,即在尺度縮小的基礎上更加突出功能的融合。微系統的發展與微電子和集成技術的發展息息相關,微電子沿著摩爾定律繼續發展,它追求的是更小的納米尺度工藝,以此推動集成電路向更高的集成度方向發展。

集成技術沿著超越摩爾定律的方向發展,它面向應用,通過射頻、模擬、光電等多種功能的融合集成提升集成密度[2]。微系統集成則是綜合了延續摩爾和超越摩爾兩條路徑的最新成果,通過三維異質異構集成實現更高的價值(如圖2所示)。系統的多功能融合和多專業多學科高度交叉給集成制造能力和工藝技術帶來了前所未有的機遇與挑戰。

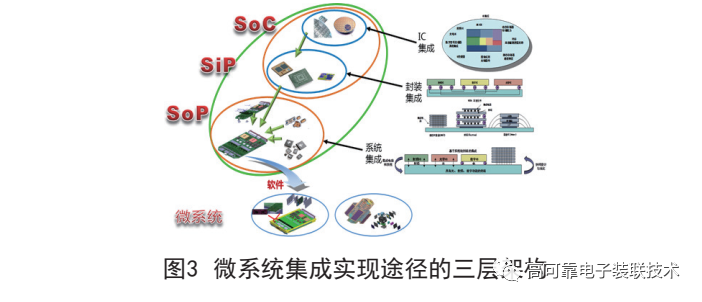

微系統有三種典型的實現路徑,分別是SoC(Systemon Chip,片上系統)、SiP(System inPackage,系統級封裝)和SoP(System on Package,基于封裝的系統),其中SoC是芯片級的集成,SiP是封裝級的集成,而SoP是系統級的集成。多功能芯片是SoC,基于封裝基板和多功能芯片的高密度集成構成SiP,若干個具有特定功能的SiP及其他輔助元器件與系統母板集成構成SoP,而SoP再與系統軟件結合最終構成了面向用戶的微系統產品。系統軟件與功能算法是微系統的“靈魂”,而SoC、SiP和SoP構成了微系統的“肉身”,成為微系統的物理實現途徑(如圖3所示)。

在三層架構的微系統集成實現途徑中,SoC期望在單芯片上通過異構甚至異質的方式集成多個系統功能,是微系統的終極目標,但其受限于材料和工藝兼容性等問題,技術難度大,研發周期長,成本高昂,還無法實現大規模的集成。

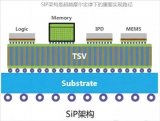

因此,目前更多是以多功能芯片的形態存在,必須與其他技術手段相結合才能實際應用于電子裝備和系統。SiP是將多種異構芯片、無源元件等采用二維或三維形式集成在一個封裝體內。其具有更高的靈活性,更高的綜合集成密度,更高的效費比,是目前微系統集成的熱門研究領域。

然而,SiP由于其本身集成規模的限制,以及部分功能集成手段的制約,仍很難綜合解決散熱、電源、外部互連和平臺集成等系統必備需求,也仍無法構成獨立的系統。SoP則是面向系統應用,基于系統主板,將SiP、元器件和連接器、散熱結構等部件集成到一個具備系統功能的廣義封裝內。SoP可以加載系統軟件,可以具有完整的系統功能,是功能集成微系統最合理、最直觀的集成形勢,也是整機和系統的核心集成能力[3]。

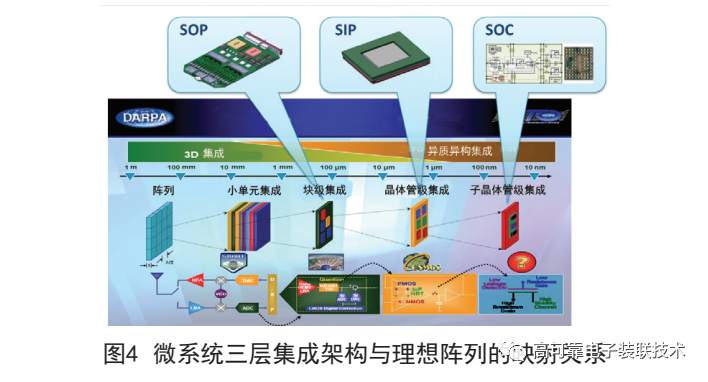

如圖4所示,在DARPA提出的理想陣列中,也可以見到從SoC到SiP,再到SoP最終到系統的實現過程,其中需要從納米到微米,再到毫米的跨越多個尺度的集成制造手段。

本文將重點分析SiP和SoP的內涵形態與關鍵技術。由于SoC的集成關鍵技術主要集中在微電子芯片工藝,在本文中不做重點論述。

1 SiP的內涵形態與關鍵技術

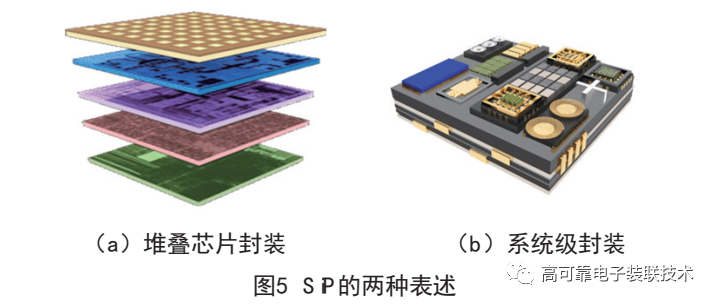

如圖5所示,SiP在集成封裝行業中有兩種不同的表述,分別是堆疊芯片封裝(Stacked ICs andPackage)和系統級封裝(System in Package)。其中,后者的使用較為廣泛。然而,這兩種表述具有很強的互補性,其關鍵技術共同構成了SiP的豐富內涵。堆疊芯片封裝的關注焦點在芯片和芯片的堆疊形態,可以理解為芯片級/晶圓級的集成封裝。系統級封裝則更多的關注功能的融合,主要依托于多功能的封裝基板,可以理解為基板級的集成封裝。

1.1 堆疊芯片封裝

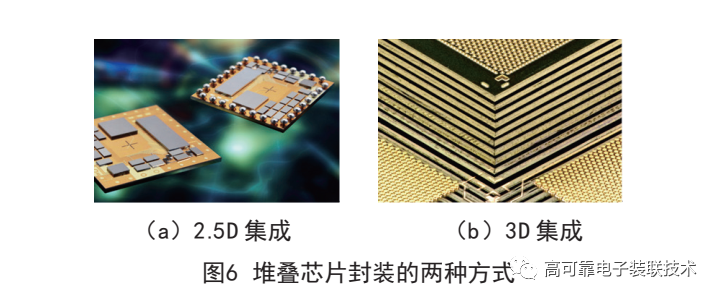

堆疊芯片封裝的集成形態是在硅、玻璃或其他材料的圓片或晶圓上通過微米級的工藝手段集成各類裸芯片與無源元件。該集成方式具有微米級的線寬和精度,具有高精度、高密度集成特點,是半導體工藝向上拓展后在異構集成中的應用。然而,與SoC類似,堆疊芯片封裝的集成規模、功能復雜度相對較低,結構強度較低,環境適應性較弱,當前較難直接在系統中集成應用,通常需要進行二次封裝。如圖6所示,堆疊芯片封裝的集成形態既包括以轉接板為過渡的2.5D集成,也包括芯片/晶圓直接堆疊的3D集成[4]。

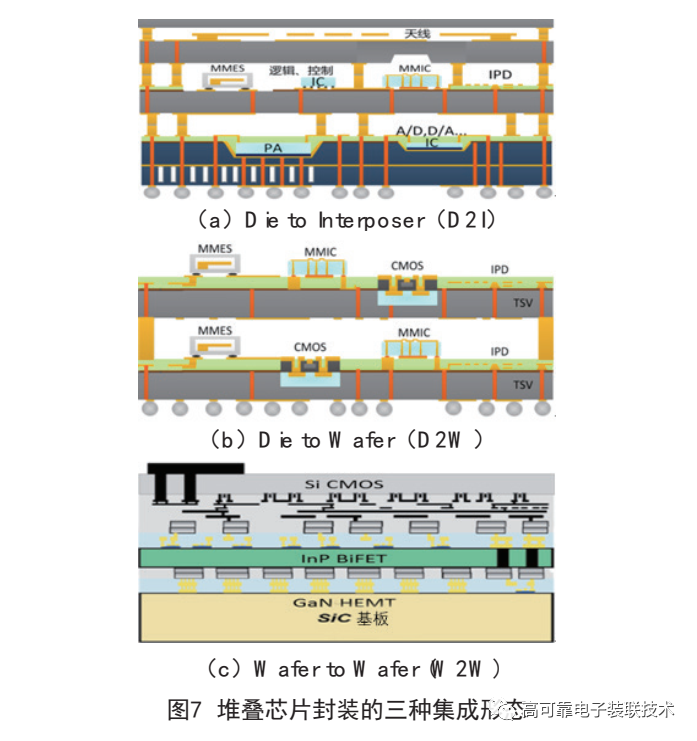

如圖7所示,在2.5D和3D集成的基礎上,堆疊芯片封裝有三種典型的集成形態:

1)D2I(Die toInterposer):制作帶TSV(ThroughSi Vias,硅通孔)互連通孔、IPD(集成無源元件)和微通道散熱的硅基無源轉接板,表面集成有源器件后三維堆疊。

2)D2W(Die toWafer):對已有CMOS(ComplementaryMetal-Oxide-SemiconductorTransistor,互補金屬氧化物半導體)晶圓做重布線和TSV互連通孔,表面集成其他非CMOS器件后三維堆疊。

3)W2W(Waferto Wafer):各同類或異類晶圓直接三維堆疊鍵合集成。

其中D2I是典型的2.5D集成形態,D2W進入到3D集成領域,而W2W是典型的3D集成形態。三種集成形態的兼容性、靈活性和技術成熟度可以簡單排序為D2I>D2W>W2W[5-7]。

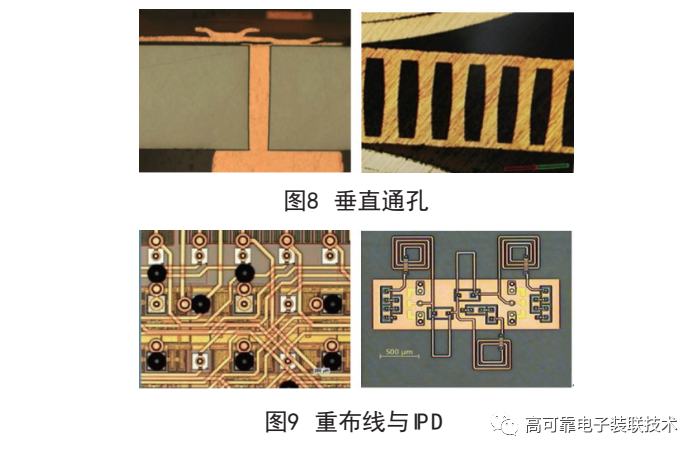

堆疊芯片封裝主要采用晶圓后道工藝,有三項主要關鍵技術:垂直通孔、重布線與IPD集成和互連與鍵合。

如圖8所示,垂直通孔是通過硅、玻璃等轉接板或晶圓內的互連通孔,實現信號的高密度低損耗垂直互連。典型孔徑為550 μm,典型深徑比為5:110:1。

如圖9所示,重布線與IPD集成是通過轉接板/晶圓表面的多層重布線,實現裸芯片與晶圓間,晶圓與晶圓間的接口匹配,同時將占據表面的部分無源元件內埋。典型線寬為2~10 μm。

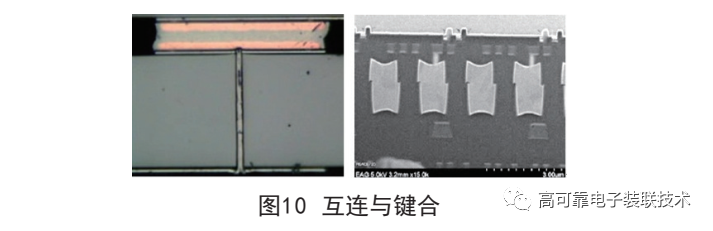

如圖10所示,互連與鍵合是通過同質/異質材料的鍵合集成,實現裸芯片與晶圓間,晶圓與晶圓間的機械連接和電氣互連。鍵合方式包括金屬鍵合、高分子鍵合、硅-硅/氧化硅-氧化硅/硅-氧化硅鍵合等[8-10]。

1.2 系統級封裝

系統級封裝的集成形態是以高密度基板為核心,集成組裝射頻、模擬、數字、光電等各類元器件,構建高性能核心功能單元,實現芯片的互連、散熱和環境適應性防護[11]。該集成方式與晶圓級集成相比集成規模更大,功能更復雜,結構強度更能適應各種復雜環境需求(如圖11所示)。相應的,該集成方式的集成密度相對晶圓級集成較低。

系統級封裝主要采用封裝工藝,有三項主要關鍵技術:高密度基板、多功能異構組裝、封裝與防護和封裝多層堆疊(Package on Package,PoP)。

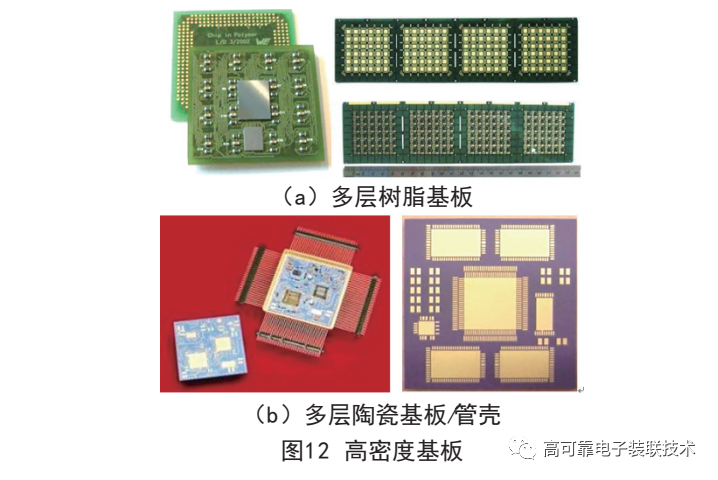

高密度基板是SiP集成的物理載體,其功能包括元器件之間的電氣互連,傳輸射頻、模擬、數字等信號;內埋集成部分無源元件,包括電容、電阻、電感,以及功分器、濾波器等;為元器件提供散熱通道。常用的SiP封裝高密度基板包括多層樹脂基板和多層陶瓷基板/管殼,其選擇的影響因素包括線條寬度、布線層數、后續封裝防護方式等(如圖12所示)。

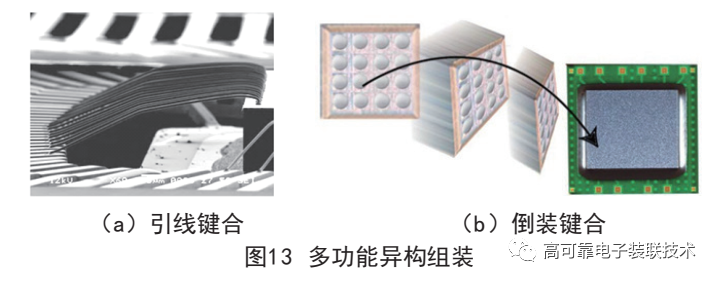

如圖13所示,多功能異構組裝是通過引線、倒裝等主要手段,將數字、模擬、射頻甚至光電器件通過鍵合集成組裝在高密度基板上,實現特定的部件功能。其還包括粘接、貼片、底部填充等集成關鍵技術。

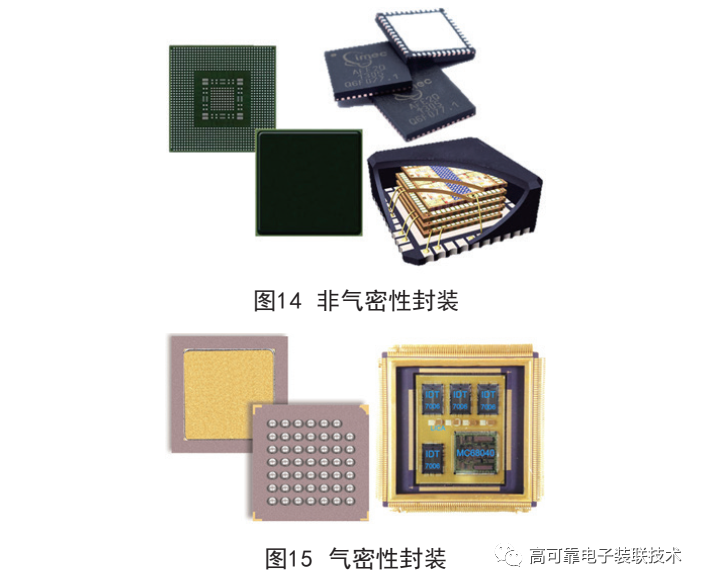

封裝與防護是以一定的手段將較脆弱的芯片保護起來,以滿足特定應用下的環境適應性要求和可靠性要求。根據應用領域的不同和對環境適應性可靠性的要求不同,可以采用非氣密性封裝和氣密性封裝(如圖14和圖15所示)。其中,非氣密性封裝用于對可靠性要求較低的場合,包括塑封、包封、粘接金屬蓋等手段實現保護與電磁屏蔽。氣密性封裝主要用于高可靠場合,包括陶瓷/玻璃封裝、金屬封裝等手段。

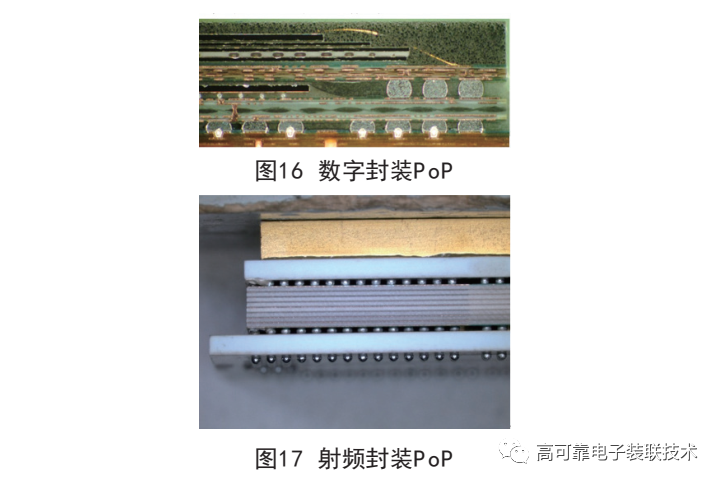

多層堆疊:與芯片和晶圓級的三維堆疊類似,SiP封裝在平面上的集成空間已經不足,可通過三維堆疊集成,在提升集成密度的同時,降低互連長度,提升性能(如圖16和圖17所示)。

2 SoP的內涵形態與關鍵技術

在一個電子系統中,半導體IC芯片通常只占體積的10%,通過SoC和SiP技術可以解決系統體積10%~20%的縮減。其余空間則被大量的分立無源元件、電路板及其線纜連線占據。SoP提供了解決這80%~90%問題的系統集成路徑,通過“超越摩爾定律”的方式,從根本上大幅提升系統集成密度,成數量級降低系統整體的體積質量(如圖18所示)。

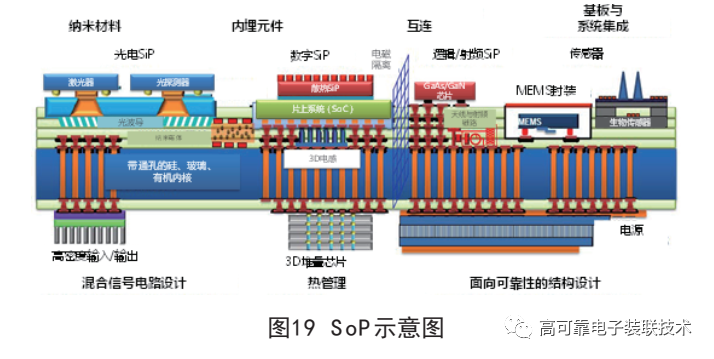

如圖19所示,SoP是基于封裝的系統,是基于系統主板,將SiP、元器件和連接器、散熱結構等部件集成到一個具備系統功能的封裝內。它通過對數字、射頻、光學、微機電系統的協同設計和制造,提供幾乎所有的系統功能,是在SiP以上更高層次的集成,也屬于廣義的封裝集成領域。

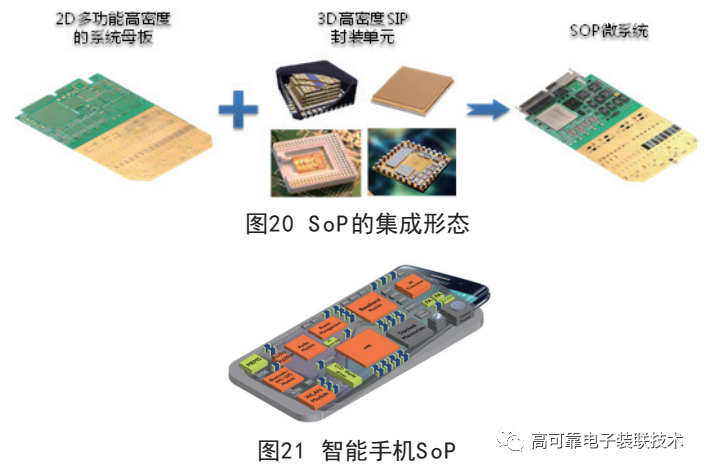

如圖20所示,SoP的基本集成形態是2.5D的板級集成,是在2D的多功能高密度系統母板上集成3D的高密度封裝單元,最終形成一個具有系統功能的板級微系統。在消費電子領域,智能手機的核心功能就是通過SoP的形式集成實現的(如圖21所示)。

SoP集成有四項關鍵技術,分別是系統母板、高密度混合信號多工藝跨尺度異構集成與互連、集成可靠性與多層級熱管理。

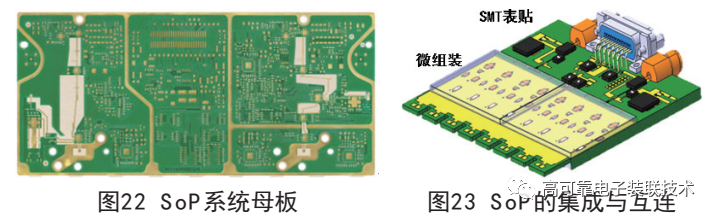

如圖22所示,系統母板是整個SoP微系統提升集成密度的基礎和核心。在系統母板內部嵌入射頻、數字、光等所需的高質量信號傳輸,以替代大量線纜,大幅縮小體積重量;嵌入阻容、功分、濾波等無源元件,以替代大量分立無源元件,大幅節省平面面積,用于有源芯片的集成;嵌入散熱結構,以替代部分分立散熱結構,降低體積質量。

如圖23所示,SoP微系統具有基本完整的系統功能,需將各類異構SiP封裝或元器件在SoP主板上組裝集成并實現高質量信號互連。集成互連的信號包括數字、模擬、射頻、光等復雜信號;集成工藝包括正裝集成、引線鍵合、倒裝集成、SMT和光電集成等;集成尺度從10 μm到mm跨過至少兩個量級。因此,高密度混合信號多工藝、跨尺度異構集成與互連工藝兼容性是核心問題。

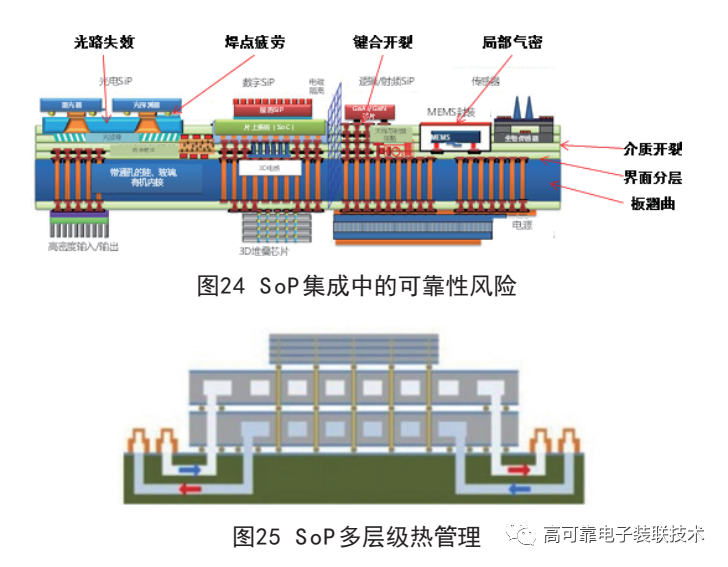

如圖24所示,SoP主板與SiP封裝相比尺寸大、密度高、材料體系多樣、集成要素種類數量多、工藝過程復雜,系統可靠性保障難度明顯增加,需要更加詳細精確的可靠性設計與驗證。

SoP系統集成密度大幅提升,帶來熱耗的大幅增加,系統散熱壓力劇增,需建立芯片到SiP封裝到SoP微系統的全套多層級熱管理體系(如圖25所示)。傳統主要通過熱傳導的散熱方式將可能不再適用,需要引入微流道、微熱管、微噴流、相變散熱等新型散熱手段。

3 結論

微系統技術是突破摩爾定律極限的重要解決途徑之一,當前已進入“百花齊放、百家爭鳴”的高速發展階段。微系統的集成實現途徑有SoC、SiP、SoP三個層級,其中SiP和SoP以其靈活性和成本優勢成為近期最具應用前景的微系統集成技術,本文淺析了SiP和SoP的技術內涵、集成形態以及關鍵技術,為微系統集成實現提供參考。

參考文獻

[1] 湯曉英.微系統技術發展和應用[J].現代雷達,2016,38(12):45-50.

[2] RADOJCICR. More-than-Moore 2.5D and 3D SiP integration[M].Berlin, GER: SpringerPublishing Company, 2017.

[3] TUMMALA RR, SWAMINATHAN M. Introduction to system-on package (SOP): Miniaturization ofthe entire system[M]. NYC, USA:Mc Graw-Hill Companies, Inc. 2008.

-

SiP

+關注

關注

5文章

498瀏覽量

105257 -

SOP

+關注

關注

0文章

92瀏覽量

27493 -

微系統

+關注

關注

1文章

31瀏覽量

10168

發布評論請先 登錄

相關推薦

基于RF?SIP 集成架構的射頻系統技術

一文看懂SiP封裝技術

SiP(系統級封裝)技術的應用與發展趨勢

SIP(封裝系統),SIP(封裝系統)是什么意思

基于ARM和FPGA的SiP通用微處理系統封裝設計

SIP系統封裝技術淺析

三點說明SIP與SOP的區別

什么是SIP與SOP?

什么是SiP技術 淺析SiP技術發展

微系統與SiP、SoP集成技術

微系統與SiP、SoP集成技術

評論