?

1 SiP項目成功的三要素

做SiP項目的人,都希望項目能夠一次成功,取得同行和領導的認可,從而爭取更多的項目和經費支持。那怎么才能使項目一次成功呢?這就需要我們把握好SiP項目成功的三要素,那就是: 裸芯片、設計仿真、生產制造 。

1.1 裸芯片

裸芯片(die,bare die,bare chip),通常是指半導體元器件制造完成,封裝之前的產品形式。裸芯片通常是以晶圓形式(wafer form)或單顆芯片(die form)的形式存在,封裝后成為半導體元件、集成電路、或更復雜電路例如系統級封裝SiP的組成部分。

在國內,由于國外芯片禁運等原因,很多國外芯片難以購買,對于裸芯片更是如此。經常一款SiP項目中需要的部分裸芯片無法購買到,這時該項目就難以繼續。根據以往的經驗,通常的解決方法有以下四種:

- 采用***代替,目前***也是遍地開花,通常國際上比較著名的芯片廠商的產品在國內都可以找到對應的替代品,雖然在性能和容量等方面還無法達到國際同類產品的水準,但很大程度上已經能滿足SiP項目的需要了。

- 采用同類芯片代替,例如AD,DA、運放類裸芯片,很多功能相近,可以通用,滿足設計指標的前提下,可以用可購買到的同類芯片替代。

- 更改設計方案,對設計方案進行合理的裁剪,例如一個完整的計算機系統并不一定要完全在一個SiP中實現,可以分成例如系統主控SiP,數據處理SiP,接口管理SiP等,這樣就比較容易首先實現某一部分功能的SiP了。

- 實在找不到裸芯片但還必須在項目中用的芯片,可以采用小封裝例如CSP,QFN等代替,這個需要提前和生產廠家溝通工藝兼容性問題。

以上四種方法在實際項目中都有應用,也取得了良好的效果,用戶最終都做出了滿意的SiP產品,實現了應有的功能。

1.2 設計仿真

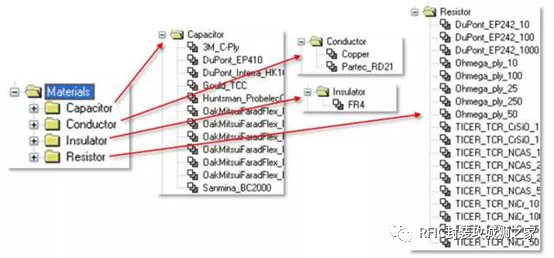

目前,SiP設計軟件有兩個廠家提供,Mentor和Cadence,SiP仿真軟件則有Mentor、AnSys、Cadence、ADS等多家。每家軟件都有各自的特點和優勢,這里我們不準備詳述各個軟件的功能比較,后面的的文章,我會專門對各家軟件進行描述并對其功能進行比較。

- 針對 設計軟件 ,主要需要考慮其功能時是否對鍵合線(Wire Bonding)、芯片堆疊(Die Stacks)、腔體(Cavity)、倒裝焊(Flip Chip)及重分布層(RDL)、埋入式無源元件(Embedded Passive)、參數化射頻電路(RF)、多版圖項目管理、多人實時協同設計、3D實時DRC等最新的SiP技術能有較好的支持。

- 針對 仿真軟件 ,主要需要考慮能否方便地將設計數據導入,并能夠正確識別各設計元素;是否具備SI、PI、EMI、熱、電磁場等仿真功能,仿真精度、仿真速度能否滿足項目要求等。

另外,除了軟件本身的功能外,還需要重點了解各個廠家對技術支持的重視程度和技術支持人員的經驗水平等因素,因為很多用戶初次接觸SiP項目,軟件廠家技術人員的經驗水平對項目成功起到重要甚至決定性的作用。

1.3 生產制造

一款SiP設計完成后,必須選擇合理并且靠譜的生產廠家,才能夠保證項目的最終成功。

一般情況下,塑料封裝、陶瓷封裝、金屬封裝的生產工藝完全不同,其設計規則定義也會差別很大,所以要根據項目情況提前考慮選擇不同類型的生產廠家。

在項目設計的過程中就需要提前和相關廠家取得聯系,獲取廠家的工藝能力和生產制造要求,并以此為依據定義設計規則,這樣設計出的產品才能滿足生產制造的要求,即所謂的可制造性設計DFM(design for manufacture)。

廠家往往為了爭取更多項目,常常也會將其極限的生產能力報給用戶,這時候我們就需要合理的考核其常規生產能力和極限生產能力,盡量在其常規生產能力范圍內進行設計,這樣就避免了成品率過低或者價格過高的問題。

另外,還需要了解廠家是否完全具備【基板+封裝+測試】的能力,還是只具備其中某一種能力,其它需要通過外協來完成,此時需要和廠家協商好如何保證產品質量和進度,避免由于生產環節周期過長而造成的項目延誤。

2 如何選擇SiP產品工藝和材料

對于一個新的SiP產品或者項目,設計師首先需要了解的就是采用什么樣的工藝和材料來實現SiP產品,不同的選擇會帶來哪些不同,成本、周期有多大的區別?

SiP系統級封裝產品按工藝或材料通常主要分為:塑料封裝SiP、陶瓷封裝SiP和金屬封裝SiP三種類型,參看圖1。

圖1 三種不同工藝材料的SiP封裝類型

每種類型的 SiP產品都有其特點和優勢,需要設計師根據項目的用途、項目周期、項目經費情況進行合理選擇。

2.1 塑料封裝SiP

塑料封裝SiP通常稱為塑封SiP,主要應用于商業級產品,具有低成本優勢,但在芯片散熱、穩定性、氣密性方面相對較差。其特點主要總結如下:

- 密封性稍差,無法阻擋濕氣和腐蝕性氣體對芯片的腐蝕;

- 不容易拆解,模封灌膠后,幾乎無法打開,否則損壞芯片;

- 散熱性能較差,因為有機基板和模封膠的傳熱系數低;

- 工作溫度范圍小,一般溫度范圍為0℃~+70℃,工業級的是-40℃~+85℃;

- 生產周期短,一般生產周期2~3個月;

- 價格便宜,成本低廉,一次打樣需要人民幣10萬元左右;

- 適合大批生產,在商業領域得到廣泛的應用。

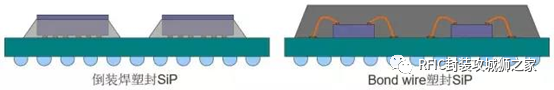

塑料封裝SiP一般采用有機基板對芯片進行互聯和承載,然后通過模封灌膠的方式對芯片進行加固和密封,其結構如圖2所示。

圖2 塑封SiP的結構

2.2 陶瓷封裝SiP

陶瓷封裝SiP多用于工業級產品、軍品以及航空航天、軍工等領域,其散熱優良,氣密性好、可靠性高。同時,陶瓷具有可拆解的優勢,便于故障查找和問題“歸零”。其特點主要總結如下:

- 密封性好,可以做到氣密性,阻擋濕氣和腐蝕性氣體;

- 散熱性能好,陶瓷基板外殼的熱傳導系數比較大,利于芯片散熱;

- 對極限溫度的抵抗性好,陶瓷封裝工作溫度可達到軍品要求-55℃~+150℃;

- 容易拆解,便于問題分析,陶瓷封裝體內部芯片都處于真空裸露狀態;

- 體積小,適合大規模復雜芯片,主要相對與金屬封裝而言;

- 生產周期長,一般生產周期6~8個月;

- 價格高,一次打樣需要人民幣40~100萬元左右;

- 適合軍品和航空航天應用,目前在全球軍工和航空航天領域應用普遍。

陶瓷封裝SiP一般采用HTCC陶瓷基板對芯片進行互聯和承載,其外殼和基板通常為一體,結構多采用腔體結構,用可伐合金焊接密封,其結構如圖3所示。

圖3 陶瓷封裝SiP的結構

2.3 金屬封裝SiP

金屬封裝SiP和陶瓷封裝SiP類似,多用于工業級產品、軍品以及航空航天、軍工等領域,其氣密性好、可靠性高,散熱優良。金屬封裝也可拆解,便于故障查找和問題“歸零”。其特點主要總結如下:

- 金屬封裝密封性好,可以做到氣密性,阻擋濕氣和腐蝕性氣體;

- 散熱性能好,對極限溫度的抵抗性好;

- 容易拆解,開蓋后即可直接看到內部裸芯片;

- 體積較大,扇出引腳較少,不太適合復雜芯片;

- 通常用在MCM領域,射頻微波,模擬SiP領域應用較多;

- 生產周期較長,一般生產周期4~6個月;

- 價格較高,一次打樣需要人民幣30~80萬元左右;

- 適合軍品和航空航天應用。

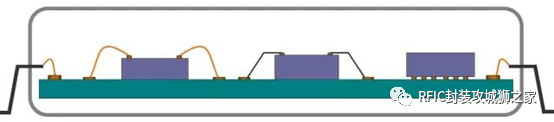

金屬封裝SiP一般采用LTCC、厚膜或者薄膜陶瓷基板對芯片進行互聯和承載,其基板和外殼獨立進行設計和加工,基板采用粘結法固定到金屬外殼上,電氣上采用Bond Wire和外部引腳連接,其結構如圖4所示。

圖4 金屬封裝SiP的結構

看了上面的描述,設計者結合項目的實際情況,就能確定選擇什么樣的工藝和材料來完成自己的SiP項目和產品了。

3 SiP基板選擇——有機基板

SiP基板系列文章

在SiP系統級封裝中,基板作為整個封裝的載體,起著支撐和電氣互聯的作用,目前,常用的基板包括有機基板、陶瓷基板、硅基板等等,我們將逐一介紹,這篇文章,我們主要來討論有機基板。

1

3.1 有機基板的材料

有機基板一般是由有機樹脂和玻璃纖維布為主要材料制作而成,導體通常為銅箔。有機樹脂通常包括:環氧樹脂(FR4),BT樹脂(雙馬來酰亞胺三嗪樹脂),PPE樹脂(聚苯醚樹脂),PI樹脂(聚酰亞胺樹脂)等。

有機基板常用的銅箔厚度為17μm(半盎司),35μm(一盎司),70μm(兩盎司)等多種。柔性有機基板銅箔厚度比較薄,5μm、9μm、12μm等規格的銅箔在柔性板上應用較多。銅箔厚度和載流量成正比關系,如果需要通過比較大的電流,則需要選擇較厚的銅箔和較寬的布線。

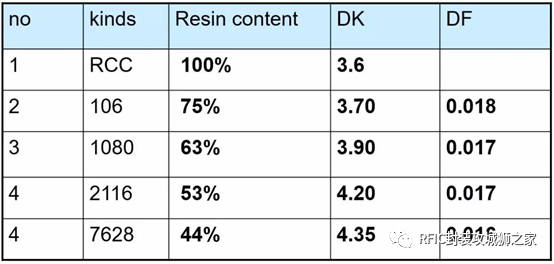

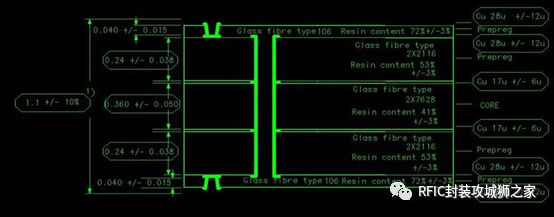

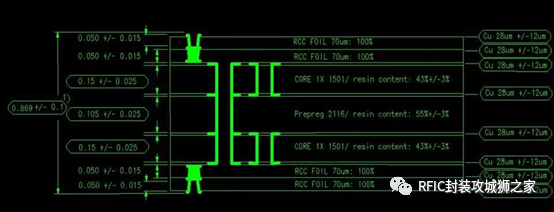

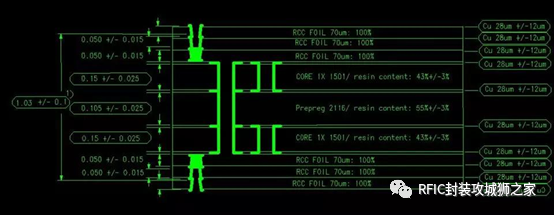

以FR4為例,介質材料根據樹脂和玻璃纖維含量的不同,可分為106,1080、2116、7628等多種型號。一般型號數值越大,樹脂含量越少,玻璃纖維含量增大,硬度增加,介電常數也越高。例如,106樹脂含量75%,1080樹脂含量63%,2116樹脂含量53%,7628樹脂含量44%。另外,還有一種RCC(Resin Coated Copper),樹脂含量100%。樹脂含量越多,材質越軟,激光打孔效率高。

下圖為不同型號的介質材料的樹脂含量、介電常數DK及損耗因子DF

通常為了兼顧各方面的性能,SiP基板會采用多種型號的基材,一般表層用樹脂含量較高的,例如RCC,106,1080,而內層則采用硬度較大的例如2116,7628,用于增強支撐強度,詳見下面基板層疊結構實例圖示。

2

3.2 有機基板的特點

-

有機基板有其自身的特點和優點,和陶瓷基板相比,有機基板不需要燒結,加工難度較底,并且可制作大型基板,同時具有成本優勢,另外有機基板介電常數低,有利于高速信號的傳輸。

當然,有機基板也有自身的劣勢,例如傳熱性能較差,傳熱系數通常只有0.2-1W/(m·K)之間,而氧化鋁陶瓷材料可以達到18W/(m·K)左右,氮化鋁更是可達到200W/(m·K)左右。

-

CTE(Coefficient of Thermal Expansion)是指熱膨脹系數α ,理想的封裝基材:α < 8×10-6/oC,或者為8ppm/oC,(ppm-parts per million,百萬分之一)。

-

半導體芯片的主要成分是硅,而硅的膨脹系數只有2.5ppm/oC,如果半導體芯片與基板的熱膨脹系數相差過大,在溫度變化時,它們之間產生較大的應力。因此,為了保證SiP或者封裝基板微細電路的精度,適宜用低熱膨脹系數的基板材料。

-

Tg玻化溫度,是板材在高溫受熱下的玻璃化溫度,一般Tg的板材為140度以上,高Tg一般大于170度,中等Tg約大于150度。Tg值越高,板材的耐溫度性能越好 ,印制板的耐熱性、耐潮濕性、耐化學性、耐穩定性等特征都會提高和改善。尤其在無鉛制程中,高Tg應用比較多。目前,高耐熱性基板的Tg通常可以達到200度以上。

3

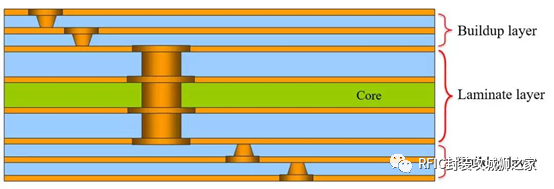

3.3 有機基板層疊結構

SiP或封裝基板通常采用盲埋孔結構,這里我們用m+N+m代表,其中m代表Buildup層,采用積層法工藝進行制作,通常采用激光鉆孔,每次只鉆一層,層層往上累積成多層,因而被稱為積層法,積層法英文為:Buildup。

N代表Laminate層,采用層壓法工藝進行制作,通常采用機械鉆孔,先將多層疊加在一起壓合,然后統一鉆孔,層壓法英文為:Laminate。

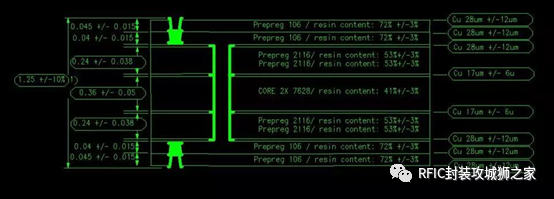

- 下圖為2+4+2的8層基板側面示意圖:

Buildup層的盲埋孔是可以疊加的,但一般不能與Laminate層的通孔疊加,這主要是由于生產工藝的限制。這個兩類孔疊加容易出現斷路。

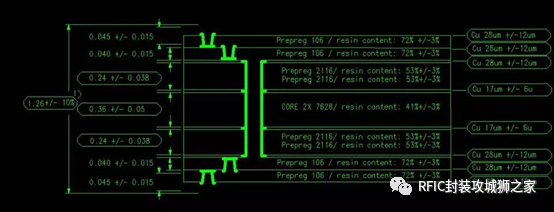

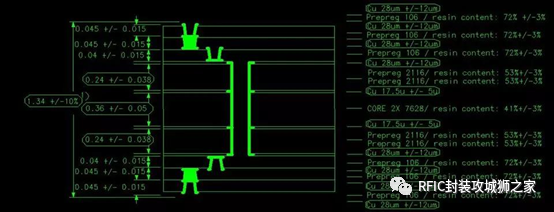

下面幾張圖是有機基板層疊結構的實例(可放大查看每層所用的材料型號和銅箔的厚度)。

- 下圖為6層基板,其層疊結構為1+4+1

- 下圖為8層基板,其層疊結構為2+4+2

- 下圖為8層基板,其層疊結構為1+1+4+1+1

- 下圖為10層基板,其層疊結構為2+1+4+1+2

- 下圖為8層基板,其層疊結構為2+4+2,機械孔又包含更復雜的多次打孔工藝

- 下圖為10層基板,其層疊結構為3+4+3,機械孔層又包含更復雜的多次打孔工藝

3.4 有機基板的選用

有機基板主要應用于塑封器件,由于其具有成本上的優勢,目前是應用最為廣泛的SiP封裝基板。

SiP或者封裝設計者在選用有機基板時,要綜合考慮成本和可靠性進行選擇,主要考慮其熱膨脹系數,玻化溫度,吸濕性能等。從而選擇FR4(環氧樹脂),BT樹脂(雙馬來酰亞胺三嗪樹脂),PPE樹脂(聚苯醚樹脂)PI樹脂(聚酰亞胺樹脂 polyimide)等基板。

同時,需要設置合理的銅箔厚度和層疊結構,選用不同型號的基材,控制好介電常數DK和損耗因子DF,從而使SiP或封裝的性能在成本優化的前提下達到最優。

4 陶封SiP為何多采用腔體結構

SiP系統級封裝產品按工藝或材料通常分為:塑料封裝SiP、陶瓷封裝SiP和金屬封裝SiP幾種類型和各自的特點。

其中陶瓷封裝SiP也簡稱為陶封SiP,美國航空航天局NASA,歐洲太空局ESA采用的SiP基本上均為陶瓷封裝SiP。目前,國內領先的航空航天和軍工領域的研究所都開始研究和應用SiP技術,他們也不約而同地選擇陶瓷封裝作為首選的SiP產品封裝。

陶封SiP密封性好,散熱性能好,對極限溫度的抵抗性好,容易拆解,便于問題分析,相對于金屬封裝體積小,適合大規模復雜芯片。有了這些優點,陶封SiP確實最適合在極限苛刻環境中應用的航空航天等軍工領域。

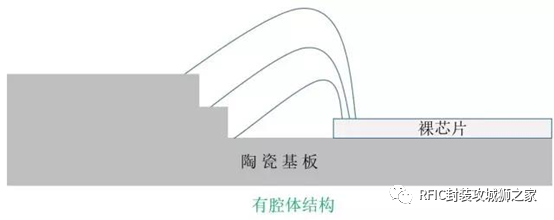

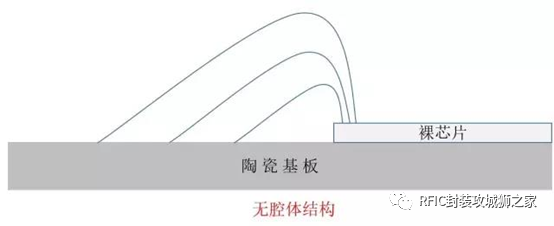

在陶封SiP設計中,有一個最明顯的特征就是:陶封SiP中基本都采用了腔體結構。

4.1 什么是腔體?

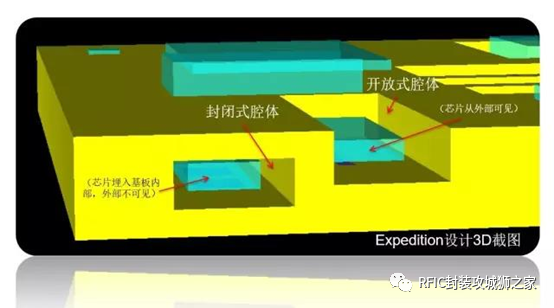

在《SiP系統級封裝設計與仿真》一書中,我這樣寫道:“腔體Cavity是在基板上開的一個孔槽,通常不會穿越所有的板層(在特殊情況下的通腔稱之為Contour)。腔體可以是開放式的,也可以是密閉在內層空間的腔體,腔體可以是單級腔體也可以是多級腔體,所謂多級腔體就是在一個腔體的內部再挖腔體,逐級縮小,如同城市中的下沉廣場一樣。”

下圖是城市中常見的下沉廣場,底部區域供人們活動,臺階可以當看臺或者坐下休息。

城市中常見的下沉廣場

下圖是陶封SiP中常見的腔體結構,底部區域安裝芯片,多級腔體的臺階上可以放置鍵合指Bond Pad。兩者唯一的區別就是下沉廣場多為圓形,而陶封SiP中的腔體多為方形,當然也不排除有些項目中采用了圓形腔體。

4.2 陶封SiP為何基本都會采用腔體?

搞明白了腔體的定義后,我們再來看看陶封SiP為何基本都會采用腔體?根據親自參與的多個陶封SiP實際項目,我總結了一下,大致有以下三種原因:

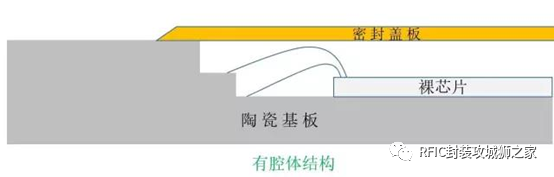

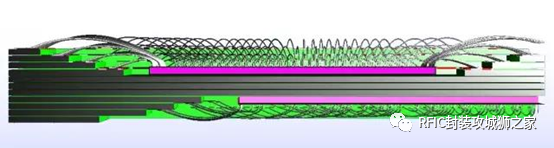

- 腔體結構有利于鍵合線的穩定性

對于復雜的芯片,常常要采用多層鍵合線,鍵合指的排列經常有3-4排,這樣外層鍵合線就會很長,跨度很大,不利于鍵合線的穩定性,而腔體結構則能有效改善這種問題。從下面兩張圖就可以明顯地看出腔體結構大大減小了鍵合線的長度,從而有效地提高了鍵合線的穩定性。

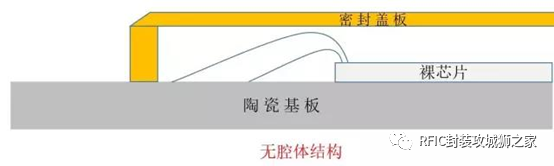

- 腔體結構有利于陶瓷封裝的密封

采用腔體結構的陶瓷基板,芯片和鍵合線均位于腔體內部,只需要用密封蓋板將SiP封裝密封即可。如果無腔體結構,則需要專門焊接金屬框架來抬高蓋板的位置,這樣就多了一道焊接工序,其焊縫的氣密性也需要經過嚴格考核才能達到氣密性要求。

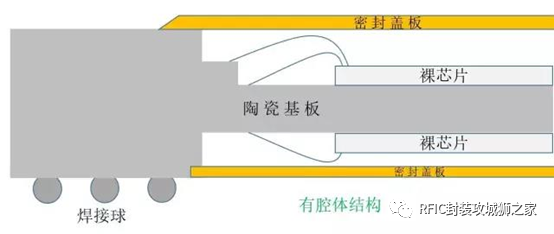

- 腔體結構有利雙面安裝元器件

現在的SiP復雜程度很高,需要安裝的器件很多,在基板單面經常無法安裝上所有器件,需要雙面安裝器件。這時候,腔體結構也就大有用武之地,通過腔體可以將一部分器件安裝在SiP封裝的底面,在封裝底面外側設計并植上焊接球,如下圖所示。

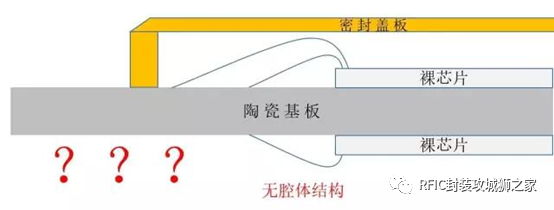

如果沒有腔體結構,就無法在背面安裝器件,如下圖所示:

如果將器件完全安裝在頂面,不可避免要擴大封裝的面積,和SiP小型化的概念是背道而馳的。

最后,我們來看一款實際的陶瓷封裝SiP項目的Expedition設計截圖:此項目為國內第一款采用雙面腔體的陶封SiP項目,完全在一顆SiP中實現了航天計算機的所有功能,并達到軍品級要求。該項目在世界上也處于領先地位,目前已經成功應用到多個航空、航天等重點工程中。

5 如何將元器件埋置在SiP基板內

將元器件埋置在基板內是一個非常有效地縮小SiP面積的方法,同時能有效減少基板表面的焊點,提高其可靠性,那如何將器件埋入到SiP基板內呢?

通俗來說有兩種方法:

- 挖個坑埋進去;

- 壓扁了嵌進去。

第一種方法用專業的術語來講就是:通過腔體技術將分立元器件埋入基板。 第二種方法用專業的術語來講就是:通過特殊材料制作電阻、電容等無源器件并嵌入到板層之間。

5.1 通過腔體的技術將分立元器件埋入基板

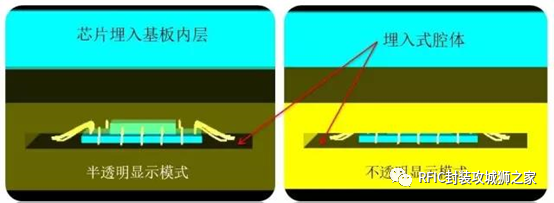

腔體主要是以開放式腔體為主,實際上還有一種腔體稱為埋置腔體,也稱為封閉式腔體,參看下圖,這樣分立器件就可以埋入基板內部了。

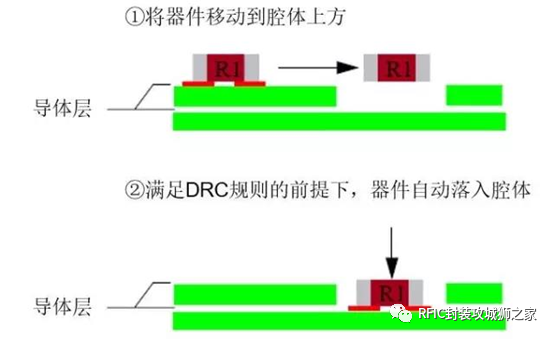

具體在設計中怎么實現呢?大致分為三步:

- 在基板上繪制正常的開放式腔體;

- 將元器件放置到腔體中,器件自動落入腔體;

- 將腔體屬性更改為封閉式腔體。

設計方法看起來是不是很容易,這種技術適合所有的芯片類型,具體設計方法可參考《SiP系統級封裝設計與仿真》一書第12章。

5.2 通過特殊材料制作電阻、電容等無源器件并嵌入到板層之間

這種技術目前應用也很廣泛,主要是通過阻性、容性材料制作電阻或者電容,然后在基板層壓的時候,嵌入到基板內部層之間或者直接制作在基板表面,這種方法制作的阻容基本沒有高度,不會影響基板的厚度。

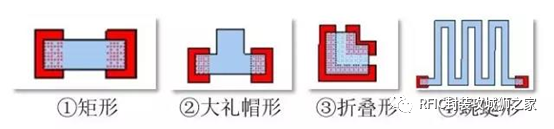

下圖是4種常見的電阻形狀,注意不同的阻值要選擇合適的阻性材料,才能做出大小合適的埋入式電阻。

下圖是3種常見的電容結構,同樣要選擇合適的材料,才能做出結構和大小都合適的埋入式電容。

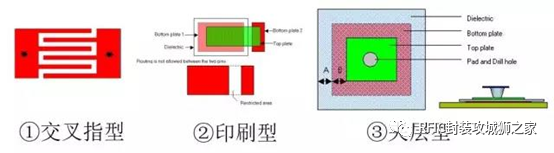

目前在國內,平面式埋置電阻應用比較多,在SiP、MCM、厚膜、薄膜電路中應用普遍,一般制作在基板的表面層,這樣方便后續的激光調整。平面式埋置電容應用相對較少,主要是工藝比較復雜,例如印刷型電容需要至少3層材料,而夾層型更為復雜,除了多層材料外,還需要通過過孔將相鄰的層連接起來。

在設計工具方面,Mentor的工具對此功能支持的比較好,全部在菜單中即可完成電阻、電容的自動綜合功能。

另外,采用第二種方法,需要對材料特性有比較詳細的了解,下圖列出了部分阻容材料,不同的材料有不同的特性,只有選擇了合適的材料,才能做出最優的埋置電阻或電容。具體設計方法可參考《SiP系統級封裝設計與仿真》一書第15章。

6 芯片堆疊技術在SiP中的應用

芯片堆疊技術在SiP中應用的非常普遍,通過芯片堆疊可以有效降低SiP基板的面積,縮小封裝體積。

目前來看,芯片堆疊的主要形式有四種:金字塔型堆疊,懸臂型堆疊,并排型堆疊,硅通孔TSV型堆疊。

為什么芯片可以進行堆疊呢?這里面我們講的主要是未經過封裝的裸芯片。曾經有用戶問我,封裝好的芯片可不可以進行堆疊呢?一般來說是不可以的,因為封裝好的芯片引腳在下表面直接焊接到基板上,而裸芯片的引腳一般在芯片上表面,通過鍵合的方式連接到基板。正是由于裸芯片引腳在上方,和基板的連接方式比較靈活,才有了芯片堆疊的可行性,參看下圖。

6.1 金字塔型堆疊

金字塔型堆疊是指裸芯片按照至下向上從大到小的方式進行堆疊,形狀像金字塔一樣,故名金字塔型堆疊,這種堆疊對層數沒有明確的限制,需要注意的是堆疊的高度會受封裝體的厚度限制,以及要考慮到堆疊中芯片的散熱問題。金字塔型堆疊參看下圖。

6.2 懸臂型堆疊

懸臂型堆疊是指裸芯片大小相等,甚至上面的芯片更大的堆疊方式,通常需要在芯片之間插入介質,用于墊高上層芯片,便于下層的鍵合線出線。這種堆疊對層數也沒有明確的限制,同樣需要注意的是堆疊的高度會受封裝體的厚度限制,以及要考慮到堆疊中芯片的散熱問題。懸臂型堆疊參看下圖。

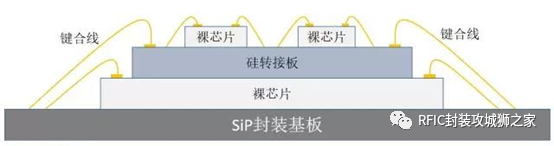

6.3 并排型堆疊

并排堆疊是指在一顆大的裸芯片上方堆疊多個小的裸芯片,因為上方小的裸芯片內側無法直接鍵合到SiP封裝基板,所以通常在大的裸芯片上方插入一塊硅轉接板,小的裸芯片并排堆疊在硅轉接板上,通過鍵合線連接到硅轉接板,硅轉接板上會進行布線,打孔,將信號連接到硅轉接板邊沿,然后再通過鍵合線連接到SiP封裝基板。并排型堆疊參看下圖。

6.4 硅通孔TSV型堆疊

硅通孔TSV型堆疊一般是指將相同的芯片通過硅通孔TSV進行電氣連接,這種技術對工藝要求較高,需要對芯片內部的電路和結構有充分的了解,因為畢竟要在芯片上打孔,一不小心就會損壞內部電路。這種堆疊方式在存儲領域應用比較廣泛,通過同類存儲芯片的堆疊提高存儲容量。目前也有將不同類芯片通過TSV連接,這類芯片需要專門設計才可以進行堆疊。TSV型堆疊參看下圖。

上面介紹的是SiP設計中四種最基本的芯片堆疊方式。

在實際應用的時候,這幾種堆疊方式可以組合起來形成更為復雜的堆疊。另外,還有通過將鍵合芯片和倒裝焊芯片進行堆疊,通過柔性電路折疊的方式對芯片進行堆疊,以及通過POP形式的堆疊等幾種,這些芯片堆疊方式在SiP設計中也比較常見。

7 SiP設計仿真流程

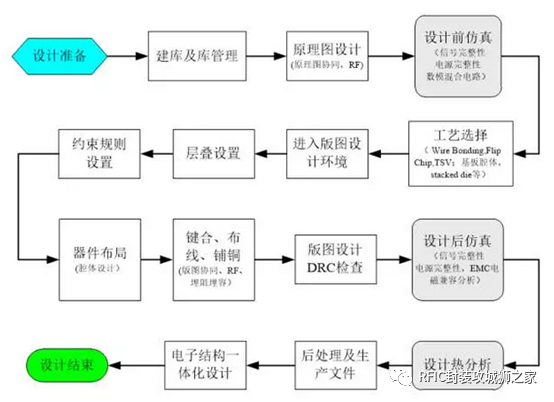

SiP設計與仿真流程的主要內容如下圖所示:

- 設計準備

設計準備的工作主要包括:① 各種資料的收集,裸芯片相關資料,管腳定義,物理尺寸,能否采購獲取等。②封裝類型的確定,是采用BGA封裝還是其他封裝形式;封裝尺寸的確定;封裝管腳間距、管腳數目的確定。③采用自定義管腳排列方式還是采用標準的封裝,或者和別人曾經用過的封裝管腳兼容,以便于后期的組裝和測試。④封裝工藝和材料的選擇,根據其應用的領域選擇塑封、陶瓷封裝或者金屬封裝。

- 建庫及庫管理

建庫及庫管理主要包括原理圖符號庫、IC裸芯片庫、BGA封裝庫、Part庫以及仿真模型庫等。

- 原理圖設計

原理圖設計包括原理圖輸入,射頻原理圖設計以及原理圖協同設計等。

- 設計前仿真

設計前仿真可和原理圖設計同步進行,通過“What if”分析,確定設計層疊結構、關鍵信號的網絡拓撲結構、阻抗匹配,以及電源平面的分割、電容種類及型號選擇等。對模擬電路或者數模混合電路,可進行電路的功能仿真。

- 工藝選擇

工藝選擇主要是為了確定SiP采用哪種工藝的封裝形式,如Wire Bonding、FlipChip、TAB、TSV等。基板上是否要挖腔體,采用單面腔體還是基板頂層/底層雙面腔體,以及腔體的深度等,同時也要考慮是否要做芯片堆疊Stacked Dies,基板的層數和需要采用的層疊結構等通常在這一步也要定下來。

- 進入版圖設計環境

通過打包Package功能,以及前向標注等手段將原理圖的連接關系、規則定義等傳輸到版圖環境,同時自動調用中心庫的相關 Cell放到版圖設計環境中。

- 層疊設置

根據工藝的選擇及設計的復雜程度進行層疊結構的設置,包括層數以及層疊結構的選擇,是采用1+N+1、2+N+2、m+N+m或者ALIVH等層疊結構。

- 約束規則設置

主要包括網絡分類,結構約束規則、間距約束規則、電氣約束規則,高速網絡約束、差分對約束等。

- 器件布局

主要確定裸芯片的擺放位置。如果芯片需要放置到腔體里,則需要確定腔體的深度以及是單級還是多級腔體,腔體形狀的繪制等。

- 引線鍵合、布線和敷銅

主要確定鍵合線的鍵合方式,是單層鍵合線還是多層鍵合線,鍵合線的模型選擇,電源環的設置;選擇交互式手工布線或自動布線,電源平面層分割,射頻電路設計,埋阻埋容的自動綜合等。這一步工作量比較大。

- 版圖設計檢查

通過檢查可發現版圖設計中的DRC錯誤并進行修正,確保設計功能的正確性。

- 設計后仿真

設計后仿真可通過專用接口導出到仿真工具,進行信號完整性、電源完整性及電磁兼容方面的仿真和分析。

- 設計熱分析

可通過專用接口導入熱分析工具。通過熱分析,可解決SiP工作中由于芯片功耗過大而發生的過熱問題,確保產品的穩定性和可靠性。

- 后處理及生產文件

包括Gerber及鉆孔文件的生成,BOM、DXF、IDF、GDSII、ODB++等格式的輸出。

- 電子結構一體化設計

電子結構一體化主要包括電子和結構的協同。因為EDA工具主要完成的是SiP內部的東西,包括基板和芯片組裝、鍵合等。而SiP的外殼等數據通常需要通過結構設計軟件來確定,如陶瓷封裝的金屬框架、蓋板、塑封的模封,金屬封裝的外殼等。

- 設計結束

所有上面的流程走完之后,SiP設計結束,即可進入生產階段。

目前,在國內,越來越多的電子設計工程師開始關注和學習SiP的技術,但由于目前關于SiP設計和仿真方面的綜合書籍很缺乏,設計者往往無從下手,這在一定程度上也阻礙了SiP技術在國內的快速發展。Mentor Xpedition是一款專業的SiP設計工具,包括原理圖設計、版圖布線設計、電學分析及熱分析等模塊,可以實現芯片堆疊、基板堆疊、復雜腔體結設計,是一款真正意義上的3D設計工具。

8 SiP 生產流程

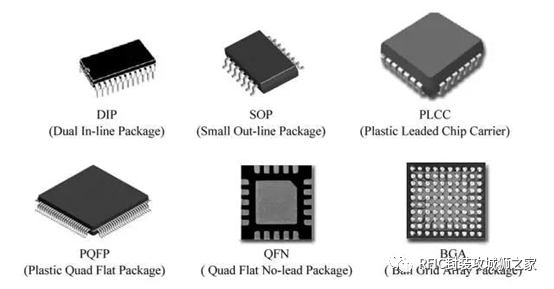

SiP的封裝形式多樣,按照材料和工藝通常分為塑料封裝、陶瓷封裝和金屬封裝三大類,每類都會有多種類型的封裝形式,例如,DIP、SOP、PLCC、QFP、QFN、BGA 等。

當前,隨著引腳數量和密度的增加,BGA成為SiP最常采用的封裝形式。

下面,我們就以BGA塑料封裝的SiP生產流程作為介紹,基本上就可以代表SiP封裝的基本生產流程,其它封裝形式流程大同小異。當然,對于陶瓷封裝和金屬封裝,其工藝流程還是有所區別,我們可以后續再討論。

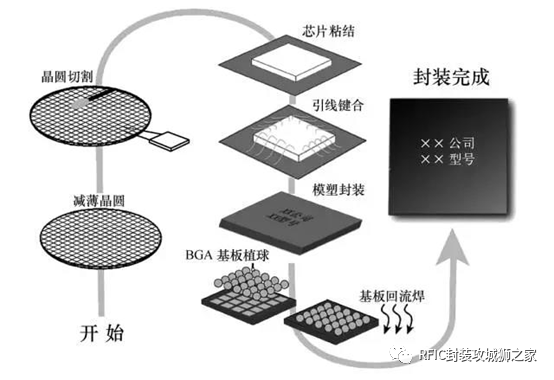

按照裸芯片和基板的連接方式,我們將BGA分為Wire Bonding BGA和FlipChip BGA。

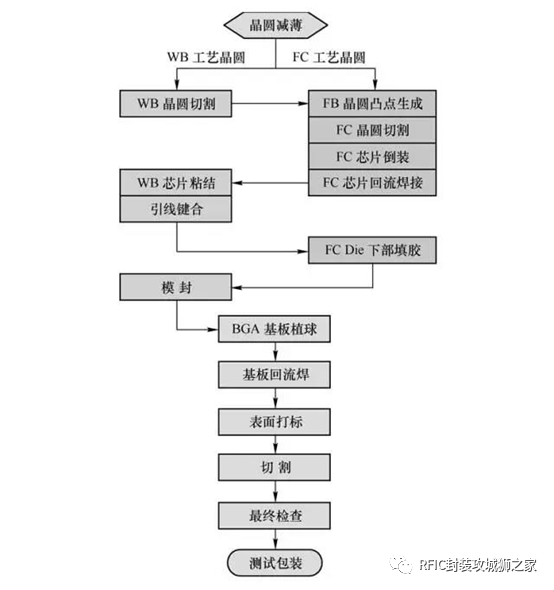

下圖是Wire Bonding BGA(簡稱WB-BGA)的生產制造流程示意圖。

Wire Bonding -BGA的流程包括:晶圓減薄→晶圓切割→芯片粘結→引線鍵合→模塑封裝→BGA基板植球→基板回流焊→表面打標→切割分離→最終檢查→測試包裝。

Wire Bonding -BGA封裝前,晶圓首先會做減薄處理,這樣也更便于晶圓切割,同時也會減小封裝后的厚度。芯片粘結是采用環氧粘結劑將IC芯片粘結在基板上。引線鍵合是采用純金絲鍵合線將芯片管腳與基板上的Pad進行連接,接著采用模塑包封或液態膠灌封,以保護芯片、焊接線和焊盤。BGA基板植球是使用植球機或者篩網將焊料球放置在焊盤上,然后在回流焊爐內進行回流焊接,然后使用清洗劑對基板進行清洗,以去除殘留在封裝體上的焊料和纖維顆粒。然后是表面打標、切割分離,最終檢查、測試和包裝入庫。

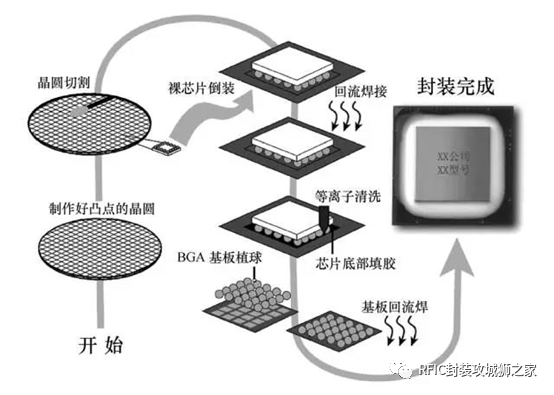

了解完Wire Bonding BGA的生產流程,我們再來看看FilpChip-BGA。

下圖是FilpChip-BGA(簡稱FC-BGA)的生產制造流程示意圖。

FilpChip-BGA的流程包括:晶圓減薄→晶圓凸點生成→晶圓切割→芯片倒裝→回流焊接→裸芯片下部填膠→表面打標→BGA基板植球→基板回流焊→切割分離→最終檢查→測試包裝。

FilpChip-BGA封裝前,晶圓同樣會做減薄處理,然后在晶圓上制作凸點Bump。之后進行晶圓切割,再將芯片倒裝焊接到基板上。焊接好后進行清洗,芯片底部填膠等操作,以固定芯片并克服由于芯片和基板CET不一致而導致的應力。BGA基板植球、回流焊接、清洗、打標、切割、測試、包裝等流程與Wire Bonding-BGA基本一致。

通過兩種工藝的對比,可以看出,兩者的基本的流程是一致的,主要區別在于FlipChip倒裝焊在切割晶圓片之前要生成芯片的凸點,然后進行芯片倒裝、回流焊接等一系列流程。

FlipChip整個工藝流程需要兩次回流焊,包括芯片回流焊和BGA基板回流焊。而Wire Bonding則需要芯片粘結、鍵合、模封等過程,整個工藝流程只需要一次回流焊。

對于SiP系統級封裝,由于是多個芯片,就有可能會遇到混合工藝的情況,即在一顆SiP封裝中既有WB芯片,也有FC芯片。目前,在實際應用中這種情況已經比較常見,在設計中經常會遇到,如所選的裸芯片中有支持WB工藝的芯片,也有支持FC工藝的芯片,就需要做混合工藝SiP的生產制造。

下圖為混合工藝SiP 生產制造流程圖。

-

芯片

+關注

關注

453文章

50406瀏覽量

421824 -

半導體

+關注

關注

334文章

27010瀏覽量

216301 -

元器件

+關注

關注

112文章

4692瀏覽量

92007 -

晶圓

+關注

關注

52文章

4842瀏覽量

127799

發布評論請先 登錄

相關推薦

EMC的三規律和三要素

嵌入式系統的三要素

單片機工作基礎三要素

力的三要素是什么?什么是力?

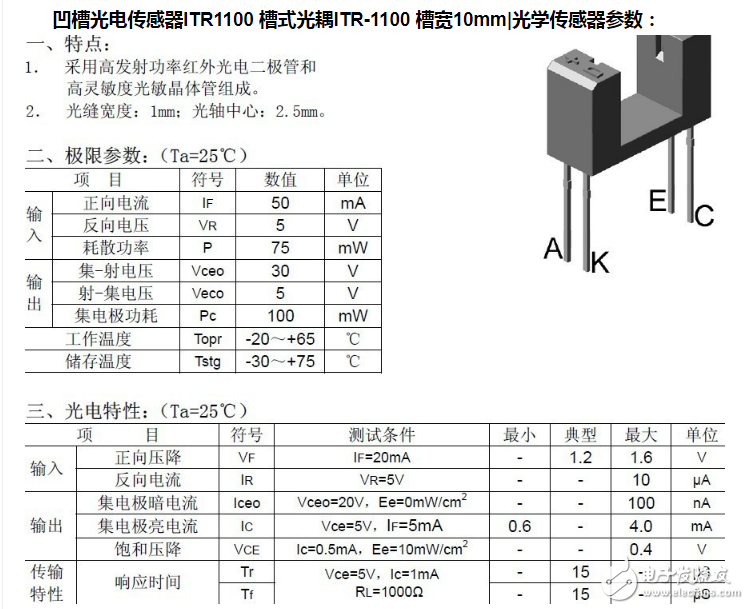

凹槽型光耦選型三要素

簡述SiP項目成功的三要素

簡述SiP項目成功的三要素

評論