專用處理器 (或專用加速器), 顧名思義, 就是用于處理 “特定應用” 的處理器, 相對于通用處理器而言, 這類處理器性能更高、功耗更低、通常價格也更便宜, 但是使用范圍也相對有限。 計算芯片產業在過去 50 年的發展歷程中, 比較成功的專用處理器門類只有數字信號處理器 (DSP)、圖形處理器(GPU) 和網絡處理器 (NPU), 這是 20 世紀 90 年代就已經基本定型的格局。

AI芯片專利技術研發態勢

在過去 5 年中, 用于處理深度學習的神經網絡處理器 (AI 芯片) 也開始快速發展, 比較成功的案例包括 Google 公司的張量處理器 TPU、寒武紀公司的 DianNao 系列深度學習處理器 [5] 等。 專用處理器的最終目標不是替代通用 CPU, 而是與現有的通用 CPU 技術協作, 即將部分 CPU 運行效率低下的應用卸載 (offloading) 到用加速器上運行, 通過構建異構計算平臺來高效地處理計算任務。 從產業生態的視角來看, 相比于通用處理器的硬件與軟件分離的 “水平” 模式, 專用加速器更注重軟硬協同的 “垂直” 發展模式。

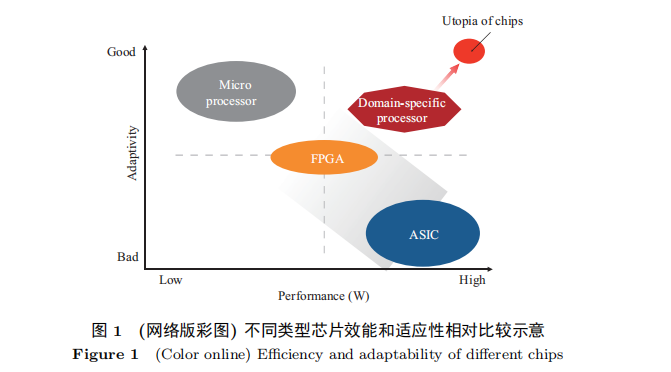

從芯片的效能和適應性兩個維度來刻畫芯片的特征。 這里效能指的是單位功耗下提供的計算能力, 適應性就是通常意義下的通用性。 業界通常將數據處理芯片大體分為三大類: 處理器芯片、ASIC(application specifific integrated circuit) 芯片和 FPGA (fifield programmable gate array) 芯片。

處理器芯片包括 CPU, GPU, DSP 等, 是用戶可編程的芯片; ASIC 是面向特定應用 (application-specifific) 的專用集成電路 [8], 通常也稱之為全定制芯片, 不可編程; FPGA 器件屬于專用集成電路中的一種半定制電路, 是可 “編程” 的邏輯列陣, 利用查找表來實現組合邏輯, 但 FPGA 的 “編程” 與處理器芯片的軟件編程不同, 主要是配置邏輯, 可以理解為硬件編程。

從相對性能來看, ASIC 芯片最好, 處理器芯片最差, FPGA 介于二者之間; 但是從應用的適應性來看, 處理器芯片最好, FPGA 次之, ASIC 芯片最差。

值得注意的是這種分類標準并不是按照電路制造工藝, 例如處理器芯片和 ASIC 芯片本質上都是全定制的集成電路, 處理器芯片本質也是一種 ASIC, 但與通常意義上 ASIC 的最大差別還在于是否具有指令集, 有指令集的就更類似傳統的處理器, 反之就歸類為 ASIC. 此外, 處理器芯片由于其使用廣泛、出貨量大, 與軟件生態聯系尤其緊密, 所以將其獨立為一個大的類別。

無論是 DSP、GPU、AI 芯片、NPU, 還是現在更新的各種 “XPU”, 都是處理數據的芯片, 最終都需要執行二進制代碼的程序來完成計算。 因此專用處理器設計也大都需要涉及如下 6 方面內容:

(1) 約定二進制代碼的格式, 即指令;

(2) 需要將指令變換為機器碼, 即匯編;

(3) 為了提高編程方便程度, 需要將高層程序語言轉換為匯編語言, 即編譯;

(4) 為了提高編程的效率, 提供了各種編程環境, 即集成開發環境 (integrated development environment, IDE);

(5) 充分復用高度優化的代碼, 即應用程序庫;

(6) 為了方便程序調試, 還需要提供各種仿真工具, 即仿真器 (emulator)。

所以, 從系統抽象層次來看, 與通用處理器幾乎沒有區別。 但是不同的 DSIC 側重點不同, 有些 DSIC 只提供 API (application programming interface) 方式的調用, 例如早期的 GPU, 將編譯、匯編等過程全都凝結在運行時庫中,從用戶角度看, 調用過程與使用 OpenCL [9] 中的 “內建核函數 (built-in kernels)” 類似,與調用普通的庫函數過程相同; 雖弱化的可編程性, 但是強化了用戶使用的便利性。 但也有些 DSIC, 如 DSP, 使用了大量底層編程, 雖編程難度高, 但方便精確地性能調優。

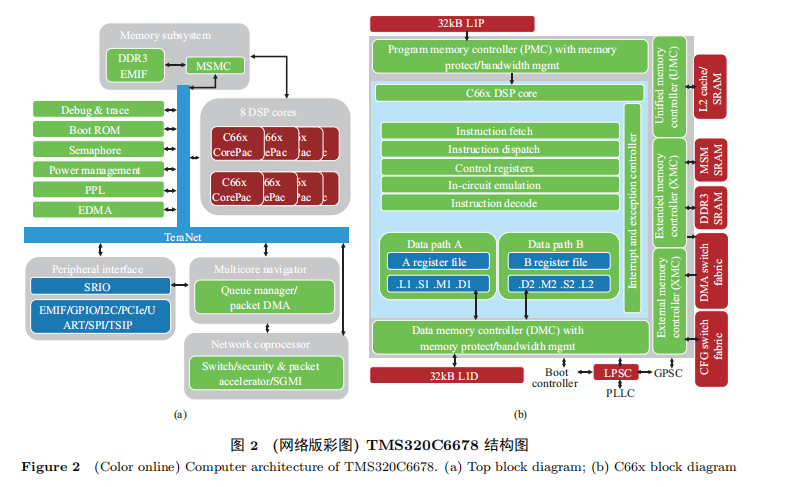

DSP: 靈活的數據格式

DSP 也許是最早出現的專用集成電路。 DSP 的使用范圍非常廣, 從簡單的 MP3 播放器到最新一代的 5G 通信都有使用場景。 常見的 DSP 大多帶有豐富的外設接口, 例如 PCIe、以太網、UART、I2C等, 尤其在很多嵌入式設備中, 豐富的外設接口對于提高系統的集成度、降低成本和功耗都有很大幫助, 所以很多 DSP 產品也演變成帶有豐富外設接口的 SoC (system on chip) 芯片, 如圖 2(a) 所示。

但是 DSP 最大的特點還是進行數字信號處理的核。 大多數 DSP 由于使用場景多為移動設備, 或者只是作為 CPU 系統的數據輸入前端, 在系統中的地位并不高, 通常在功耗、散熱等方面都不可能給予太高容限, 所以功耗敏感、計算位寬對 DSP 很重要, 定點、浮點, 半精度、單精度、雙精度, 16 位、24 位、32 位、40 位等各種數據格式規范 “五花八門”。 在尋址上, DSP 對于數據對齊方式也最靈活, 設置了大量專門的指令對數據進行對齊操作。

TI 公司是 DSP 芯片的龍頭, 被媒體評為是半導體行業利潤率最高的公司。 2019 財年營業總收入144 億美金, 稅后凈利潤高達 50 億美金, 利潤率高達 35%. 作為比較, 同期 Intel 收入 720 億美金, 利潤率 29%; 英偉達總營收 110 億美金, 利潤率 25%. TI 公司的 DSP 主要分為 3 大系列: C2000 系列,集成了 AD 轉換、Flash 存儲等, 主要用于控制馬達、變頻器等工控產品; C5000 系列, 16 位定點, 主要用于便攜聲音、視頻、機頂盒等設備; C6000 系列, 采用了 VLIW (very long instruction word) 架構, 每秒執行指令峰值可達百億條, 主要用于數字通信、圖像增強、傳輸、加密解密等對性能要求更高的場景。 下面就以比較復雜的 C6678 為例做簡要介紹, 其頂層架構如圖 2 所示。

1、通過 VLIW 架構提高性能

在 C6000 系列的 DSP 中, 采用了超長指令字 (VLIW) 技術, 性能的提升主要是通過引入 SIMD(single instruction multiple data) 來實現。 從 2 路 16 位、4 路 8 位 SIMD 操作, 到 8 路 16 位、4 路 32 位向量操作。 為了支持較寬的向量化操作, C66x 系列 DSP 設置了 8 個功能單元、兩組寄存器堆文件、兩條獨立數據通路; 每組寄存器文件包含 32 個 32 位通用寄存器, 而且可以支持 8, 16, 32, 40, 64 位等非常靈活的數據位寬打包存儲。 例如一個完整 32 位寄存器連同相鄰寄存器的低 8 位存儲一個 40 位的浮點數, 同時相鄰寄存器的高 24 位還可以用于存其他的數。 乘法器支持 128, 40, 64 位數據。 顯然支持那么多 “非標” 的定點和浮點數, 如何來安排寄存器的分配成為一個很有挑戰的問題。

2、指令緩存和程序緩存分離

將指令與數據分離也就是著名的 “哈佛結構”, 一級程序緩存 (L1P) 采用直接映射, 一級數據緩存(L1D) 采用多路組相連。 這樣導致了緩存替換策略的不同, L1P 采用新緩存行替換同一位置的舊緩存行, 采用讀 – 分配 (read-allocate) 策略。 相較而言, L1D 復雜的多, 采用了最近最少使用 (least recently used, LRU) 替換策略和回寫 (writeback) 機制: 當數據被更新時, 并不立即更新相應的緩存位置和存儲器地址, 而只做 “dirty” 標記, 只有數據被替換出緩存, 或者手動啟動一致性操作指令, 或出現長距離訪問 (此時所有高速緩存的局部性都極有可能被破壞), 才會寫回到存儲器。 這也說明指令的局部性是比數據的局部性顯著得多, 而且對于核而言, 指令緩存是只讀的, 而數據緩存可讀可寫, 從這個意義上看, 將二者分開也是有好處的。 此外, DSP 的緩存還支持很多先進的管理功能, 例如強制凍結模式(freeze mode), 可以防止中斷程序破壞已經建立在緩存中的數據局部性, 降低中斷恢復后 “冷啟動” 性能開銷。 這些操作也全都由程序員來完成。

3、硬件指令支持一致性管理

多核并不是 CPU 的 “專利”, C6000 系列也提供多核的 DSP, 由于多核引入會導致數據一致性的問題, C66x 系列 DSP 也提供了柵欄指令 (MFENCE) 來處理緩存回寫, 強制或阻止一致性操作的執行等, 方便程序員管理數據一致性。

4、硬件化的帶寬管理防止運行阻塞

DSP 核中還設置了硬件化帶寬管理, 負責管理一級數據緩存 (L1D)、一級程序緩存 (L1P)、二級緩存 (L2)、寄存器配置總線等 4 類資源的訪問優先級。 訪問發起方包括 DSP、外部 DMA (enhanced direct memory access, EDMA)、內部 DMA (internal direct memory access, IDMA)、數據一致性操作。

管理按照每次訪問授予優先級, 而不是按照訪問類型固定優先級, 通過設置競爭強度計數器來反映對資源的 “饑渴” 程度, 即便是最低優先級的訪問, 隨著等待時間增加, 優先級就會逐漸升高, 當達到最長等待周期數, 就會強制授予一次訪問。 而這些都是硬件管理的, 程序員只能設置最長等待時間, 不能設置競爭計數器。 這樣的硬件化維護資源公平性的設置在 CPU 中并不常見。

由以上分析可以看出, DSP 作為一類典型的專用處理器, 其結構與數字信號處理需要豐富的 IO接口便于集成, 強大的浮點處理能力支持高帶寬的信號處理, 還提供了豐富的底層數據通路的控制手段方便專業用戶的性能調優。

審核編輯 :李倩

-

處理器

+關注

關注

68文章

19178瀏覽量

229200 -

asic

+關注

關注

34文章

1195瀏覽量

120347 -

神經網絡

+關注

關注

42文章

4765瀏覽量

100565 -

數據處理

+關注

關注

0文章

583瀏覽量

28531

發布評論請先 登錄

相關推薦

0.5mm層疊封裝應用處理器的PCB組裝指南,第II部分

dsp和嵌入式微處理器的區別和聯系 嵌入式微處理器應用領域分析

dsp與單片機,嵌入式微處理器的區別

dsp和嵌入式微處理器的區別和聯系

dsp和嵌入式微處理器的區別是什么

芯來科技正式發布首款專用處理器產品線Nuclei Intelligence系列

DSP篇:專用處理器比較分析(2022)

DSP篇:專用處理器比較分析(2022)

評論