01什么是串擾?

串擾是 PCB 的走線之間產(chǎn)生的不需要的噪聲 (電磁耦合)。

串擾是 PCB 可能遇到的最隱蔽和最難解決的問題之一。最難搞的是,串擾一般都會發(fā)生在項目的最后階段,而且通常以斷斷續(xù)續(xù)或不易重現(xiàn)的方式發(fā)生,對于工程師來說,盡早解決 PCB 上串擾發(fā)生的所有原因非常重要。

串擾會對時鐘信號、周期和控制信號、數(shù)據(jù)傳輸線和 I/O 產(chǎn)生不良影響。通常來講,串擾是無法完全消除的,只能盡量減少串擾。

02串擾的機制

1、耦合

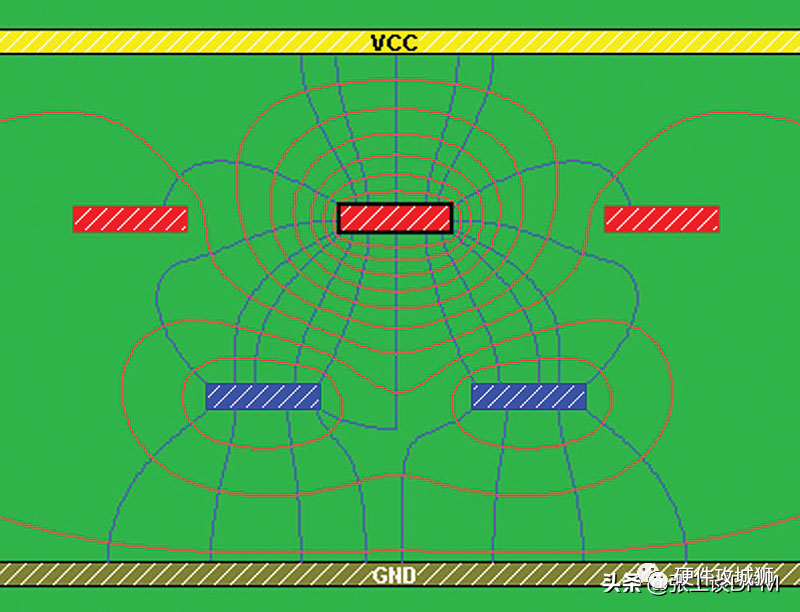

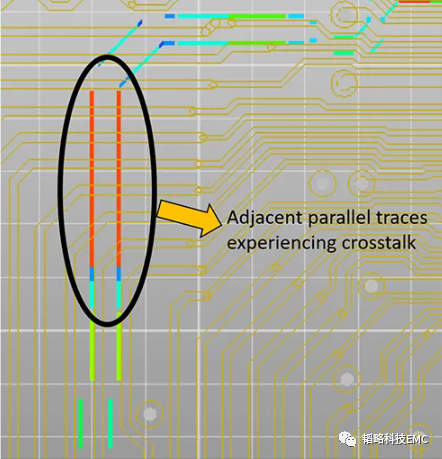

影響一條走線的過大電壓或電流會對另一條走線產(chǎn)生不良影響,但是這兩條走線之間沒有物理接觸,每當兩個網(wǎng)絡(luò)彼此相鄰運行任何顯著長度時,都可能出現(xiàn)這種 耦合。當信號在其中一條線上驅(qū)動時,它產(chǎn)生的電場和磁場會導(dǎo)致意外信號也出現(xiàn)在附近的線上,如下圖所示:

當兩條或更多條相鄰跡線耦合在一起時會發(fā)生串擾

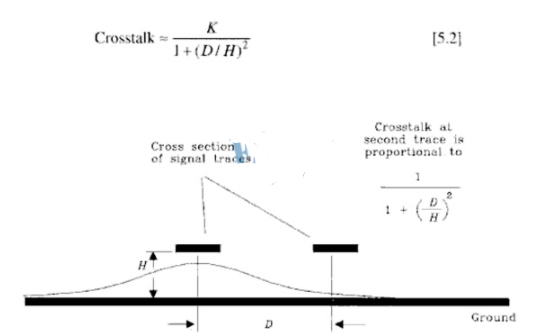

2、電容耦合

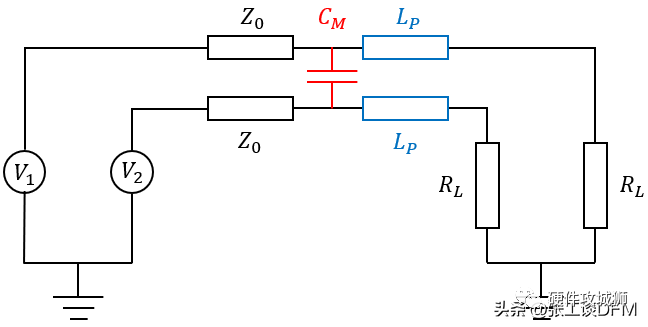

下面的電路圖顯示了 如何使用電路理論來模擬不同類型的串擾 。在該圖中,兩條跡線之間存在一些寄生電容,這是由于跡線之間的寬邊耦合而存在的。因為每條跡線都是一個導(dǎo)體環(huán)路,所以每條跡線就像一個電感器并具有一些寄生電感。兩個并聯(lián)電感具有一定的互感,它定義了兩條走線之間的電感耦合強度。

電路圖顯示了描述 PCB 中不同類型串擾的經(jīng)典電路模型

電容耦合不僅僅意味著顯示由走線邊緣產(chǎn)生的等效電容,盡管這確實有助于互電容。每條跡線的本機電容和寬邊電容相結(jié)合得出總互電容;它們?nèi)看?lián)并耦合回地平面。

當串擾發(fā)生并被觀察為時域中的快照時,很難區(qū)分電容和電感對串擾的貢獻。

3、“攻擊者”信號或走線切換

串擾是一種特別難以預(yù)測和控制的現(xiàn)象,除非它是模擬的,因為幾乎沒有辦法直觀地知道由于給定的耦合會產(chǎn)生多少串擾電壓和電流。

用串擾的說法, “攻擊者”信號或跡線切換并導(dǎo)致串擾。“受害者”信號或軌跡通過產(chǎn)生一個意外信號來做出響應(yīng)。 效果本質(zhì)上是三維的。受害者可以在同一層相鄰,也可以在攻擊者的上方或下方( 下圖 )。

受害者網(wǎng)絡(luò)可以位于攻擊者網(wǎng)絡(luò)的上方、下方或附近

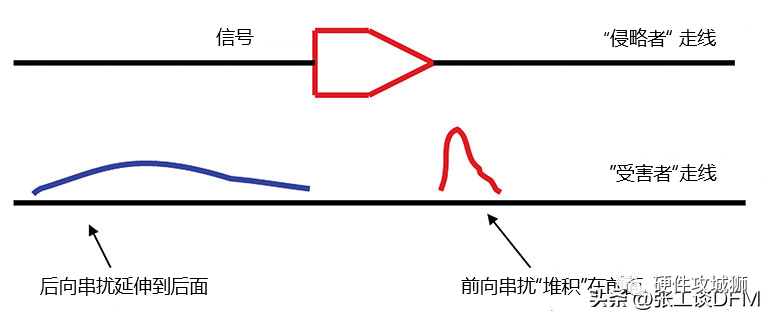

4、前向和后向串擾

實際上,有兩個耦合信號加在受害網(wǎng)絡(luò)上:一個前向信號和一個 后向信號 。 “前向”脈沖與干擾信號一起傳播,而“后向”脈沖從干擾信號返回。 受害遠端的串擾稱為“遠端串擾”或 FEXT,近端的耦合電壓稱為“近端串擾”(NEXT)。下圖顯示了前向和后向串擾。

受害跡線上的前向和后向串擾示意圖

03串擾的原因

1、電容和電感耦合

電容耦合是由于寄生電容,而電感耦合是由于互感。

2、傳播速度差異

傳播速度的差異,可能串擾

3、 PCB 過孔

帶有短截線的 PCB 過孔會產(chǎn)生反射,從而產(chǎn)生振鈴,從而產(chǎn)生串擾。

4、增加的數(shù)據(jù)速率

隨著數(shù)據(jù)速率的增加,上升時間也會增加。根據(jù)法拉第定律,隨著上升時間的增加,串擾也會增加。

5、板尺寸

隨著 PCB 板尺寸的增加,走線長度也會增加,這些走線就像天線一樣。

04減少 PCB 設(shè)計中 串擾的技巧

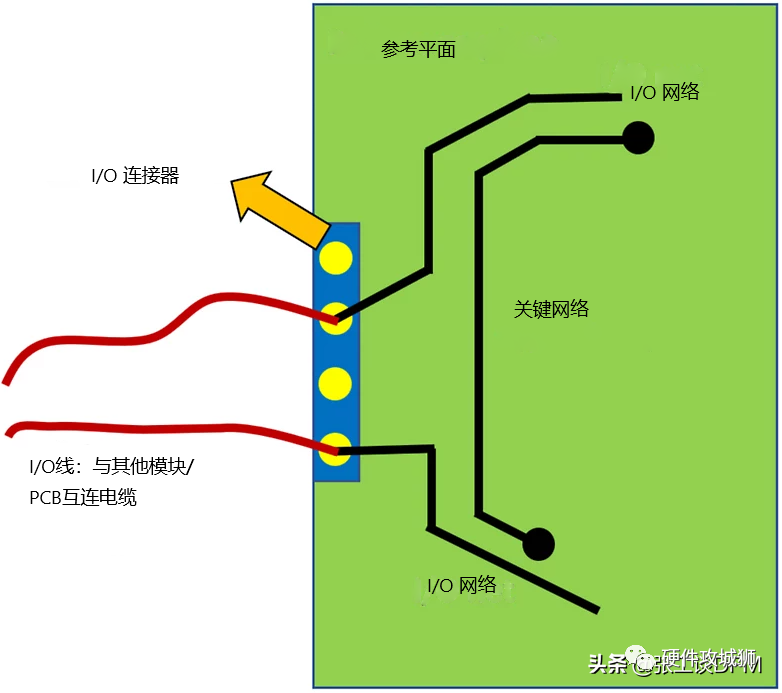

1、檢查靠近 I/O 網(wǎng)絡(luò)的關(guān)鍵網(wǎng)絡(luò)

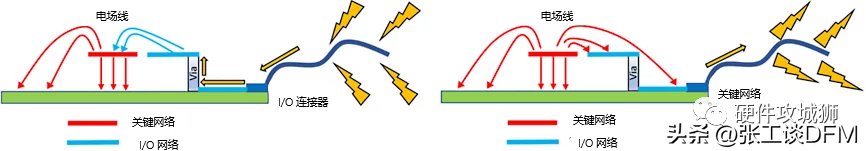

查看與 I/O 線相關(guān)的關(guān)鍵網(wǎng)絡(luò)的布線非常重要 ,因為 噪聲很容易通過這些 I/O 線離開或進入電路板(如下圖)并將 PCB 連接到電路板上或電路板外耦合 。 外部世界與系統(tǒng)中的其他 PCB 或模塊。

關(guān)鍵網(wǎng)絡(luò)和I/O 網(wǎng)絡(luò)彼此靠近布線的場景示意圖

通過 I/O 線進入電路板的任何噪聲都有可能耦合到承載重要數(shù)據(jù)/時鐘信號的關(guān)鍵網(wǎng)絡(luò),這基本上是 PCB 的抗擾性方面(下圖左)。 以類似的方式,任何由關(guān)鍵網(wǎng)絡(luò)傳輸?shù)母咚傩盘柖伎梢择詈系?I/O 網(wǎng)絡(luò),最終通過從板上出來的 I/O 線到達外部世界并進入其他模塊在系統(tǒng)中。 原則上,這將是 PCB 的排放方面(下圖右)。

關(guān)鍵網(wǎng)絡(luò)和 I/O 網(wǎng)絡(luò)接近導(dǎo)致的潛在 EMI/EMC 問題

2、走線間的最小寬度

在定義 PCB 布局時,可以在使用的 CAD 工具中設(shè)置一些規(guī)則 ,例如兩條走線之間的最小距離以及每條走線與板上存在的組件之間的最小距離。 還可以設(shè)置與特定網(wǎng)表或網(wǎng)表將在其中布線的區(qū)域相關(guān)的不同距離值。

PCB 設(shè)計軟件應(yīng)用程序通常包含可以指定差分信號對的寬度和距離的功能,或者可以在哪些 PCB 層上布線網(wǎng)表以及走線可以采用的首選方向。

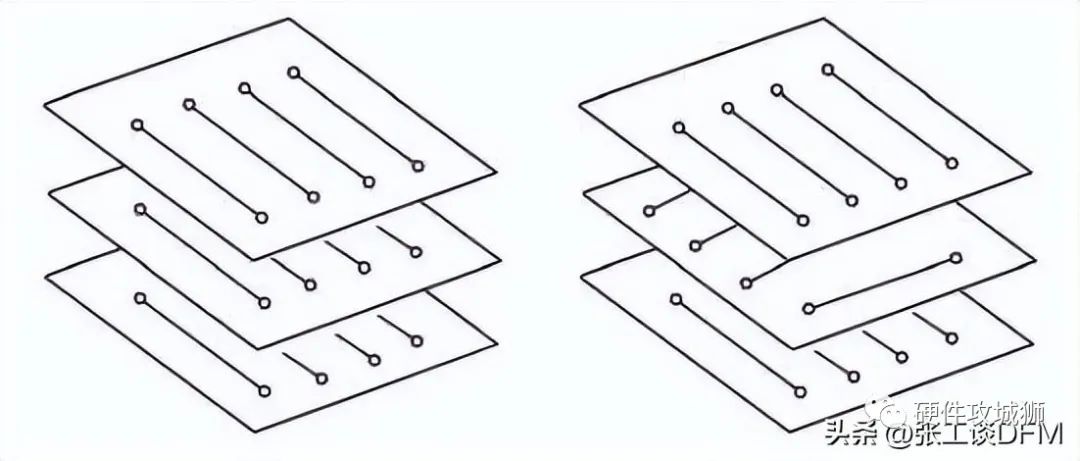

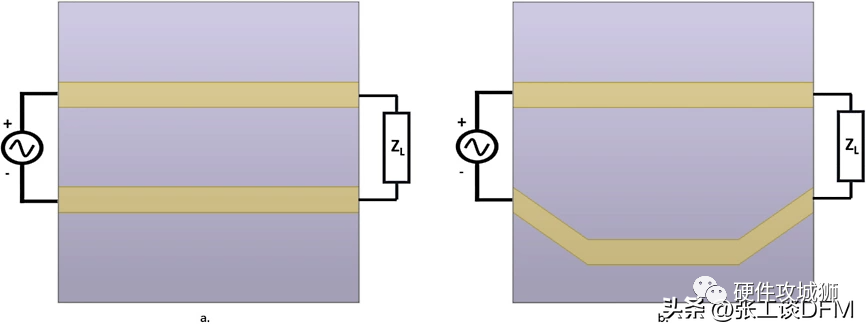

3、保持相鄰層的走線垂直

PCB 層的配置應(yīng)使穿過相鄰層的信號具有相互垂直的方向,絕對避免它們的走線平行。 也有人說,如果一層走線是“從北到南”,那么在它旁邊的一層走線應(yīng)該是“從東到西”。 這個簡單的預(yù)防措施可以讓你將寬邊耦合的影響降至最低。

具體如下圖所示:左側(cè)是要避免的布局,右側(cè)是要應(yīng)用的布局。

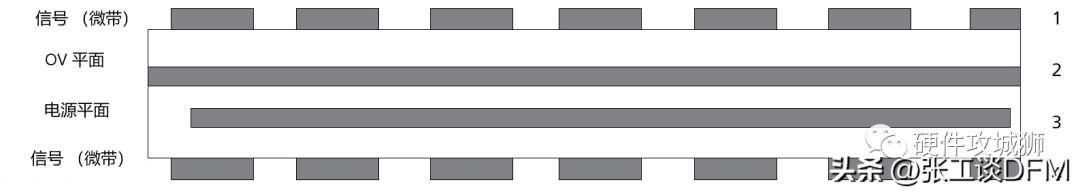

4、使用接地層

在兩個相鄰的信號層之間,最好插入一個接地層(或者,一個電源層),這樣做進一步降低了發(fā)生寬邊耦合的可能性。

該解決方案具有雙重優(yōu)勢,即增加了層之間的距離,并為信號層提供了更好的接地返回路徑。在下圖,我們可以看到一個經(jīng)典的四層 PCB,分為兩個信號層(外部),一個用于接地層(0V)的內(nèi)部層和一個用于電源的內(nèi)部層。

多層 PCB 示例

5、 利用接地返回路徑

雖然這和前面說的有點矛盾,但是可用于減少串擾的替代技術(shù)恰恰在于利用走線之間存在的并行性,將接地返回路徑與高頻信號耦合。

事實上,由于接地返回路徑相對于信號具有相同的幅度但方向相反,因此可以消除影響,從而減少串擾。

6、使用差分信號

另一種保證信號完整性、最小化串擾產(chǎn)生的影響的方法是使用 差分信號 ,即 兩條幅度相同但極性相反的信號線形成一個單一的高速信號。 由于在接收時,信號是作為兩條信號線的電壓之差獲得的,并且由于電磁噪聲對兩條線的影響相同。

因此即使存在明顯的外部噪聲,信號也能保持高度的完整性。 建議是在差分信號對和其他 PCB 走線之間保持盡可能大的距離 。經(jīng)驗法則是選擇至少是軌道寬度三倍的距離。

7、減小平行走線的寬度

在所有無法避免走線之間平行的情況下,都需要保證它們的寬度盡可能的短,從而減少耦合程度。

8、將高頻信號與其他走線隔離

高頻信號(例如時鐘)必須盡可能遠離承載其他信號的走線 。即使在這種情況下,也可以應(yīng)用經(jīng)驗法則,選擇最小距離等于走線寬度的三倍。

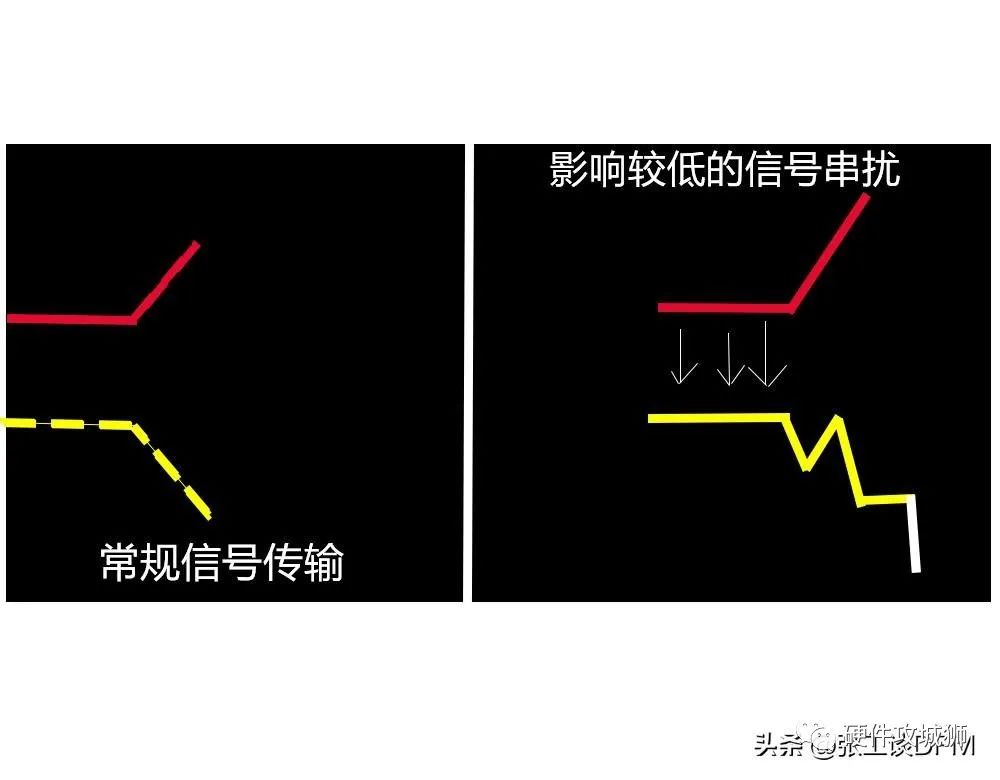

串擾影響信號傳輸

9、盡可能縮短暴露的關(guān)鍵跟蹤長度

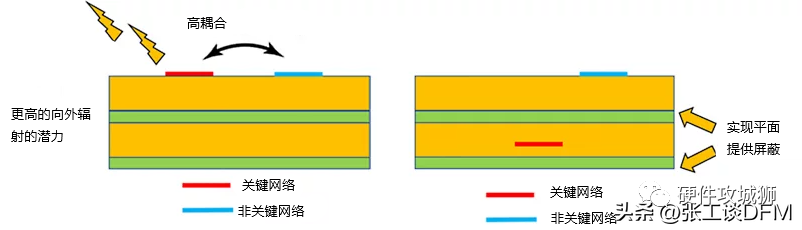

在波長較短的高速 PCB (> 100MHz) 上,任何關(guān)鍵網(wǎng)絡(luò)(參見下圖左)的電氣長度都足以使其成為高效的輻射器,尤其是當暴露在頂層或底層時,這種不需要的輻射可以耦合到任何相鄰的跡線,甚至耦合到靠近跡線的組件中存在的電纜。

建議 將關(guān)鍵網(wǎng)絡(luò)埋在 PCB 內(nèi)層的實心平面之間 ,如下圖右 所示。這有助于控制走線中的場,并避免串擾或 EMI 形式的任何無意耦合。如果暴露關(guān)鍵網(wǎng)絡(luò)是不可避免的,請盡可能縮短暴露部分的長度。這是因為裸露跡線的較短長度將具有較小的輻射趨勢,因為如果它們的電氣尺寸很小,它們將是低效的天線。

在實心平面之間暴露或掩埋關(guān)鍵網(wǎng)絡(luò)的圖示

10、隔離異步信號

異步信號,如復(fù)位或中斷線,應(yīng)使用盡可能遠離高頻信號的走線 。異步信號經(jīng)常被放置在靠近電源線或控制開關(guān)的信號附近,因為這些信號僅用于電路操作的某些階段而不是連續(xù)使用。

11、背鉆過孔

過孔短截線會降低信號完整性,因此會增加串擾,這可以通過實施背鉆來減少。

12、選擇差分對布線

緊密耦合的差分布線消除了串擾,因為來自干擾源的噪聲均等地耦合到差分對的兩個分支中,從而產(chǎn)生共模噪聲。 差分對抑制有助于減少串擾的共模噪聲 。

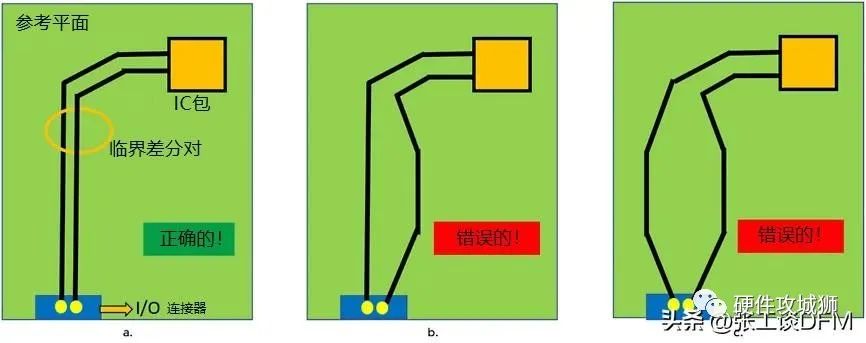

理論上,差分對承載大小相等但極性相反的信號,因為該信號產(chǎn)生的 EMI 可以抵消或可以忽略不計。但是,這僅在線對中的走線長度相等并且盡可能對稱地彼此靠近時才有效。

違反其中任何一項都會產(chǎn)生共模噪聲和 EMI 問題,尤其是對于承載高頻關(guān)鍵信號的差分網(wǎng)絡(luò),因為 EMI 會增加所承載信號的頻率。

下圖顯示了在 IC 封裝和電路板上的出口點(連接器)之間路由關(guān)鍵差分對的正確/錯誤方法的幾個示例。

參考平面存在分裂時的返回電流路徑

關(guān)鍵差分網(wǎng)絡(luò)匹配:模擬和與實際測試要求的關(guān)系

在下圖 PCB 示例中,這里有一個簡單的差分對在 PCB 上以兩種不同方式布線的情況:分別是對稱的和不對稱的。 在這兩種情況下,它們的一端由差分電壓源激勵,另一端由負載端接。

在 PCB 上布線的差分對示例

13、使用保護走線

保護走線用于控制傳輸線之間的電容串擾 。 但是需要謹慎使用,因為使用保護走線會影響。

審核編輯:湯梓紅

-

電路圖

+關(guān)注

關(guān)注

10291文章

10707瀏覽量

524005 -

pcb

+關(guān)注

關(guān)注

4296文章

22778瀏覽量

393372 -

電容耦合

+關(guān)注

關(guān)注

1文章

38瀏覽量

15180 -

串擾

+關(guān)注

關(guān)注

4文章

187瀏覽量

26893 -

走線

+關(guān)注

關(guān)注

3文章

112瀏覽量

23579

原文標題:什么是串擾?如何減少串擾?

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

什么是串擾?如何減少串擾?

高速數(shù)字電路設(shè)計串擾問題產(chǎn)生的機理原因

高速PCB設(shè)計中如何消除串擾?

如何減少電路板設(shè)計中的串擾

如何減少PCB布局中的串擾

淺談層疊設(shè)計、同層串擾、層間串擾

串擾的類型,串擾產(chǎn)生的原因?

減少串擾的方法有哪些

什么是串擾?如何減少串擾?

什么是串擾?如何減少串擾?

評論