MIPI Dsi的使用相比于CSI多了一些寄存器控制,生成的example直接仿真是可以的,但是修改了參數,一些參數也要做相應的調整。這里我們來做個簡單總結 。

(1)BANK電壓要配置成1.2V

(2)輸出要接相應bank的REF_RES管腳。

(3)IP設置關鍵信號說明

| 名稱 | 參數 | 說明 |

| MIPI Parallel Clock frequency | 50~187.5 | 指clk_byte_HS的時鐘頻率。 |

| IP core frequency | 100 | 指mipi_clk的時鐘頻率,指定100MHz |

| Pack Type 48 | Enable,Disable | 使能表示打開48位的數據類型,比如RGB888, |

| Packe Type64 | Enable,Disable |

使能表示打開64位的數據類型,比如RGB565. 如果要全部支持可以同時打開Pack Type48和Packe Type 64 |

| MaximumHorizontalResolution | 行像素的最大個數。一定要注意hactive的長度,如果設置不正確可能無畫面或者畫面偏移。 | |

| FIFOPixelDepthSize | 最大4096 | FIFO的data width是64-bit, MIPIIP里面會緩存2~3行才發出去.所以注意這個值要大于一行的一行數據的2倍或者3倍。 |

| videoTransmission Packet Sequences |

Non-burst mode with SyncPulses, Burst mode, Non-burst mode with Sync Events |

?Non-Burst Mode with Sync Pulses – 讓外設可以精確的重構原始的視頻時序,包括同步脈沖寬度。 ?Non-Burst Mode with Sync Events –與上述類似,但精確重建同步脈沖寬度不是必需的。 ?Burst mode – RGB像素包在時間上有壓縮,留出更多的時間用于LP模式,或者用于復用別的傳輸。 |

(4)修改配置參數

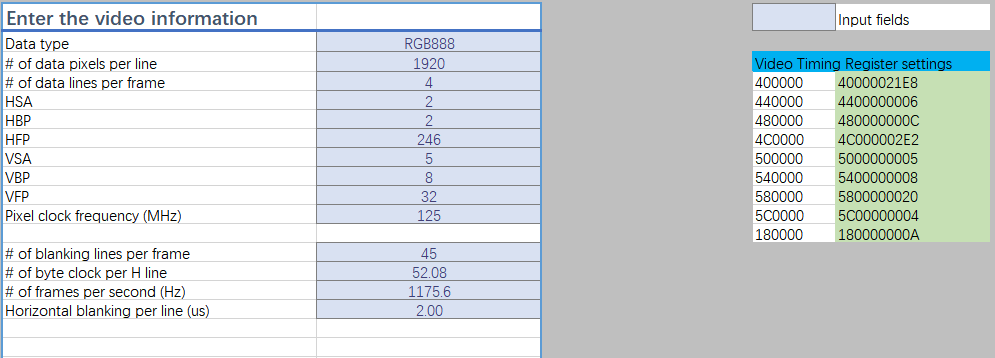

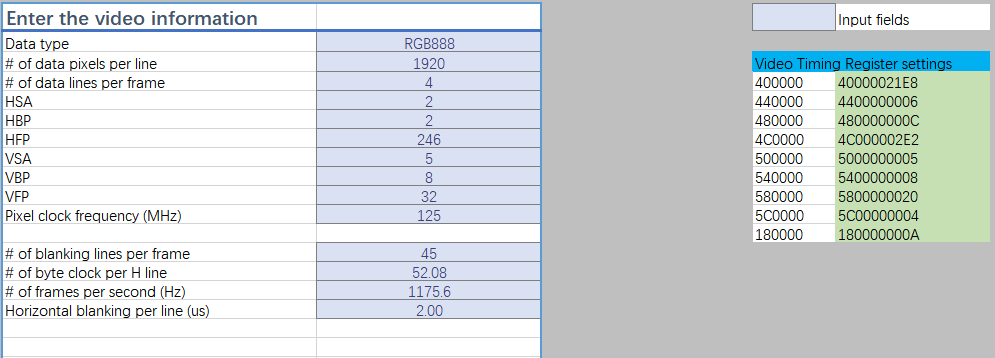

視頻格式如下,可能根據實際的需要進行修改。

parameter MAX_HRES = 16'd1920; parameter MAX_VRES = 12'd4; parameter HSP = 10'd2; parameter HBP = 10'd2; parameter HFP = 10'd246; parameter VSP = 6'd5; parameter VBP = 6'd8; parameter VFP = 6'd32;

修改參數后要在Tianium-mipi-utility文件中驗證,確保文件沒有錯誤提示。

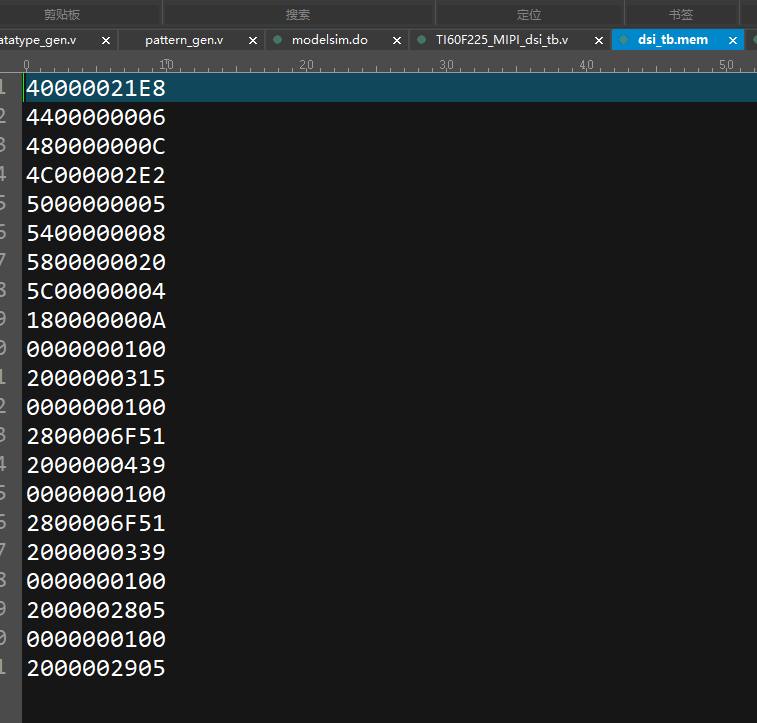

另外要把Tianium-mipi-utility文件中input fields中的信息替換Panel_1080p_reg.mem中的相應信息。這是IP需要的視頻格式信息。

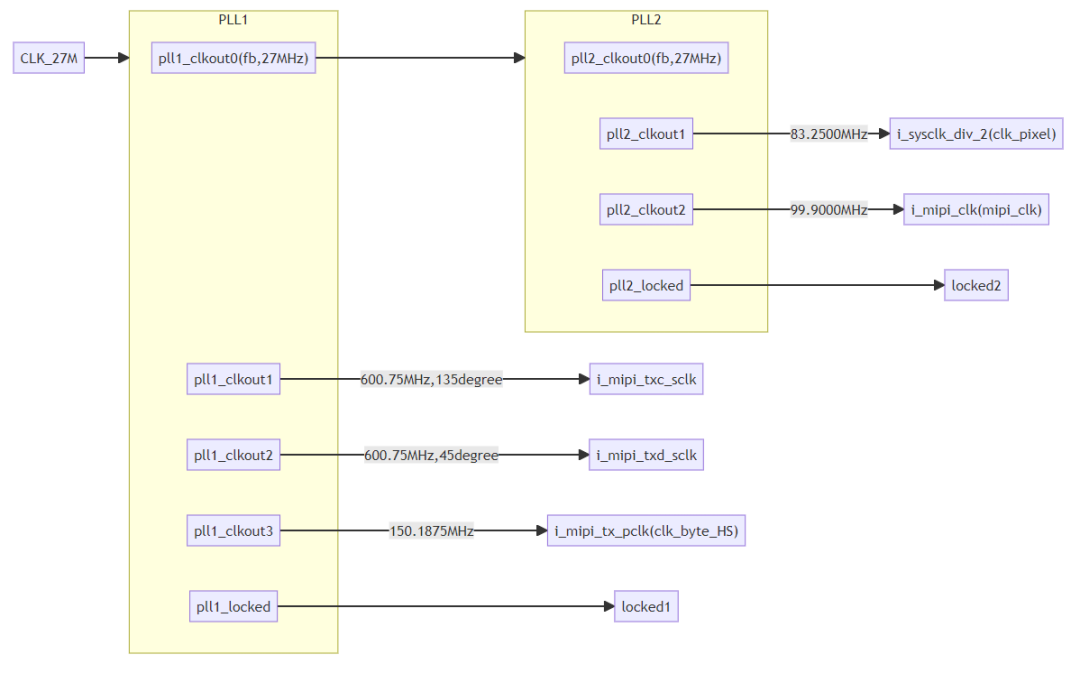

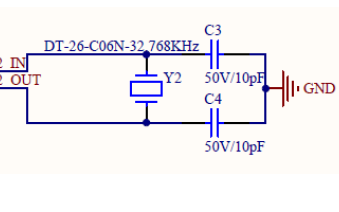

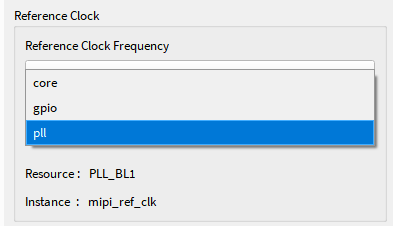

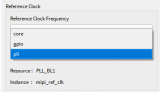

(5)注意修改相應的時鐘

在下面,i_pclk是單像素的時鐘。o_pclk對應MIPI接口的像素時鐘。

i_sys_clk是MIPI AXI接口的配置時鐘。i_mipi_tx_pclk是MIPI發送8位HS數據的并行時鐘。

在使用中可能根據設置參數修改i_pclk,o_pclk和i_mipi_tx_pclk;一般不用修改i_sys_clk。

//video生成時鐘是125M initial begin i_pclk <= 1'b1; forever #4.00 i_pclk <= ~i_pclk; end //轉換成MIPI接口的pixel clock是62.5M initial begin o_pclk <= 1'b1; forever #8.00 o_pclk <= ~o_pclk; end //MIPI配置接口時鐘是50M initial begin i_sys_clk <= 1'b1; forever #10 i_sys_clk <= ~i_sys_clk; end //MIPI時是100M initial begin mipi_clk <= 1'b1; forever #5 mipi_clk <= ~mipi_clk; end //數據速率是1000M initial begin i_mipi_tx_pclk <= 1'b1; forever #4 i_mipi_tx_pclk <= ~i_mipi_tx_pclk; end

(6)所設置的參數既要在Tianium-mipi-utility在評估通過,還要滿足公式

PIX_CLK_MHZ < (DATARATE_MPBS * NUM_DATA_LANE) / PACK_BIT

1)這里的PIX_CLK_MHZ就是指MIPI IP接口的pixel_clk

2)DATARATE_MPBS是指MIPI的數據速率,并非video的帶寬。

3)NUM_DATA_LANE是指傳輸所用的lane數

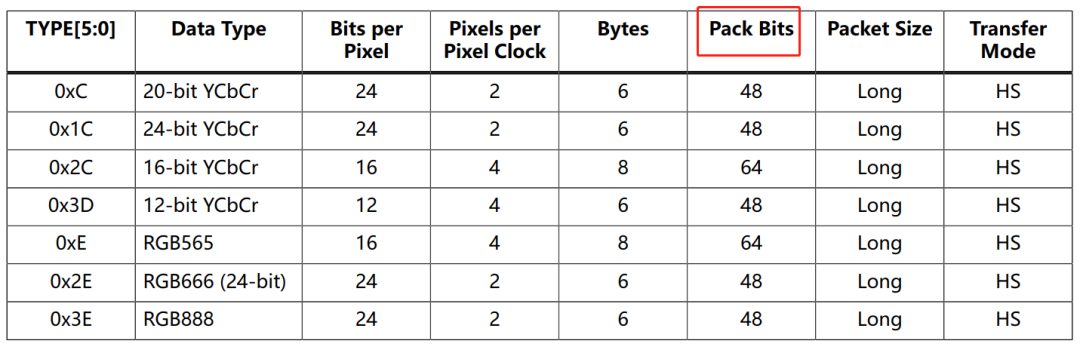

4) PACK_BIT如下,詳細信息請參考MIPI DSI ds。

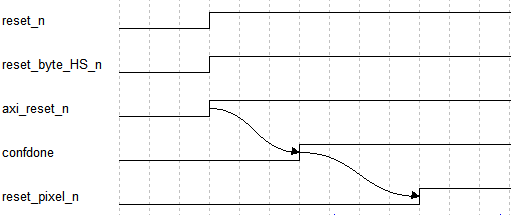

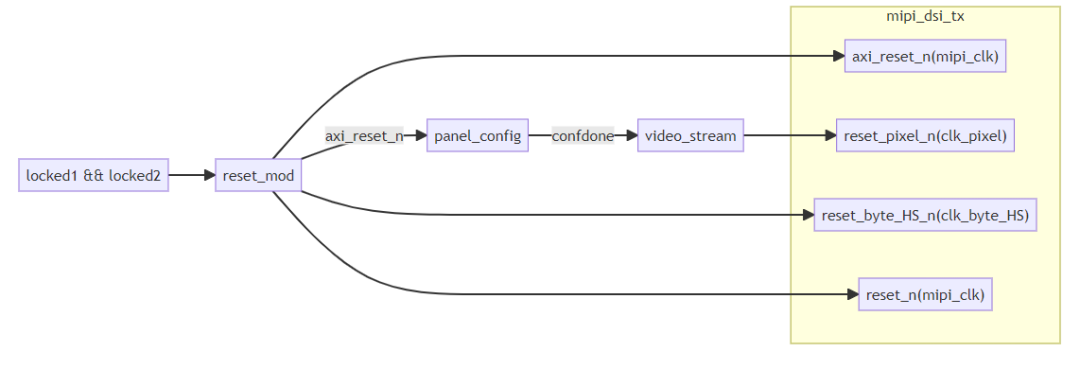

(7)復位處理

復位timing

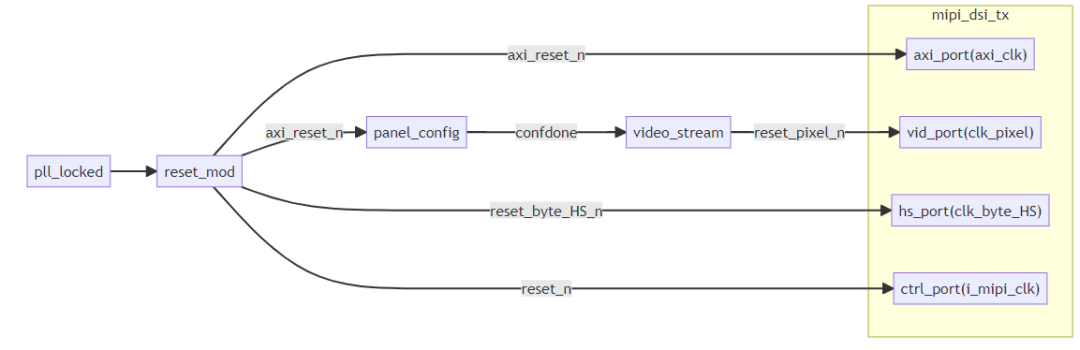

關于DSI_TX復位處理:

1)reset_n,reset_byte_HS_n和axi_reset_n先釋放;

2)等待panel_config的o_confdone拉高,也就是panel_config配置完成

3)通過confdone拉高來釋放video_stream的復位

4)confdone可以用于reset_pixel_n,也可以通過video_stream的輸出的vs信號,在vs為blank時釋放復位。

parameterFRAME_NUM = 5 reg vs_r; reg [10:0] r_vs_cnt; wire neg_vs; always@(negedge sys_rst_n or posedge i_sysclk_div_2) begin if(!sys_rst_n) vs_r <= 1'b0; else ????????vs_r????<=?vs; end assign neg_vs = {vs_r,vs} == 2'b10; always@(negedge sys_rst_n or posedge i_sysclk_div_2) begin ????if(?!sys_rst_n?) r_vs_cnt <= 16'b0; else if (neg_vs && r_vs_cnt <= FRAME_NUM ) ????????r_vs_cnt????<=?r_vs_cnt?+?1'b1; end always@(negedge sys_rst_n or posedge i_sysclk_div_2) begin ????if?(!sys_rst_n) reset_pixel_n <= 1'b0; ????else?if?(neg_vs?&&?r_vs_cnt?==?FRAME_NUM-1??)?//?? reset_pixel_n <= 1'b1; end

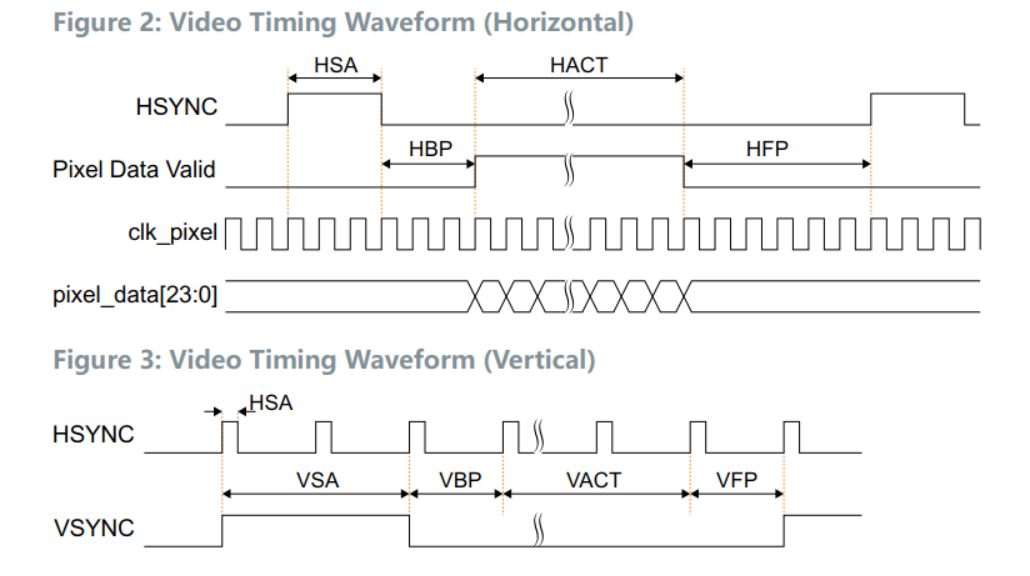

(8) MIPI IP接口的timing時序要求如下:

(9)video接口數據類型格式

視頻格式的順序請參考AN015。

=========================================

example

=========================================

時鐘方案

復位方案

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5325瀏覽量

120048 -

MIPI

+關注

關注

11文章

308瀏覽量

48569 -

FIFO存儲

+關注

關注

0文章

103瀏覽量

5965 -

DSI

+關注

關注

0文章

51瀏覽量

42330

原文標題:MIPI dsi TX移植注意事項 - update4

文章出處:【微信號:gh_ea2445df5d2a,微信公眾號:FPGA及視頻處理】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

1.5G MIPI dsi TX移植注意事項及demo - update8

MIPI解決方案 ICN6202:MIPI DSI轉LVDS轉換芯片

MIPI DSI 轉 LVDS 單路, ZA7783

ICN6202 MIPI DSI轉LVDS的橋接芯片

MIPI dsi TX移植注意事項

MIPI dsi TX移植注意事項 - update7

MIPI dsi TX移植注意事項-update4

MIPI dsi TX移植注意事項-update4

評論