碳化硅 (SiC) 是一種成熟的器件技術,在 900 V 至 1,200 V 以上的高壓、高開關頻率應用中,與硅 (Si) 技術(包括硅超結 (SJ) 和絕緣柵雙極晶體管 (IGBT) )相比具有明顯的優勢。1 最近推出的 650 V SiC MOSFET 產品通過輕松取代 IGBT、從 Si SJ 應用領域中脫穎而出,并在中壓范圍內提供氮化鎵 (GaN) 的替代品,進一步擴大了 SiC 的使用范圍。

當用SiC替換Si器件或使用SiC重新設計時,工程師必須考慮SiC的不同特性、功能和優勢,以確保成功。以下是來自 Wolfspeed 電源專家的 SiC 設計技巧列表。

RDS(ON) 隨溫度的變化

SiC 的一個關鍵優勢是低 RDS(ON),在很寬的溫度范圍內變化僅為 1.3× 至 1.4×而在硅或 GaN 器件中,RDS(ON) 可能會從 25°C 時的額定溫度增加到 120°C 至 140°C 范圍內的實際結溫的兩倍到三倍(圖 1)。因此,仔細檢查數據表并指定正確的I2R或傳導損耗非常重要。

圖1:60 mΩ Si或GaN器件的熱>為120 mΩ,而90 mΩ SiC器件的熱度為120 mΩ。

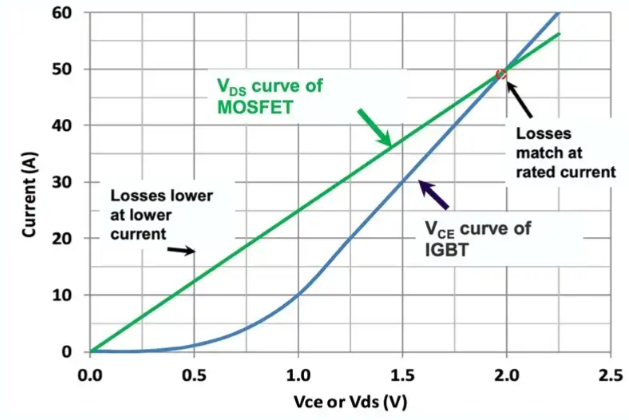

無膝電壓

IGBT針對全額定電流下的熱設計點進行了優化。低于該點的是VCE(sat)指數“拐”電壓曲線(圖2)。碳化硅 MOSFET 的 VDS 特性是線性的,在低于全額定電流的任何點均提供較低的導通損耗。

在設計電動汽車傳動系統時,這一點特別有用,因為其中驅動循環大多低于全額定功率。當并聯使用時,IGBT VCE(sat)曲線加劇了這個問題。

因此,設計人員必須仔細考慮其熱設計點和任務概況。

圖2:Tj = 50°C 時模塊中 50 A IGBT 與 150 A SiC MOSFET 的比較。 在三分之一額定電流下,SiC的損耗是IGBT的一半。

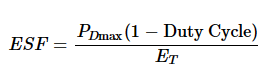

有效開關頻率

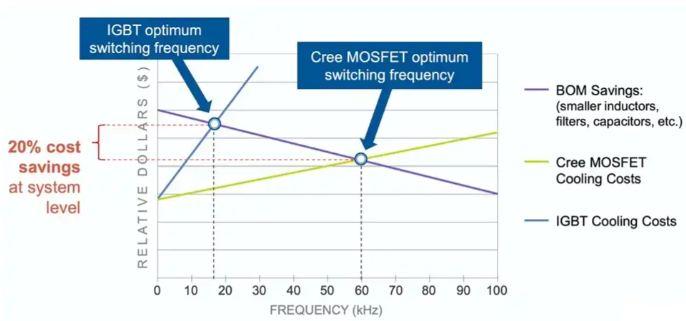

有效開關頻率 (ESF) 定義為硬開關應用中器件在額定I C100 下可以承受的最大頻率,方波占空比為 50%,而不會超過器件在工作電壓下規定的最大功耗。藝術

其中:

有效開關頻率(ESF)定義為硬開關應用中器件在額定IC100下可以承受的最大頻率,方波占空比為50%,而不會超過器件在工作電壓下規定的最大功耗。藝術

圖3:頻率優化考慮了冷卻開關頻率的實際限制和物料清單成本。

與40 mΩ硅器件相比,40 mΩ Wolfspeed SiC MOSFET的理論ESF高10×。雖然這讓我們得以一窺SiC的功能,但冷卻、磁性和成本對開關頻率造成了實際限制。

冷卻成本增加,但電感器和電容器的無源BoM成本隨著開關頻率的降低而降低。對于IGBT,最佳頻率約為18 kHz,冷卻和無源BoM節約曲線在此相交。對于導通損耗較低的 SiC MOSFET,成本權衡的最佳點約為 60 kHz(圖 3)。

設計人員必須注意,最小化電感是有限制的,特別是當系統連接到電網時。雖然SiC器件本身比IGBT更昂貴,但頻率優化設計可在系統級節省20%至25%的成本。

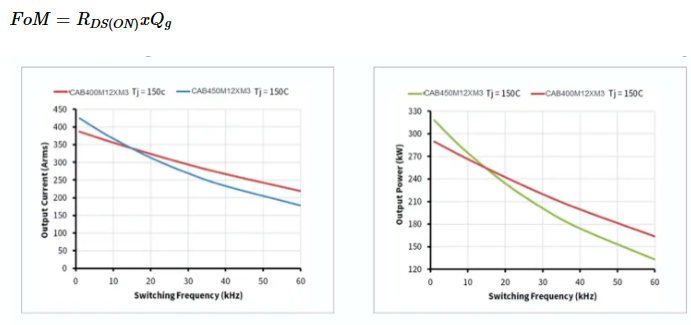

針對應用程序進行優化

MOSFET 的品質因數 (FoM) 由以下公式定義。其背后的想法是,較低的RDS(ON)意味著較低的傳導損耗,而較低的柵極電荷Qg意味著較低的開關損耗。如果他們的產品FoM最小化,總損失就會最小化。

圖4:對于此概念示例,Fsw 為 15 kHz。在分頻點之后,CAB400M12XM3可以提供比CAB450M12XM3更高的安培數。

通過檢查 Wolfspeed 兩個功率密度最高的功率模塊的輸出電流和輸出功率與開關頻率特性,設計人員必須如何仔細選擇適合其應用的最佳產品(圖 4)。450 A CAB450M12XM3 模塊針對極低的 RDS(ON) 進行了優化,但 400 A CAB400M12XM3 模塊針對 FoM 進行了優化。超過 15 kHz,400 A 可提供更高的電流和更高的功率。

對于通常在 20 kHz 以下運行的電機驅動器,高安培數模塊是有效的,但對于在 48 kHz 至 60 kHz 范圍內切換的太陽能逆變器,400 A 模塊是更好的選擇。

VDS 堅固性和降額

IGBT的額定電壓通常為1.2 kV,VDS擊穿電壓接近1.25 kV。Wolfspeed 的 SiC MOSFET 額定電壓為 1.2 kV,但擊穿電壓通常高出數百伏。在航空航天應用中,設計人員必須降額以考慮宇宙輻射的影響,SiC的魯棒性提供了優勢。

反向恢復

在軟開關或使用非對稱設計時,設計人員可能不會太關注它,但反向恢復(Qrr)對于對稱設計非常重要,包括降壓、升壓和圖騰柱PFC。Wolfspeed 650 V SiC MOSFET 在反向恢復時間 T rr 為 11 ns 時具有 16 nC Q rr,而典型的 650 V Si MOSFET 在 T rr 為 13 ns 時具有 725 μC Q rr。

開爾文源極引腳

開爾文源極引腳(盡可能靠近 MOSFET 芯片源極連接的開爾文連接)用于減輕 MOSFET 內部鍵合線引起的電感。為了保持SiC器件的高開關頻率優勢,開爾文源極引腳至關重要。

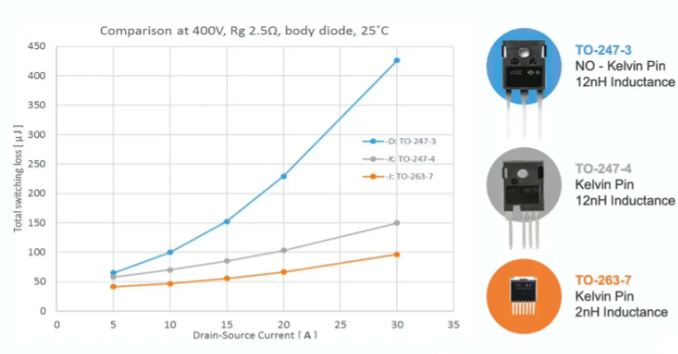

開爾文源極引腳也會影響開關損耗。例如,在 30 A IDS下,無開爾文引腳和 247 nH 源極電感的 TO-3-12 SiC MOSFET 的總開關損耗接近 430 μJ(圖 5)。采用TO-247-4封裝的同一產品(帶有開爾文源極引腳)在相同的IDS上只有150 μJ的開關損耗。改用更小的封裝,如 TO-263-7 或表面貼裝 D2PAK-7,可進一步降低固有的源極電感和損耗。

圖5:開爾文源極引腳有助于避免柵極驅動器環路中的電感,并減少開關能量損耗。

柵極驅動注意事項

驅動SiC MOSFET時,設計人員必須記住,需要負柵極驅動以確保硬關斷,這與硅不同,硅使用正柵極驅動來接通器件。要記住的其他 SiC 特定因素包括:

更快的 dV/dt 和 >100 kV/μs 的額定共模瞬變抗擾度 (CMTI)

峰值連續工作電壓 (V IORM) 高達 1.7 kV

驅動能力通常更高功率,最高可達 10 A

傳播延遲和通道失配時間通常為 <10 ns

有源米勒箝位要求,因為開關速度更高,2 V時閾值略低

由于 SiC 芯片尺寸較小 (<1.8 μs),可實現快速短路保護

除此之外,驅動SiC器件就像驅動硅基器件一樣。

處理電磁干擾

由于SiC器件的目標開關頻率通常較高,并且其上升和下降時間遠短于Si產品,因此工程師可能傾向于認為這會導致更大的EMI問題。

但是,與Si相比,對所需的低頻噪聲或差模EMI濾波器尺寸沒有影響。雖然對輸入端子上的導通模式噪聲有影響,但它僅在兆赫茲范圍內。與硅基器件一樣,這種高頻EMI可以通過使用高頻材料和電容器進行EMI抑制來衰減。

應用范圍廣

如今,SiC 器件用于從 200 kW UPS、180 kW 電動汽車傳動系統和 10 kW 太陽能逆變器到 220 W LED SMPS 等各種應用,所有這些應用均在設計時牢記一些 SiC 設計考慮因素和通常的良好設計原則。

審核編輯:郭婷

-

IGBT

+關注

關注

1265文章

3761瀏覽量

248328 -

晶體管

+關注

關注

77文章

9635瀏覽量

137860 -

碳化硅

+關注

關注

25文章

2701瀏覽量

48886

發布評論請先 登錄

相關推薦

碳化硅電源的設計注意事項

碳化硅電源的設計注意事項

評論