2022年,集成電路半導體行業最熱的頭條是“EDA被全面封鎖”。如何突破EDA封鎖,成為行業發展的關鍵詞,也是群體焦慮。在全球市場,有人比喻EDA是“芯片之母”,如果沒有了芯片,工業發展和社會進步將處處受制,EDA的重要性也上升到了戰略性高度。盡管國際封鎖形勢嚴峻,但睿智的中國科技人擅于把危機化為機會,從《加快自主研發應用,讓工業軟件不再卡脖子》,到《破解科技卡脖子要打好三張牌》,即一要打好“基礎牌”,提升基礎創新能力;二要打好“應用牌”,加強對高精尖國貨的應用;三是要打好“人才牌”,讓人才留得住、用得上、有發展……,各種政策、舉措和實際行動,處處彰顯了我們中國科技的發展韌性。

我們EDA探索頻道,今天迎來了第18期的內容——BSIM4模型,下面就跟著小編一起來開啟今天的探索之旅吧~

在BSIM3的基礎上,UC Berkley的BSIM小組緊接著又推出了BSIM4模型。

BSIM4模型是在BSIM3模型的基礎上發展而來的,主要針對深亞微米到納米的工藝進行了改進和擴展。與BSIM3模型相比,BSIM4模型有以下幾個區別:

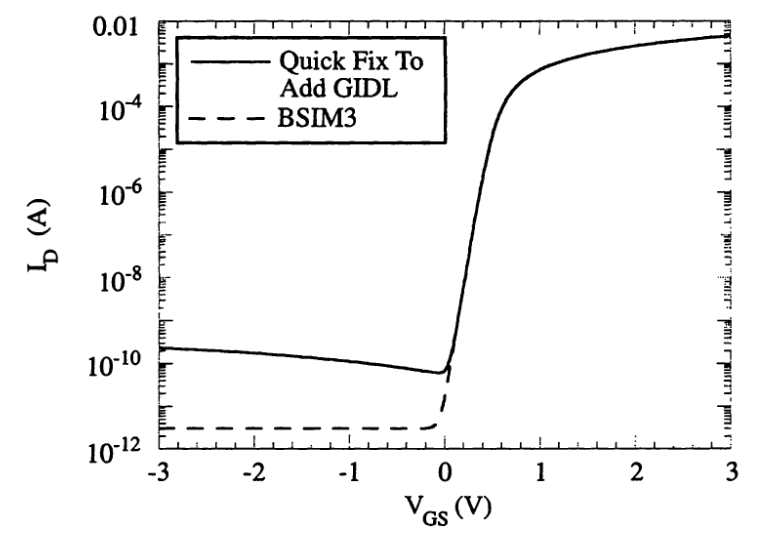

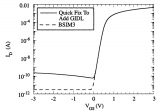

BSIM4模型增加了對多晶硅柵極極化效應、柵極漏電流、柵極隧穿電流、柵極直接隧穿電流等現象的建模。通過對GIDL現象建模,使得在負柵壓下仍可準確預測體電流。工藝發展到90nm節點后,由于柵氧層過薄而引起的柵極隧穿電流不再可忽略,BSIM4建立了詳細的隧穿模型來描述柵極電流。

圖:BSIM4中增加了對GIDL現象的模型(實線),而BSIM3模型則不能描述(虛線)[2]

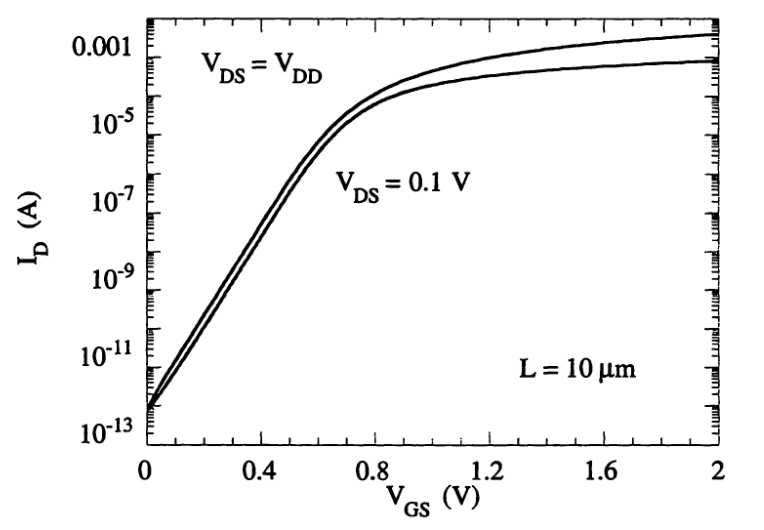

BSIM4模型改進了對短溝道效應、窄溝道效應、溝道長度調制效應、溝道電荷分布效應等現象的建模。BSIM4增添了pocket/retrograde新工藝對閾值電壓的影響,并改進短溝系數以消除閾值電壓roll—up現象。

圖:Pocket Implant引入后仿真的IdVg曲線[2]

BSIM4模型引入了對射頻電路設計相關的參數和效應的建模,如輸出導納、輸出電阻、輸出電容等。BSIM4改進了器件的輸出電阻模型、NQS模型和1/f噪聲模型,并增加了柵電阻、熱噪聲及噪聲分配方案和襯底電阻網絡的描述。

BSIM4模型提供了更多的可選參數和功能,如溫度依賴性、工藝變異性、器件匹配性、噪聲分析等。BSIM4還分析了版圖設計(多finger布圖、串并聯等)對器件寄生參數的影響。

總之BSIM4是對BSIM3的全面提升,一般認為BSM3主要適用于微米、亞微米器件,而BSIM4主要適用于亞微米到納米級平面器件(130nm-20nm)。繼BSIM3之后,BSIM4也被Compact Model Council采納為標準模型。

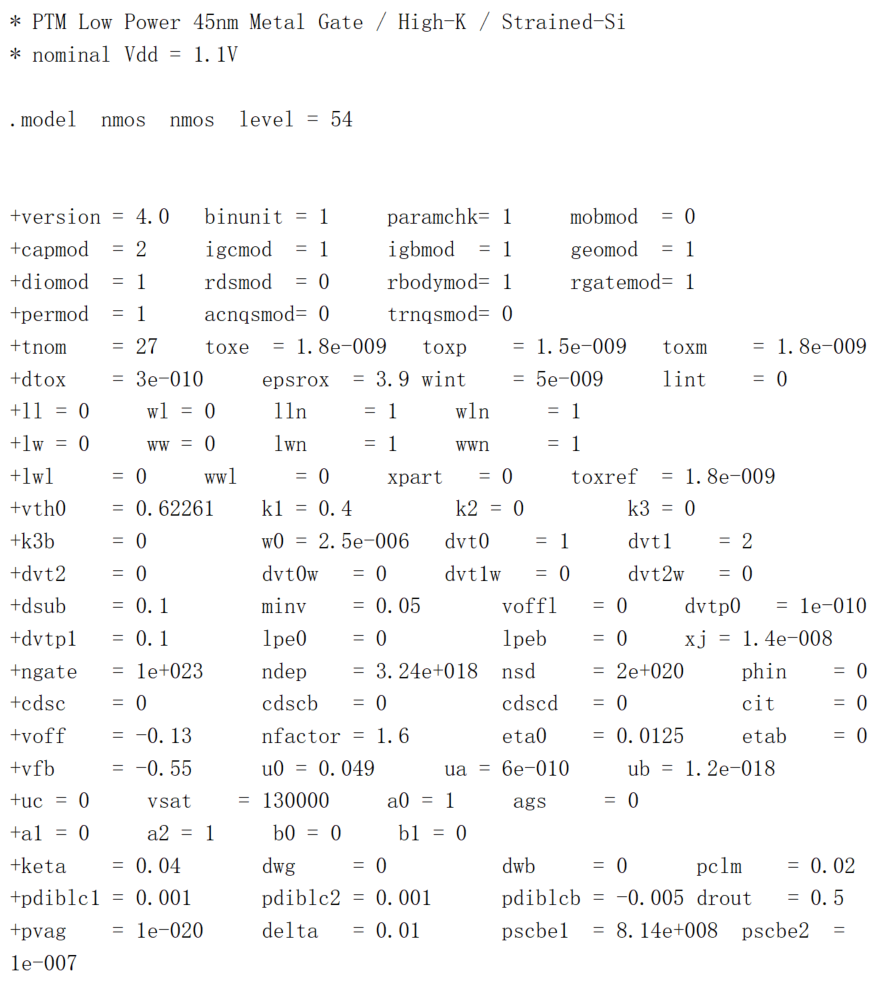

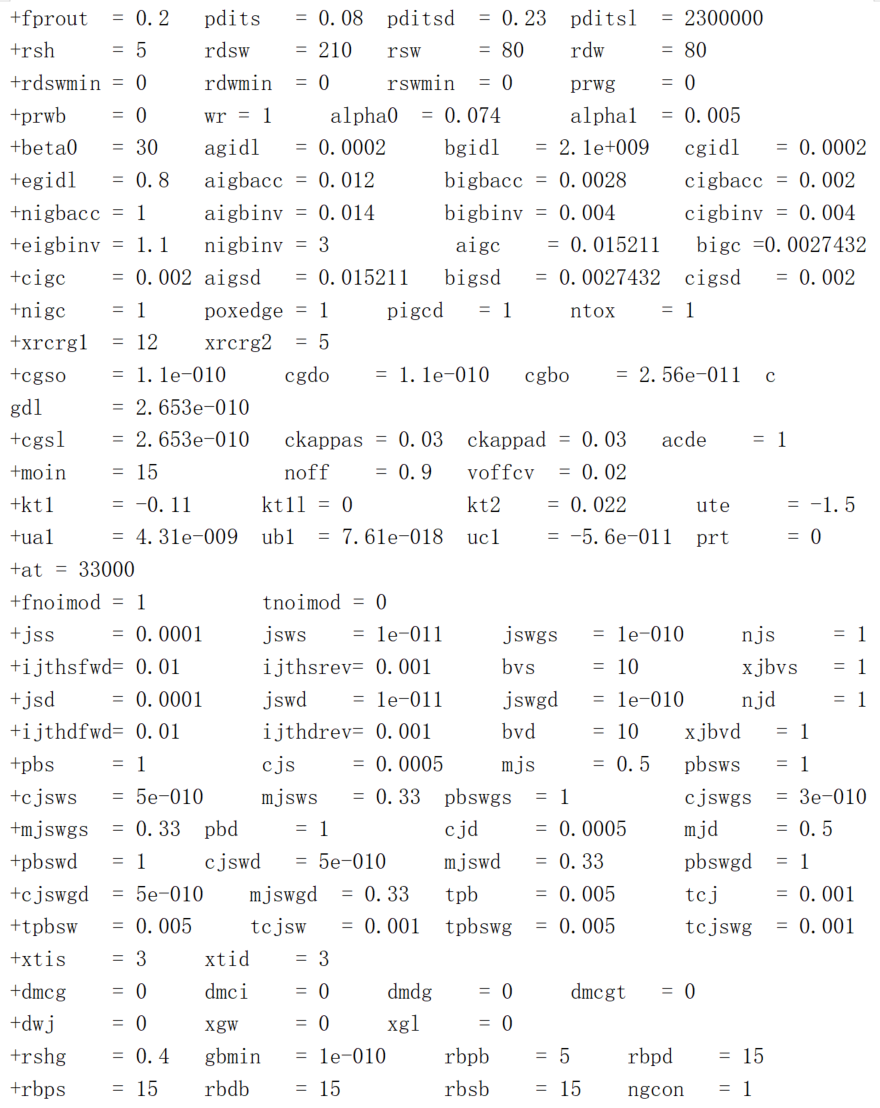

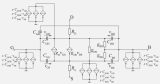

重點來啦! 下圖是一個BSIM4模型的例子,可與上期的BSIM3模型相對比(http://bwrcs.eecs.berkeley.edu/Classes/icdesign/ee241_s13/Assignments/45nm_LP.pm)。

參考文獻

[1] 伍青青等,《MoSFET集約模型的發展》,固體電子學研究與進展,2010

[2] William Liu,MOSFET MODELS FOR SPICE SIMULATION, INCLUDING BSIM3v3 AND BSIM4, Wiely,2001

-

芯片

+關注

關注

453文章

50406瀏覽量

421843 -

模型

+關注

關注

1文章

3172瀏覽量

48714 -

漏電流

+關注

關注

0文章

260瀏覽量

16996

原文標題:EDA探索丨第18期:BSIM4模型

文章出處:【微信號:hzwtech,微信公眾號:鴻之微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何用DC掃描提取BSIM3電容?

如何在ADS中添加晶體管的spice模型

概倫電子通用并行電路仿真器NanoSpice?介紹

業界領先的半導體器件SPICE建模平臺介紹

PDK 驗證軟件PQLab的優勢和技術指標

MOSFET的建模與BSIM3用戶指南

盤古大模型和ChatGPT4的區別

在SPICE模擬器中應該調諧優化哪些模型參數?需要全部調優嗎?

BSIM4模型與BSIM3模型的區別

BSIM4模型與BSIM3模型的區別

評論