本篇繼續介紹數電第二章——門電路的相關內容。本章雖然個人感覺重要程度不如之后的幾章,但是也是相當重要的一部分,并且學習起來有一定的困難,因此需要對于一些重點部分進行適當的重視。

1考點總結

1.分析所給TTL電路的邏輯(真值表和邏輯式)

2.計算TTL門電路的扇出系數

3.OC門負載電阻的計算

4.分析所給的CMOS電路的邏輯(真值表和邏輯式)

2各考點分析

首先這些電路都是不需要會畫的,會分析就行,因此在復習的時候不要花大把的時間去記憶電路圖,熟悉熟悉就可以,重點在于分析。

1.TTL門電路

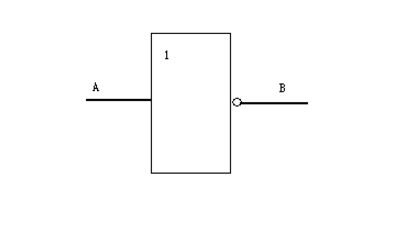

①TTL反相器

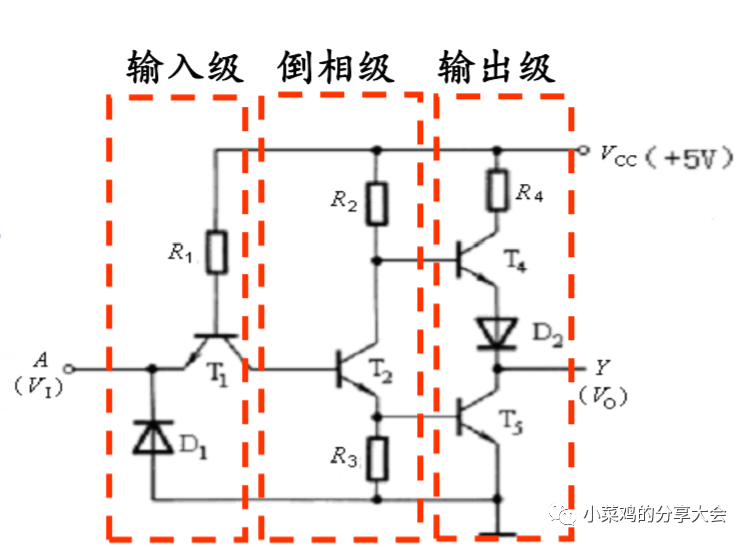

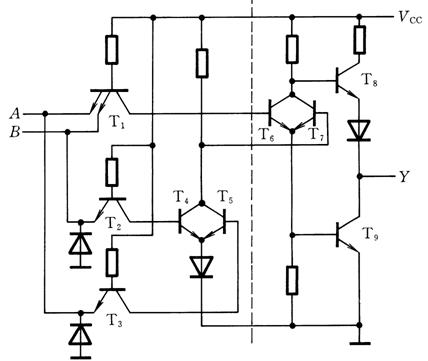

電路如圖分為輸入、倒向、輸出三級。后兩級都是我們在模電中就已經熟知的結構,在這里不再贅述。輸入級的D1管的作用就是保護,對電路本身沒有太大影響。我們在這里給定一定的條件,借以分析。

設:VCC=5VVIL=0.2V,VIH=3.4V,VON=0.7V,R1=4kΩ。(注意這里的VCC=5V,所有的TTL電路的VCC都必須是5V.另外R1=4KΩ也是一個定制,在TTL反相器中一般不改變。)

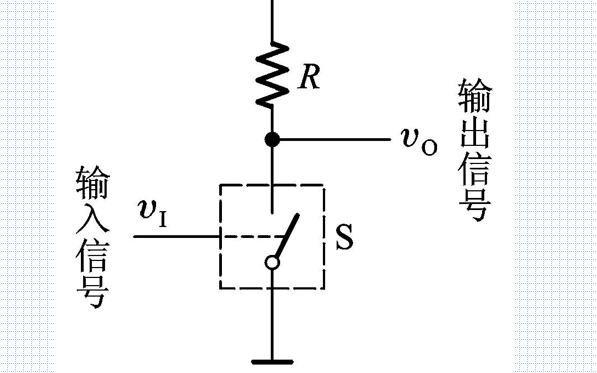

所謂的邏輯分析,就是畫真值表,給定輸入的高低電平所有情況,觀 察對應的輸出,并寫出邏輯表達式的過程。因此我們分輸入的高低電平兩種情況討論:

1>VI=0.2V。

此時的T1管必定導通,因此Vb1被鉗位在0.9V.觀察c1和b2,這兩個電流從理論上講應當是相反的,因此都等于零。從而可以算出ib1=ie1≈1mA。而Ibs≈0,進而滿足了ib1>>Ibs這一深度飽和條件。我們知道深度飽和的條件下,VE=VES<0.3V,這里我們取0.1V,顯然T2管是截止的,那么R2是沒有大電流流過的,可以認為Vb4處于高電平狀態,同理Vb5處于低電平狀態,即T4導通,T5截止,Y處于高電平狀態。

2>VI=3.4V。

這一情況請讀者自行依照上文分析,最后可以得到Y處于低電平狀態。

綜合上述畫出真值表,寫出邏輯表達式:

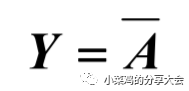

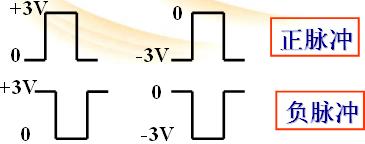

這里必須提到的一點還有TTL反相器的輸入伏安特性曲線,如下圖。請讀者記住圖中對應高低電平下的輸入電流值,在與非門和或非門的電路分析中需要使用到。

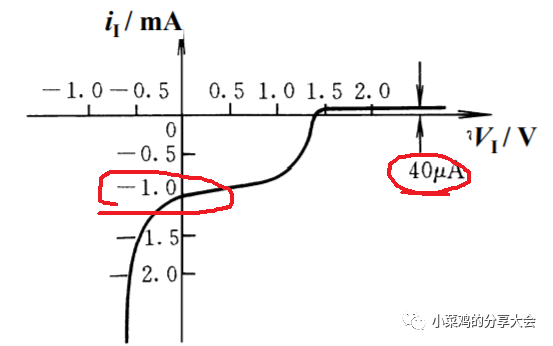

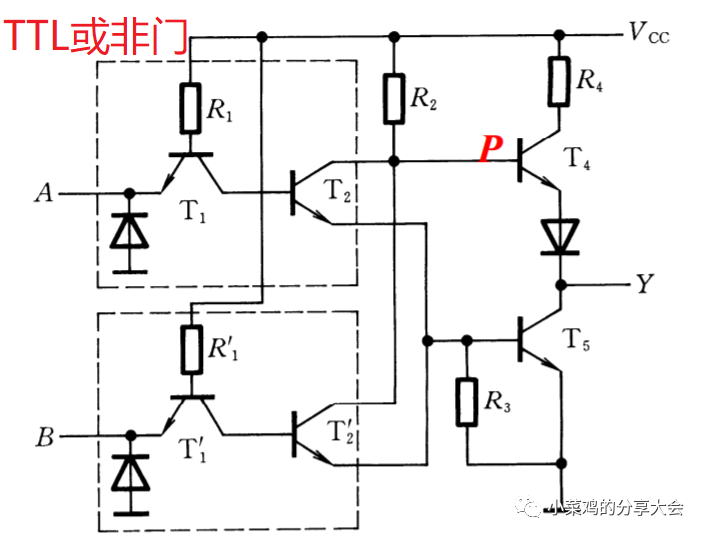

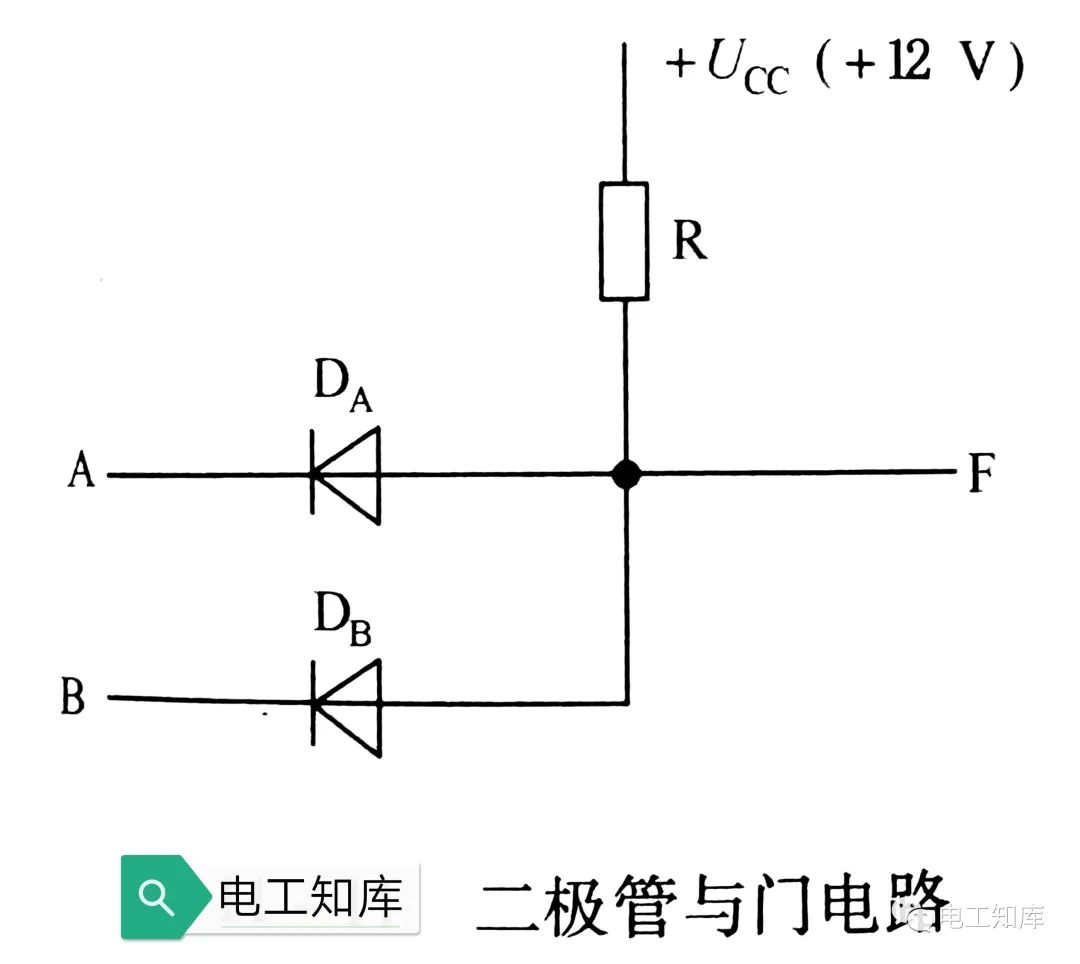

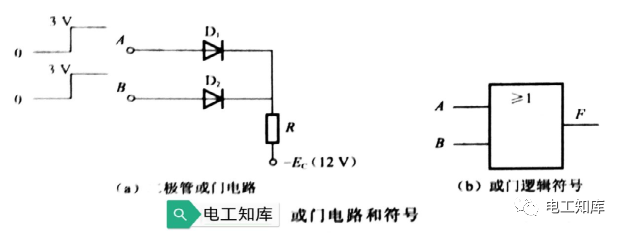

②TTL與非門和或非門

電路圖如下:

由于TTL電路的分析過程大同小異,這里就不再做過多的敘述,值得注意的一點是TTL與非門輸入級的雙輸入端結構。這個結構導致與非門在低電平時雖然有兩個輸入端,但是輸入電流依然只有-1mA,而高電平時要按照兩個計算,為40*2=80uA。另外在其他計算中,請一定要格外注意與非門和或非門的多輸入端結構導致的電流加倍問題,題設一般給的都是一端輸入的電流要求。

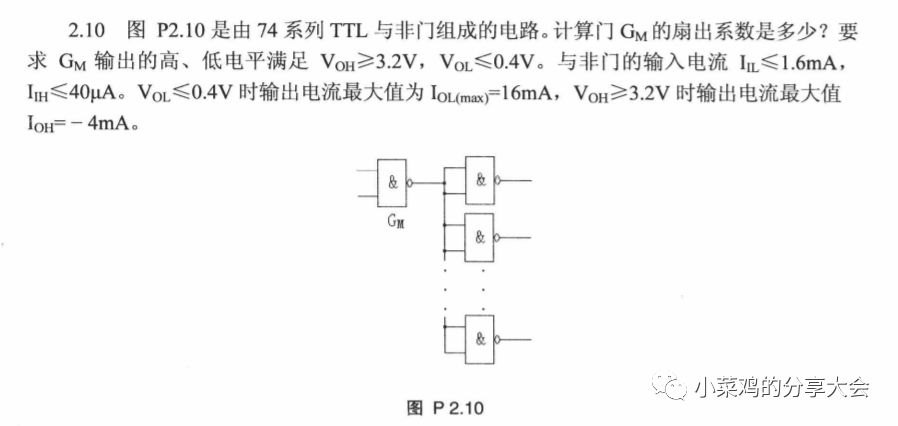

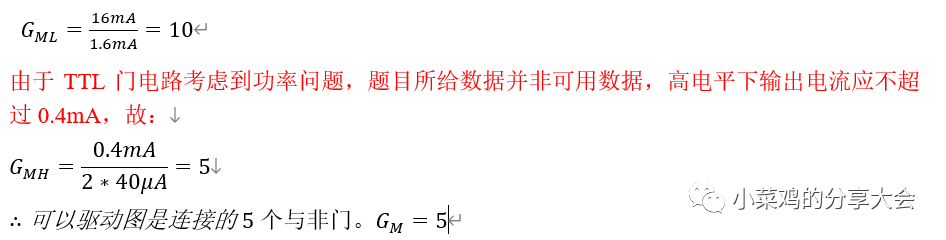

2.TTL門電路的扇出系數計算

扇出系數的定義是:一個TTL門電路可以帶動相同門電路的數目。一般是指電流的允許值。這里給出一道例題借以講述:

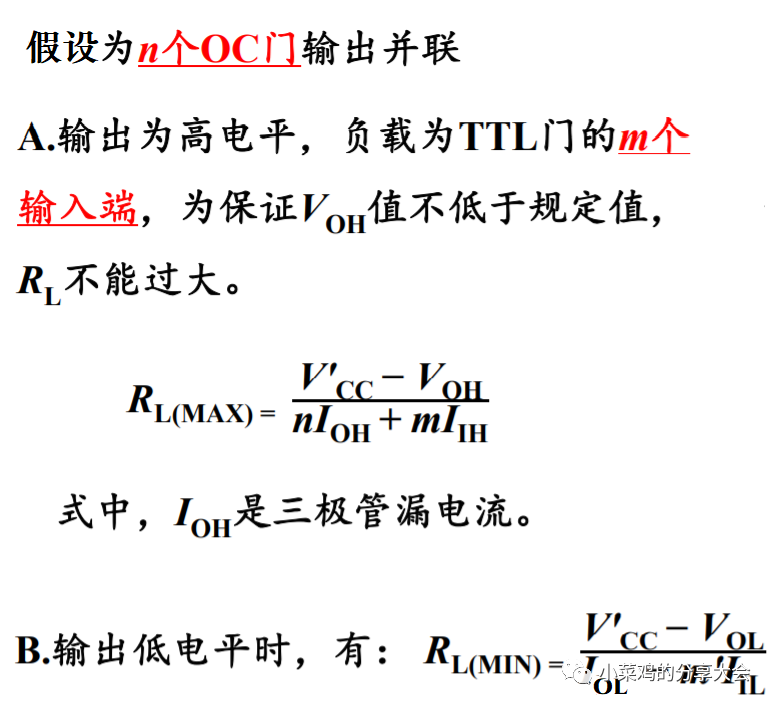

3.OC門負載電阻的計算

OC門即為集電極開路門電路,是為了實現“線與”這個邏輯而存在的一種電路,只要把幾個OC門的輸出Y直接用導線連在一起,就可以得到這幾個輸出的“與”邏輯,但是OC門對于負載電阻RL有著嚴格的要求:

這里需要特別注意,針對與非門,m為輸入端數,m'為負載門數;針對或非門,m和m'都是輸入端數,這是上文提到的與非門輸入電流問題導致的。

4.CMOS集成門電路

CMOS門電路相較于TTL電路簡便許多,并且不會存在溫漂等問題,分析起來要簡單的多,因此實際電路設計中,TTL電路已經逐步被CMOS工藝所替代。由于過于簡單,CMOS電路的分析請讀者自行學習,這里強調的一點是,請一定要注意COMS電路中NMOS和PMOS的上下位置關系不要顛倒,以及N和P型的電壓導通情況不要搞混。

-

CMOS

+關注

關注

58文章

5689瀏覽量

235171 -

電路圖

+關注

關注

10325文章

10718瀏覽量

528379 -

TTL

+關注

關注

7文章

502瀏覽量

70147 -

反相器

+關注

關注

6文章

310瀏覽量

43251 -

門電路

+關注

關注

7文章

199瀏覽量

40127

發布評論請先 登錄

相關推薦

與門電路、或門電路、非門電路及實例

什么是門電路 門電路是什么意思

基本邏輯門電路

門電路作用是什么_門電路有幾種電路

門電路的相關知識

門電路的相關知識

評論