1.關(guān)于AXI協(xié)議

AMBA AXI協(xié)議支持高性能、高頻系統(tǒng)設(shè)計(jì)。

AXI協(xié)議:

?適用于高帶寬和低延遲的設(shè)計(jì);

?提供高頻操作,無(wú)需使用復(fù)雜的連線橋接;

?滿足多器件的接口要求;

?適用于具有高初始訪問(wèn)延遲的內(nèi)存控制器;

?提供靈活的互連架構(gòu);

?向后兼容現(xiàn)有的AHB和APB接口。

AXI協(xié)議的主要特性是:

?獨(dú)立的地址/控制和數(shù)據(jù)階段

?使用字節(jié)控制支持不對(duì)齊的數(shù)據(jù)傳輸;

?使用基于突發(fā)的傳輸(burst),只需要發(fā)出起始地址;

?獨(dú)立的讀和寫(xiě)數(shù)據(jù)通道,可以提供低成本的直接內(nèi)存訪問(wèn)(DMA);

?支持發(fā)出多個(gè)傳輸?shù)刂罚?/p>

?支持亂序傳輸;

?允許輕松添加配置階段,以提供定時(shí)關(guān)斷(AXI支持低功耗擴(kuò)展模式)。

2.AXI 架構(gòu)

AXI協(xié)議是基于突發(fā)傳輸?shù)模╞urst-based),并定義了以下獨(dú)立的傳輸通道:

?讀取地址傳輸通道

?讀取數(shù)據(jù)傳輸通道

?寫(xiě)地址傳輸通道

?寫(xiě)入數(shù)據(jù)傳輸通道

?寫(xiě)響應(yīng)傳輸通道

地址通道攜帶描述要傳輸?shù)臄?shù)據(jù)性質(zhì)的控制信息。 數(shù)據(jù)在主從之間通過(guò)以下方式傳輸:

?寫(xiě)數(shù)據(jù)通道,用于將數(shù)據(jù)從主端傳輸?shù)綇亩恕?在寫(xiě)事務(wù)中,從端使用寫(xiě)響應(yīng)通道向主機(jī)發(fā)送完成傳輸?shù)?a target="_blank">信號(hào)。

?讀取數(shù)據(jù)通道,將數(shù)據(jù)從從端傳輸?shù)街鳈C(jī)。

AXI協(xié)議:

?允許在實(shí)際數(shù)據(jù)傳輸之前發(fā)出地址信息;

?支持多個(gè)未完成的傳輸事務(wù);

?支持亂序傳輸。

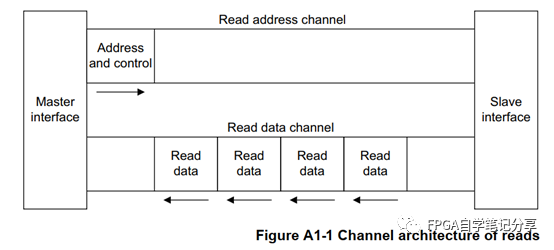

讀傳輸使用讀地址和讀數(shù)據(jù)通道進(jìn)行讀操作的過(guò)程如下圖所示:

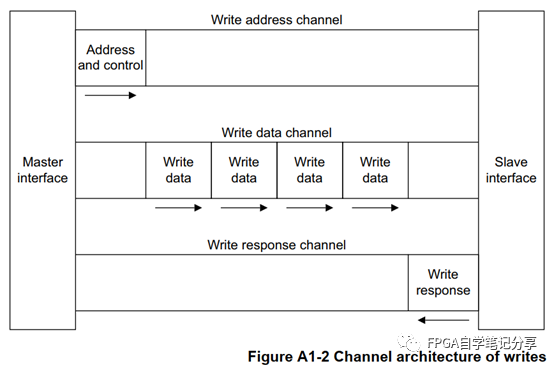

寫(xiě)傳輸使用寫(xiě)地址、寫(xiě)數(shù)據(jù)通道和響應(yīng)通道進(jìn)行讀操作的過(guò)程如下圖所示:

信息源端使用VALID信號(hào)來(lái)顯示通道上何時(shí)有有效地址、數(shù)據(jù)或控制信息可用。 目的端使用READY信號(hào)來(lái)顯示它何時(shí)可以接受信息。 讀數(shù)據(jù)通道和寫(xiě)數(shù)據(jù)通道都包括一個(gè)LAST信號(hào),以指示事務(wù)中最終數(shù)據(jù)項(xiàng)的傳輸。

讀和寫(xiě)地址通道:

讀寫(xiě)傳輸都有自己的地址通道。 適當(dāng)?shù)牡刂吠ǖ罃y帶傳輸所需的所有地址和控制信息。

讀數(shù)據(jù)通道:

讀數(shù)據(jù)通道攜帶從端到主端的讀數(shù)據(jù)和讀響應(yīng)信息,包括:

?數(shù)據(jù)總線,可以是8、16、32、64、128、256、512或1024位寬;

?一個(gè)讀響應(yīng)信號(hào),指示讀事務(wù)的完成狀態(tài)。

寫(xiě)數(shù)據(jù)通道:

寫(xiě)數(shù)據(jù)通道攜帶從主機(jī)到從主機(jī)的寫(xiě)數(shù)據(jù),包括:

?數(shù)據(jù)總線,可以是8、16、32、64、128、256、512或1024位寬;

?字節(jié)有效信號(hào)為每8個(gè)數(shù)據(jù)位,表明哪些字節(jié)的數(shù)據(jù)是有效的。

寫(xiě)數(shù)據(jù)通道信息總是被視為緩沖的,這樣主端就可以執(zhí)行寫(xiě)傳輸,而不需要等待從端確認(rèn)。

寫(xiě)響應(yīng)信道:

從端使用寫(xiě)響應(yīng)通道來(lái)響應(yīng)寫(xiě)傳輸。所有寫(xiě)傳輸都需要在寫(xiě)響應(yīng)通道上發(fā)出完成信號(hào)。寫(xiě)傳輸完成時(shí),寫(xiě)響應(yīng)只對(duì)一個(gè)完全的傳輸發(fā)出響應(yīng)信號(hào),而不是對(duì)傳輸中的每個(gè)數(shù)據(jù)傳輸發(fā)出響應(yīng)信號(hào)。

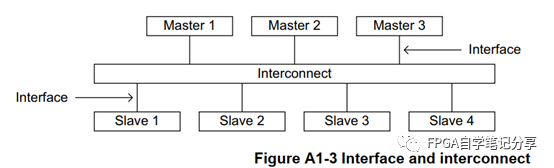

3.AXI總線的互聯(lián):

AXI協(xié)議提供了一個(gè)單獨(dú)的接口定義,用于以下接口:

主機(jī)和互聯(lián)接口之間的連接;

從機(jī)和互連接口之間的連接;

主機(jī)和從機(jī)之間連接;

AXI的連接接口如下:

AXI的拓?fù)浣Y(jié)構(gòu),大多數(shù)系統(tǒng)使用AXI以下三種互連拓?fù)渲?

?共享地址和數(shù)據(jù)總線;

?共享地址總線和多個(gè)數(shù)據(jù)總線;

?多層,具有多個(gè)地址和數(shù)據(jù)總線;

在大多數(shù)系統(tǒng)中,地址通道帶寬需求明顯小于數(shù)據(jù)通道帶寬需求。這樣的系統(tǒng)可以通過(guò)使用多個(gè)數(shù)據(jù)總線的共享地址總線來(lái)實(shí)現(xiàn)并行數(shù)據(jù)傳輸,從而在系統(tǒng)性能和互連復(fù)雜性之間實(shí)現(xiàn)良好的平衡。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21665瀏覽量

601828 -

接口

+關(guān)注

關(guān)注

33文章

8497瀏覽量

150834 -

總線

+關(guān)注

關(guān)注

10文章

2866瀏覽量

87985 -

AMBA

+關(guān)注

關(guān)注

0文章

68瀏覽量

14951 -

AXI

+關(guān)注

關(guān)注

1文章

127瀏覽量

16598

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

看看在SpinalHDL中AXI4總線互聯(lián)IP的設(shè)計(jì)

SoC Designer AXI4協(xié)議包的用戶(hù)指南

AMBA 4 AXI4、AXI4-Lite和AXI4-流協(xié)議斷言用戶(hù)指南

AXI4接口協(xié)議的基礎(chǔ)知識(shí)

一文詳解ZYNQ中的DMA與AXI4總線

深入AXI4總線一握手機(jī)制

AXI4 、 AXI4-Lite 、AXI4-Stream接口

AXI3與AXI4寫(xiě)響應(yīng)的依賴(lài)區(qū)別?

AXI4協(xié)議五個(gè)不同通道的握手機(jī)制

FPGA AXI4協(xié)議學(xué)習(xí)筆記(二)

FPGA AXI4協(xié)議學(xué)習(xí)筆記(三)

AXI4-Lite協(xié)議簡(jiǎn)明學(xué)習(xí)筆記

Xilinx FPGA AXI4總線(一)介紹【AXI4】【AXI4-Lite】【AXI-Stream】

漫談AMBA總線-AXI4協(xié)議的基本介紹

AMBA AXI4接口協(xié)議概述

FPGA AXI4協(xié)議學(xué)習(xí)筆記(一)

FPGA AXI4協(xié)議學(xué)習(xí)筆記(一)

評(píng)論