雖然減少工藝節點在電路密度和提高計算能力方面帶來了巨大的好處,但也有一個相關的缺點——增加設計可變性。這種可變性源于對裕量的需求,即工程師為提高設計穩健性和降低流片風險而引入的規范保護帶。規格設置得越嚴格,失敗的風險就越大,從而影響最終成本。設計人員需要新的工具來有效且高效地最大限度地減少他們指定的過多設計裕量,從而降低成本和風險。

這篇由兩部分組成的文章的第一部分將探討設計人員在開發針對節能設計的 SoC 時面臨的問題,以及 Synopsys 的 PrimeShield? 技術如何幫助優化低功耗設計,同時實現積極的上市時間目標。

現實

長期以來,半導體一直根據最壞情況的工藝、電壓和溫度(PVT)進行指定。在設計階段,設計人員必須平衡性能與功耗和面積(PPA),努力實現所需的每瓦性能目標。為了評估可變性對電路性能的影響,設計人員采用靜態時序分析(STA)來評估每個時序路徑。由于影響PPA的因素很多,設計人員經常執行SPICE仿真以獲得更準確的結果。

然而,隨著工藝節點的進步和電路密度的增加,上市時間的壓力也越來越大。結果是,設計團隊可以執行預簽核的魯棒性分析量有限,導致過度悲觀(增加設計裕量以確保達到性能和功耗目標)。在設計和制造中,不言而喻的是,越早發現錯誤或進行優化,影響就越低——魯棒性改進也不例外。

這種過度設計的最終結果是魯棒性降低,直接影響最終產品PPA、上市時間和材料成本——所有這些因素都可能使半導體供應商在市場上失去競爭力。需要一種強大的統計魯棒性分析工具,該工具可以在設計周期的早期應用,并幫助提高設計對變化的抗擾度。

進入總理盾

蒙特卡洛類固醇

雖然蒙特卡洛SPICE仿真一直是電路分析的黃金標準,但它無法適應當今的電路密度。就其本質而言,蒙特卡羅模擬必須重復相同的分析數千次甚至數百萬次才能獲得高西格瑪精度,因此僅適用于數十個細胞。

PrimeShield 利用 Synopsys 的 PrimeTime? 黃金簽核引擎,在幾秒鐘內執行 SPICE 精確的時序計算和變化建模。為了實現所需的吞吐量,PrimeShield利用蒙特卡洛分析的重復性,并使用獲得專利的機器學習技術來大大提高分析性能。結果是分析通量提高了 100 到 10,000 倍,在幾分鐘內對具有數十億個細胞的大規模 SoC 中的關鍵時序路徑執行統計仿真,而不是傳統統計仿真所需的數天或數周。

用于低功耗設計的PrimeShield

PrimeTime引入了先進的電壓調節技術,使設計人員能夠在廣泛的范圍內對任何電壓電平進行準確分析。設計人員現在有一種方法可以掃描電壓范圍,在不同的電壓電平下試運行相同的設計,并最終找到所需的PPA或每瓦性能目標的電壓最佳點。雖然 PrimeTime 解決方案已被證明既準確又有效,但掃描過程既耗時又耗費資源。

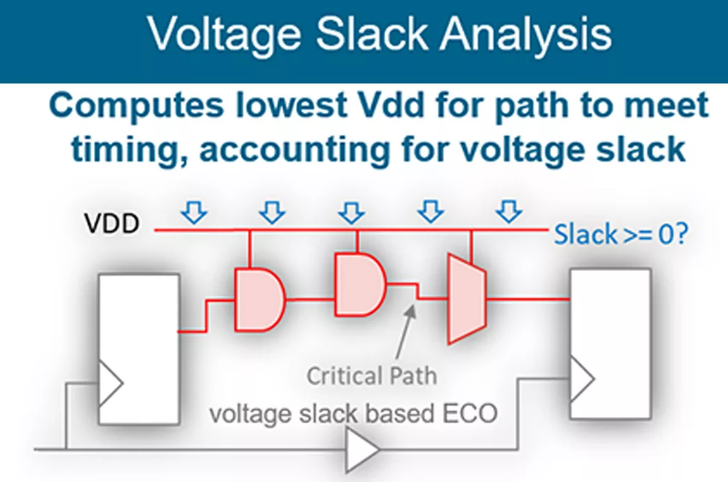

PrimeShield擴展了PrimeTime核心技術,并引入了一種新的PPA簽核分析類型,稱為電壓松弛,它表示設計滿足性能要求的每個單元或每個路徑的最低電壓。這種簽核分析使設計人員能夠有效地查明電壓瓶頸,以提高IR壓降魯棒性,提高電壓裕量均勻性,并發現直接微調工作電壓的機會。可變電壓現在可用作 PPA 優化指標。

電壓松弛的大小決定了路徑對電壓變化的敏感性。具有小電壓松弛的路徑被認為是工作電壓關鍵型的。PrimeShield優先考慮具有較小電壓緩沖的固定路徑,以提高設計對IR壓降的彈性。它還通過降低工作電壓或通過提高工作電壓來提升頻率,從而實現節能。此外,PrimeShield支持基于電壓松弛的優化,并且已被發現對混合V非常有益。T設計。

動態或開關電源已成為功耗優化的重中之重,尤其是對于高級節點 HPC 應用。雖然降低工作電壓可以直接降低動態功耗,但工作電壓長期以來一直是設計流程中的靜態指標。高級節點上更高的電池和功率密度也使得降低電壓供應水平成為一項極其困難的任務。盡管如此,較低的電壓水平對于實現有競爭力的每瓦性能目標至關重要。因此,一個新的購電協議權力機會出現了。

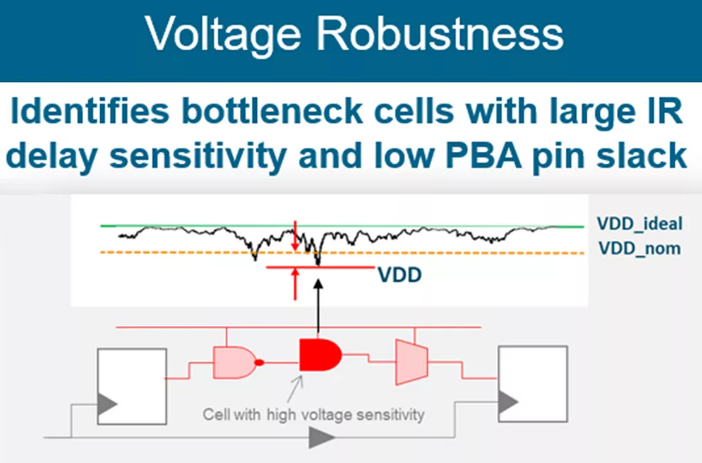

功率與電壓有關,但降低工作電壓會影響性能。PrimeShield 計算每條路徑滿足時序要求的最低工作電壓,準確考慮電壓松弛。利用這些數據,PrimeShield執行電壓魯棒性分析,以識別具有大IR壓降靈敏度和引腳松弛不足的瓶頸電池。因此,設計人員可以對設計進行微調,以實現最低的工作電壓,同時達到性能目標。

因此,PrimeShield電壓松弛和魯棒性分析使用戶能夠提高超低功耗設計中對電壓變化的設計彈性,并進一步節省功耗以獲得最佳能效。

審核編輯:郭婷

-

半導體

+關注

關注

334文章

27019瀏覽量

216347 -

仿真

+關注

關注

50文章

4044瀏覽量

133420 -

SPICE

+關注

關注

6文章

181瀏覽量

42517

發布評論請先 登錄

相關推薦

面對不斷增加的設計可變性,提高穩健性并最大限度地減少過度悲觀情緒

面對不斷增加的設計可變性,提高穩健性并最大限度地減少過度悲觀情緒

評論